ADC12DJ3200器件是一款射頻采樣、千兆采樣、模數轉換器 (ADC),可直接對從 DC 到 10 GHz 以上的輸入頻率進行采樣。在雙通道模式下,ADC12DJ3200可以采樣高達 3200 MSPS,在單通道模式下可以采樣高達 6400 MSPS。通道數(雙通道模式)和奈奎斯特帶寬(單通道模式)的可編程權衡允許開發靈活的硬件,以滿足高通道數或寬瞬時信號帶寬應用的需求。8.0 GHz 的全功率輸入帶寬 (–3 dB),在雙通道和單通道模式下的可用頻率都超過 –3 dB 點,允許對 L 波段、S 波段、C 波段和 X 波段進行直接射頻采樣,適用于頻率捷變系統。

*附件:adc12dj3200.pdf

該ADC12DJ3200使用高速JESD204B輸出接口,具有多達 16 個串行通道和子類 1 合規性,可實現確定性延遲和多設備同步。串行輸出通道支持高達 12.8 Gbps,并可配置為權衡比特率和通道數。創新的同步功能,包括無噪聲孔徑延遲(T 廣告 )調整和SYSREF窗口,簡化相控陣雷達和MIMO通信的系統設計。雙通道模式下的可選數字下變頻器(DDC)可降低接口速率(實抽取模式和復抽取模式)和信號的數字混合(僅限復抽取模式)。

特性

- ADC內核:

- 12 位分辨率

- 單通道模式下高達 6.4 GSPS

- 雙通道模式下高達 3.2 GSPS

- 性能規格:

- 本底噪聲(無信號,V

司 司長= 1.0 伏PP-差分器):- 雙通道模式:–151.8 dBFS/Hz

- 單通道模式:–154.6 dBFS/Hz

- HD2、HD3:–65 dBc,最高 3 GHz

- 本底噪聲(無信號,V

- 帶 V 的緩沖模擬輸入

CMI的0 V 的:- 模擬輸入帶寬 (–3 dB):8.0 GHz

- 可用輸入頻率范圍:>10 GHz

- 滿量程輸入電壓 (V

司 司長,默認):0.8 V聚丙烯 - 模擬輸入共模 (V

ICM的):0 伏

- 無噪聲孔徑延遲 (T

廣告)調整:- 精確采樣控制:19-fs 步長

- 簡化同步和交錯

- 溫度和電壓不變延遲

- 易于使用的同步功能:

- 自動 SYSREF 定時校準

- 樣品標記的時間戳

- JESD204B串行數據接口:

- 支持子類 0 和 1

- 最大通道速率:12.8 Gbps

- 多達 16 個通道可降低通道速率

- 雙通道模式下的數字下變頻器:

- 實際輸出:DDC 旁路或 2 倍抽取

- 復數輸出:4 倍、8 倍或 16 倍抽取

- 每個DDC有四個獨立的32位NCO

- 功耗:3 W

- 電源:1.1 V、1.9 V

參數

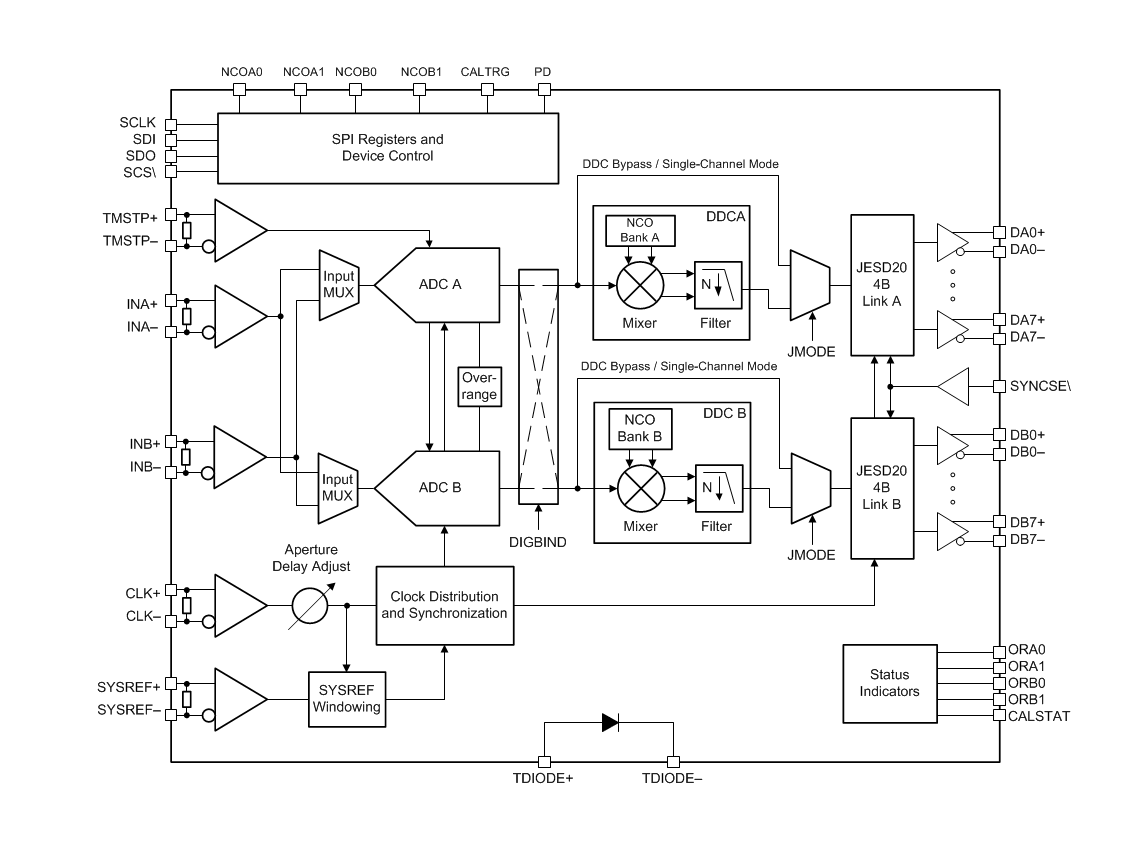

方框圖

ADC12DJ3200 是德州儀器推出的高速 RF 采樣模數轉換器(ADC),支持單通道最高 6.4 GSPS、雙通道最高 3.2 GSPS 采樣率,12 位分辨率,具備寬輸入帶寬、高抗干擾性與靈活同步特性,專為高頻通信、雷達、測試測量等場景設計,文檔版本為 SLVSD97A(2017 年 6 月首次發布,2020 年 4 月修訂)。

一、產品基礎信息

- 核心定位 :RF 采樣架構,可直接采樣 DC 至 10 GHz 以上頻率信號,支持 L 波段、S 波段、C 波段、X 波段直接采樣;通過可編程通道數與 Nyquist 帶寬,適配高通道數或寬瞬時帶寬需求。

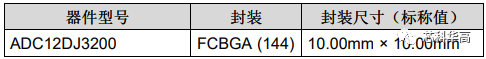

- 引腳與封裝 :采用 144 引腳 FCBGA 封裝,尺寸 10.00mm×10.00mm;包含雙路模擬輸入(INA±/INB±)、時鐘輸入(CLK±)、同步參考輸入(SYSREF±)、16 路高速串行數據輸出(DA0-7±/DB0-7±)及 SPI 配置接口。

二、核心特性與參數

(一)采樣與精度性能

- 采樣速率 :單通道模式 6.4 GSPS,雙通道模式 3.2 GSPS;輸入時鐘頻率范圍 800 MHz - 3200 MHz,單通道模式支持雙沿采樣(DES)。

- 精度指標 :差分非線性(DNL)±0.3 LSB,積分非線性(INL)±2.5 LSB;噪聲基底單通道模式 -154.6 dBFS/Hz,雙通道模式 -151.8 dBFS/Hz;總諧波失真(THD)低至 -65 dBc(3 GHz 以下),無雜散動態范圍(SFDR)最高達 100 dB。

- 輸入特性 :模擬輸入帶寬(-3 dB)8.0 GHz,可用頻率 >10 GHz;差分輸入滿量程電壓默認 0.8 VPP,可通過寄存器調整(480 mVPP - 1040 mVPP);共模輸入電壓 0 V,共模瞬態抗擾度(CMTI)典型值 100 kV/μs。

(二)隔離與可靠性

- 安全特性:爬電距離與電氣間隙均滿足高頻應用要求,ESD 防護達 ±2500 V(HBM)/±1000 V(CDM),工作結溫最高 150°C,存儲溫度 -65°C 至 150°C。

- 熱性能:結到環境熱阻(RθJA)25.3 °C/W,結到板熱阻(RθJB)8.2 °C/W,暴露熱焊盤需焊接至 PCB 優化散熱。

(三)電源與功耗

- 供電范圍:模擬電源(VA19)1.8 V - 2.0 V,模擬電源(VA11)1.05 V - 1.15 V,數字電源(VD11)1.05 V - 1.15 V。

- 功耗表現:典型功耗 3 W(單通道模式,JMODE=1),不同工作模式功耗范圍 2.9 W - 3.8 W,支持低功耗背景校準模式降低平均功耗。

三、關鍵功能模塊

(一)信號鏈與調制傳輸

- ADC 核心 :采用 6 個 ADC 子核交錯架構,支持前景校準(離線)與背景校準(在線),可修正增益、偏移與線性誤差,保障寬溫下性能穩定。

- 數字下變頻器(DDC) :雙通道模式專屬,支持 2 倍(實輸出)、4/8/16 倍(復輸出)抽取;每通道含 4 個獨立 32 位 NCO,支持快速跳頻與相位相干,可降低接口速率并實現信號混頻至基帶。

- JESD204B 接口 :支持子類 0/1,最高 16 路串行 lanes,單 lane 速率達 12.8 Gbps;子類 1 支持確定性延遲與多器件同步,適配高集成度系統。

(二)同步與校準功能

- 同步特性 :支持無噪聲孔徑延遲調整(19 fs 步長),簡化多 ADC 同步與交錯;SYSREF 時序自動校準、時間戳標記功能,配合 SYSREF 窗口 ing 技術,降低同步時序約束。

- 校準模式 :前景校準需設備離線,背景校準通過備用 ADC 核輪換實現無中斷校準;支持偏移濾波、輸入阻抗微調、增益校準,可補償溫度與電壓變化帶來的誤差。

(三)保護與狀態監測

- 過 range 檢測:可編程雙閾值(OVR_T0/OVR_T1),支持引腳輸出與數據嵌入標記,響應時間快,便于系統增益管理。

- 告警功能:監測串行器 PLL 鎖定狀態、JESD204B 鏈路狀態、NCO 與時鐘異常,通過 CALSTAT 引腳或寄存器輸出告警信息。

四、應用與設計要點

(一)典型應用場景

- 通信測試儀器(802.11ad、5G)、衛星通信(SATCOM)、相控陣雷達、電子情報(ELINT)/ 信號情報(SIGINT)、合成孔徑雷達(SAR)、激光雷達(LIDAR)、寬帶數字示波器與軟件無線電(SDR)。

(二)設計關鍵要點

- 電源與去耦 :模擬電源與數字電源需獨立供電,就近部署 0.1 μF 陶瓷電容 + 10 μF 鉭電容去耦,模擬地與數字地單點連接,減少噪聲耦合。

- 時鐘與同步 :推薦低抖動時鐘源(如 MEMS 時鐘或晶振),CLK±/SYSREF± 建議 AC 耦合,長距離布線需匹配 50 Ω 阻抗;多器件同步需保證 SYSREF 信號相位一致,Trace 長度匹配。

- 布局要求 :模擬輸入線路對稱布線,遠離數字信號路徑;隔離區域保留足夠爬電 / 電氣間隙,高速串行輸出 lanes 需控制阻抗與串擾。

五、封裝與訂購信息

- 封裝規格 :144 引腳 FCBGA(AAV 封裝),引腳鍍層符合 RoHS 標準,MSL 等級 3(260°C 峰值回流,168 小時暴露)。

- 訂購型號 :核心型號為 ADC12DJ3200(無后綴基礎型號),提供管裝與卷帶包裝選項,具體需參考完整訂購指南。

-

adc

+關注

關注

100文章

7796瀏覽量

556643 -

硬件

+關注

關注

12文章

3610瀏覽量

69105 -

模數轉換器

+關注

關注

26文章

4077瀏覽量

130217 -

射頻采樣

+關注

關注

0文章

56瀏覽量

4739 -

信號帶寬

+關注

關注

0文章

44瀏覽量

3510

發布評論請先 登錄

ADC12DJ3200器件異常發熱的原因?怎么解決?

ADC12DJ3200采樣諧波很大的原因?怎么解決?

ADC12DJ3200使用JMODE0的模式下,線速度如何計算?

ADC12DJ3200芯片采樣率最高是6.4GSPS,為什么可以采集10GHz(甚至12GHz)的信號呢?

請問ADC12DJ3200的lane rate怎么計算?

使用adc12dj3200做設計,該上電順序是必須要準守的嗎?

使用adc12dj3200做設計,可以使用差分運放嗎?

ADC12DJ3200的PSRR電源抑制是多少?

ADC12DJ3200EVM訂貨

請問ADC12DJ3200的SPI讀寫哪里出了問題?

一顆模數轉換器芯片(ADC12DJ3200)的結構原理及特性

ADC12DJ3200 技術文檔核心內容總結

ADC12DJ3200 技術文檔核心內容總結

評論