在當(dāng)今高速數(shù)字系統(tǒng)中,信號速率早已突破幾十 Gbps。隨著頻率上升、邊沿變快、時序裕度變小,信號鏈路的設(shè)計不再只是“連起來”這么簡單,而是一個完整的系統(tǒng)匹配工程。真正的高速鏈路,是芯片、PCB、極細(xì)同軸線束三者共同配合、精確匹配的結(jié)果。任何一個環(huán)節(jié)“掉鏈子”,信號完整性(SI)都會被破壞。

一、芯片端:信號的“源頭”必須受控

高速信號從芯片的 SerDes、FPGA 或 ASIC 輸出,是整個鏈路的起點。這個階段最核心的指標(biāo)是驅(qū)動能力與阻抗匹配。

1.1、驅(qū)動特性決定信號形態(tài):高速芯片的上升/下降時間已經(jīng)進(jìn)入皮秒級,意味著每一段傳輸路徑都必須被當(dāng)作“傳輸線”處理,否則反射與過沖不可避免。

1.2、阻抗匹配是基本原則:輸出端的阻抗若與后級傳輸線不一致(例如 50 Ω 單端或 100 Ω 差分),反射、振鈴、眼圖閉合等現(xiàn)象就會出現(xiàn),最終影響系統(tǒng)誤碼率。

1.3、回流路徑也要關(guān)注:芯片到 PCB 的過渡設(shè)計若地平面斷開或走線不連續(xù),會引入寄生電感與雜散電容,導(dǎo)致信號完整性下降。

換句話說,芯片端不僅要能“推得動”,還要能“推得穩(wěn)”。而這個“穩(wěn)”,取決于它與 PCB 和線束的匹配程度。

二、PCB 端:信號傳輸?shù)摹案咚俟贰?br />芯片輸出的信號,第一站就是 PCB。PCB 不只是載體,更是信號傳播的重要通道;要讓信號在板上傳輸無誤,關(guān)鍵在于“阻抗、走線、地平面”三點。

2.1、阻抗控制要精準(zhǔn):無論是微帶線、帶狀線還是差分對,必須保持穩(wěn)定阻抗。走線寬度、介質(zhì)厚度、間距、銅厚都要通過仿真精確控制。

2.2、走線設(shè)計要平滑:高速信號最怕突變。拐角、過孔、層跳都會引起反射,因此設(shè)計上要避免 90° 轉(zhuǎn)角、減少 via 數(shù)量,并保持層間參考平面連續(xù)。

2.3、接地結(jié)構(gòu)要完整:信號回流路徑應(yīng)短、連續(xù),避免形成環(huán)路。尤其在連接器或線束接口區(qū)域,地回流若中斷,將導(dǎo)致串?dāng)_與 EMI 問題。

在許多高速系統(tǒng)中,設(shè)計師甚至?xí)?PCB 與線束連接處使用“跳板結(jié)構(gòu)”(Paddle Card),用以平滑過渡,避免阻抗突變。這種細(xì)節(jié)優(yōu)化,往往決定整條鏈路的上限。

三、極細(xì)同軸線束:連接外部的“最后一公里”

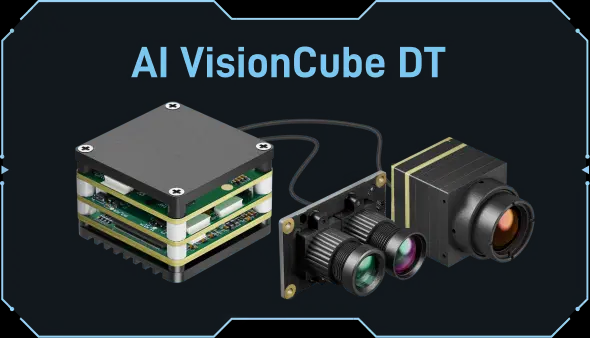

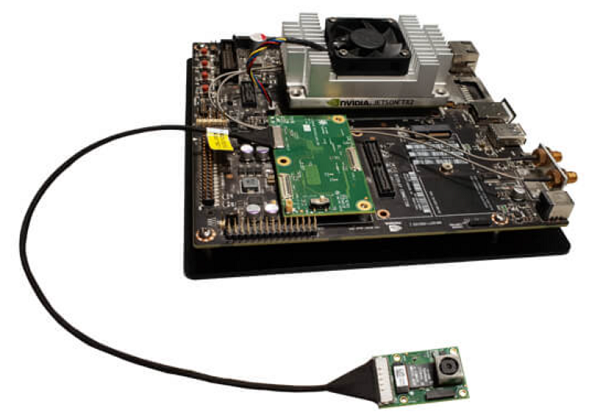

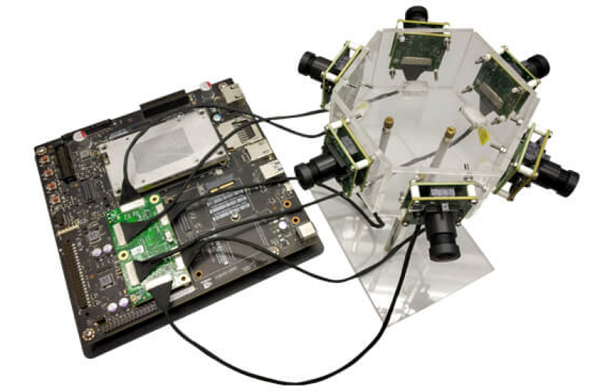

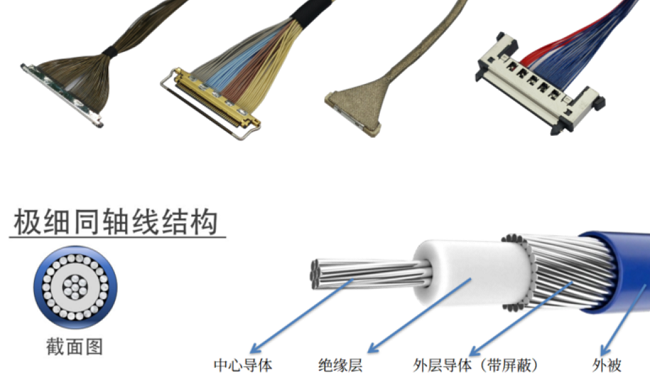

在系統(tǒng)中,極細(xì)同軸線束(Micro Coaxial Cable)往往用于芯片模塊與外部接口的高速連接,例如攝像頭模組、顯示接口、AI 計算模組之間。它的結(jié)構(gòu)與性能直接決定信號能否被完整送達(dá)。

3.1、結(jié)構(gòu)優(yōu)勢:

極高帶寬能力:micro coax 可支持幾十 GHz 頻率,遠(yuǎn)高于傳統(tǒng)電子線或排線。

優(yōu)異的屏蔽性能:同軸結(jié)構(gòu)的地層包圍信號線,回流路徑短,可有效抑制 EMI 與串?dāng)_。

體積極小,布線靈活:線徑常在 0.1 mm 左右,能在狹小空間中高密度布局,適用于筆記本、汽車電子、工業(yè)相機(jī)等領(lǐng)域。

3.2、設(shè)計匹配點:

阻抗一致性:典型為 50 Ω 單端或 100 Ω 差分,必須與 PCB、芯片輸出匹配,否則反射與損耗會明顯增加。

接口結(jié)構(gòu)優(yōu)化:在 PCB 連接處要避免信號路徑突變,通常采用高密度同軸連接器或跳板結(jié)構(gòu),讓信號過渡更平滑。

機(jī)械特性控制:線束彎曲半徑、扭轉(zhuǎn)強(qiáng)度、屏蔽完整性等,也會影響高頻性能。

可以說,極細(xì)同軸線束是高速信號的“延伸神經(jīng)”,它不僅傳遞信號,更是整個系統(tǒng)信號完整性鏈條的關(guān)鍵部分。

四、三者匹配的意義

一個優(yōu)秀的高速鏈路,必須滿足:源阻抗 = 傳輸線特性阻抗 = 負(fù)載阻抗;當(dāng)芯片、PCB、線束三者達(dá)到一致匹配時,信號可平滑傳輸,反射最小、眼圖開口最大、誤碼率最低;反之,只要某一環(huán)節(jié)失配,就會造成信號振鈴、串?dāng)_、時延不均、系統(tǒng)穩(wěn)定性下降等問題。這也是為什么高端設(shè)備在信號鏈設(shè)計上會采用全鏈路仿真(SI/PI Simulation),從芯片到連接器都進(jìn)行建模分析,確保系統(tǒng)級匹配。

五、設(shè)計實踐建議

5.1、在芯片選型階段,關(guān)注輸出驅(qū)動能力與阻抗特性,確保其適配目標(biāo)鏈路。

5.2、在 PCB 階段,保持走線阻抗恒定、參考平面連續(xù)、via 最少,尤其在接口區(qū)域需重點仿真。

5.3、在線束階段,選擇符合目標(biāo)速率的 micro coax 規(guī)格,注意屏蔽結(jié)構(gòu)、長度控制及機(jī)械約束。

5.4、在系統(tǒng)驗證階段,通過 TDR、S參數(shù)、眼圖測試等手段驗證鏈路連續(xù)性與信號質(zhì)量。

高速信號鏈路的性能,不取決于單一環(huán)節(jié),而是“芯片 + PCB + 極細(xì)同軸線束”三者的整體匹配;芯片是信號的源,PCB 是高速通道,線束是關(guān)鍵橋梁;三者只有協(xié)同優(yōu)化,才能實現(xiàn)高速、低誤碼、高可靠的傳輸系統(tǒng);任何一個環(huán)節(jié)忽視,都可能讓整個鏈路的性能大打折扣。

我是【蘇州匯成元電子科技】,長期致力于為工程師提供高性能極細(xì)同軸線束與高速連接方案,如果你也在探索高速鏈路設(shè)計的瓶頸與突破,歡迎在電子發(fā)燒友社區(qū)與我們交流更多實踐經(jīng)驗!

-

線束

+關(guān)注

關(guān)注

8文章

1131瀏覽量

26898 -

線束設(shè)計

+關(guān)注

關(guān)注

0文章

76瀏覽量

10098 -

信號線束

+關(guān)注

關(guān)注

0文章

71瀏覽量

1620

發(fā)布評論請先 登錄

極細(xì)同軸線束(micro coaxial cable)常見的使用場景有哪些?

極細(xì)同軸線束能否傳輸電源?設(shè)計中的應(yīng)用邊界解析

極細(xì)同軸線束到底是什么?一文帶你入門

極細(xì)同軸線束如何解決AI設(shè)備的高速信號傳輸難題?

極細(xì)同軸線與傳統(tǒng)射頻同軸線區(qū)別有哪些?

小體積、大帶寬:極細(xì)同軸線束如何兼顧高速與可靠性?

極細(xì)同軸線束在 HDMI 高速信號傳輸中的應(yīng)用與全解析

極細(xì)同軸線束如何助力 MIPI 高速信號實現(xiàn)低損高穩(wěn)傳輸?

極細(xì)同軸線束在 CoaXPress 高速圖像傳輸系統(tǒng)中的應(yīng)用與設(shè)計要點

極細(xì)同軸線束在Jetson攝像頭高速傳輸中的結(jié)構(gòu)與設(shè)計要點

極細(xì)同軸線束如何決定 USB 3.2 的真實傳輸速度?

極細(xì)同軸線束如何保障高速信號完整性?深度解析設(shè)計要點

為什么高速信號鏈路 = 芯片 + PCB + 極細(xì)同軸線束三者匹配?

為什么高速信號鏈路 = 芯片 + PCB + 極細(xì)同軸線束三者匹配?

評論