LDO基礎知識

低壓差線性穩壓器(以下簡稱LDO)是一種半導體器件,是在輸入與輸出的電壓差較小的狀態下也能工作的線性穩壓器的統稱。LDO的特點是即使輸入與輸出電壓差很小仍能獲得穩定的輸出,因此被廣泛應用于電池驅動的移動設備以及注重低功耗和小型化的應用場景中。具體而言,在直接由鋰離子電池驅動電路時采用LDO就是一個典型的案例。

本文我們將介紹LDO的工作原理與電路結構、設計時應考慮的規范和特性等內容,同時梳理在引入LDO時需要掌握的要點。

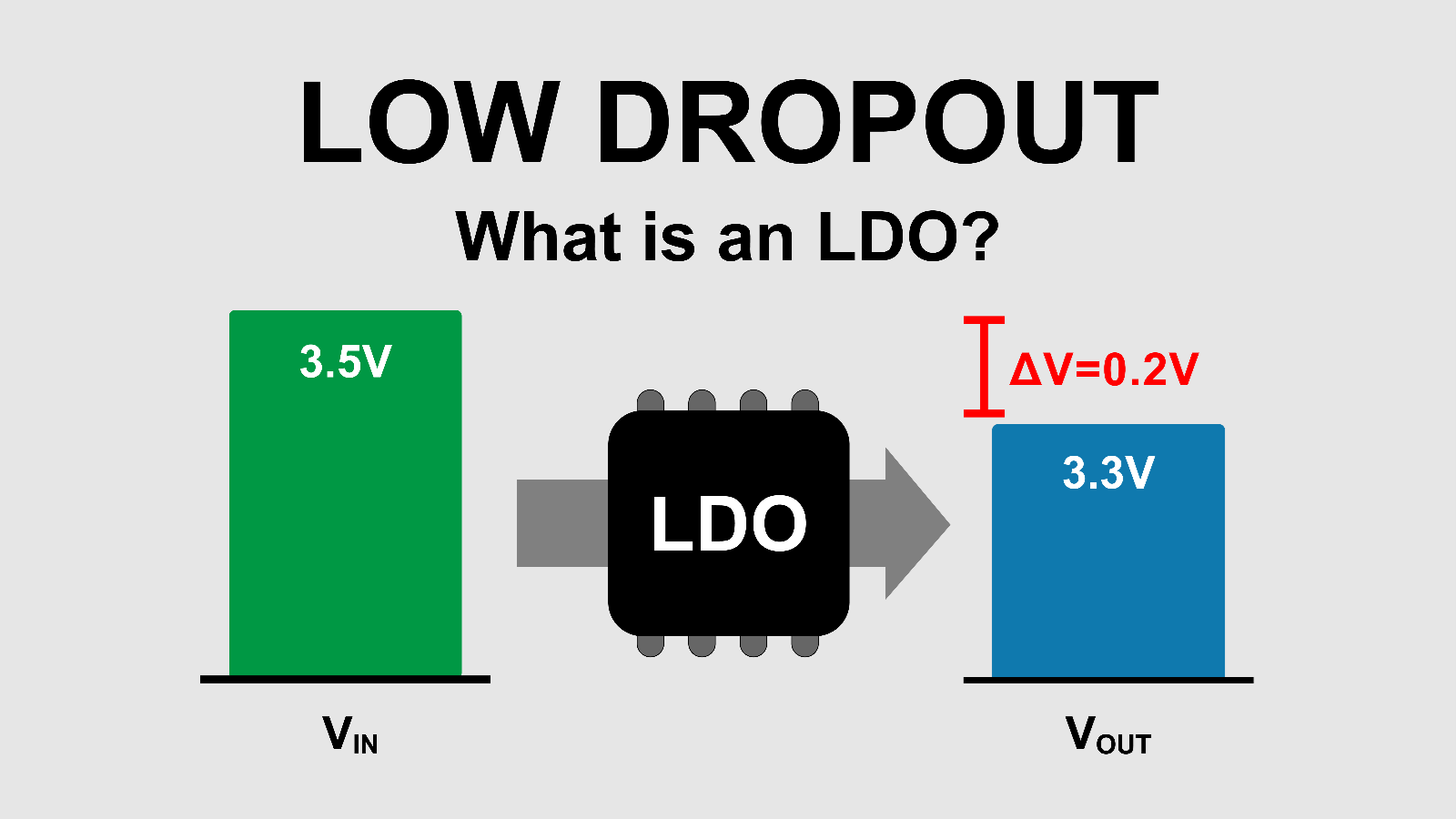

什么是LDO?(定義和基本原理)

LDO是一種即使在輸入電壓與輸出電壓之差(輸入輸出電壓差)較小的情況下,仍能維持一定輸出的線性穩壓器。與普通的三端穩壓器相比,其顯著特點在于所需輸入電壓的裕量更小。本節我們將簡要回顧LDO的定義和歷史背景,并介紹其被眾多設備廣泛采用的原因。

LDO的含義與由來(“Low Dropout”的詞源與定義)

LDO是“Low Dropout Regulator”的英文首字母縮寫,表示其具有低壓差。壓差是指“維持穩定的穩壓所需的最小輸入電壓與輸出電壓之差”。一般的傳統線性穩壓器通常需要比輸出電壓高數V的輸入電壓,而LDO可將這一差值控制在數百mV,有些產品甚至可至數十mV。大多數LDO內部包含通路元件(雙極晶體管或MOSFET)、誤差放大器及保護電路,能否滿足各項規格(輸入電壓范圍、輸出電流范圍等)是選型時的關鍵考量因素。

例如,在需要3.3V的輸出而輸入僅為4.0V左右的條件下,LDO仍有可能穩定工作。這種“低壓差”有助于提高電源效率并減少熱損耗,因此在追求節能與小型化的設備中發揮著重要作用。

與傳統線性穩壓器的區別

線性穩壓器通過內部的通路元件(晶體管等)將輸入電壓中多余的電壓以熱的形式耗散掉,從而實現穩定輸出。傳統線性穩壓器在輸入與輸出電壓差較大時較易于設計,但當輸入輸出電壓差變小時,則難以正常工作。

相比之下,LDO通過采用在線性(電阻)區域易于保持低導通電阻的晶體管等方式,使其即使在輸入輸出電壓差很小時也能工作。具體而言,通過將雙極晶體管或MOSFET以源極跟隨器或射極跟隨器等結構工作,可以將壓差電壓控制在數百mV以下。

許多傳統線性穩壓器要求輸入電壓比輸出電壓高2V以上,其設計是以(輸入電壓 ? 輸出電壓)較大的情況為前提的。而LDO即使在電池驅動等輸入電壓下降的應用中,仍易于保持額定輸出直至極限狀態,因而在節能與低發熱等方面具有優勢。

LDO備受關注的理由(低壓差、低功耗、小型化等)

LDO受到關注的原因主要有以下幾點:

低功耗 :壓差電壓越低,浪費的功耗就越少。

熱設計簡化 :通過抑制輸入輸出電壓差,可減少產生的熱量,有時使用小型散熱片即可。

小型化與電池工作 :在移動設備等應用中,即使電池的電壓下降,仍易于維持工作。

噪聲方面 :與開關穩壓器相比,不易產生高頻噪聲。

因此,LDO被廣泛應用于從電池驅動應用到通信設備以及工業設備等諸多領域。本節主要總結了概念性的理解,后續章節將進一步詳細介紹其電路結構和工作原理。

LDO的電路結構和工作原理

LDO在通過反饋控制來保持輸出電壓穩定方面,與普通的線性穩壓器相同。然而,為了將輸入輸出電壓差控制得較小,在其內部結構、所用晶體管類型及保護功能等方面均采取了特殊設計。本節將介紹LDO的主要電路模塊,并闡述其能夠實現低壓差的原理。

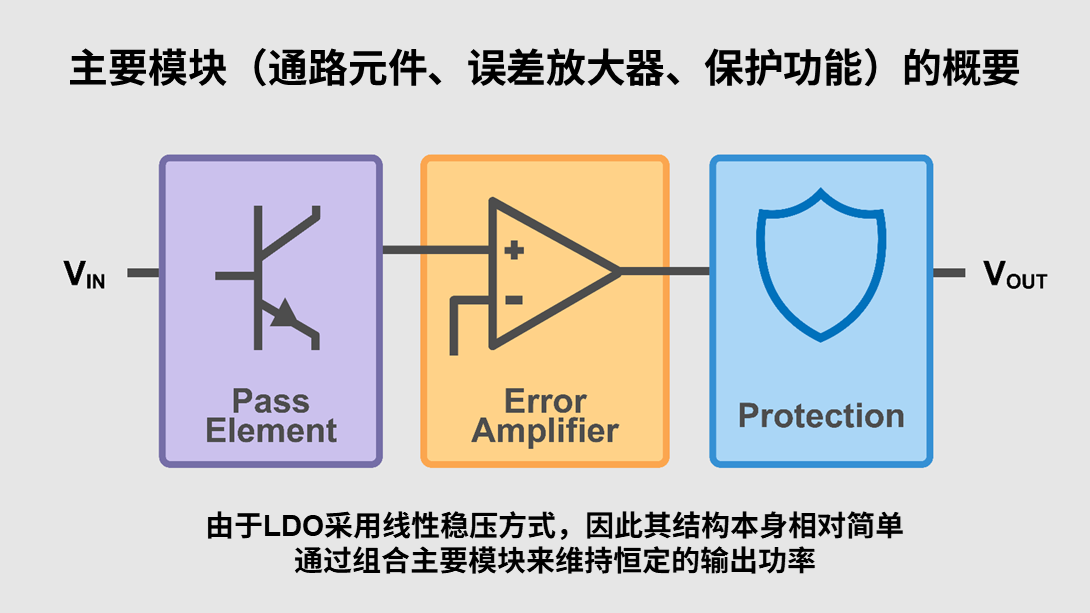

主要模塊(通路元件、誤差放大器、保護功能)概述

LDO的結構本身相對簡單。通過組合以下主要模塊來維持恒定的輸出電壓。

通路元件(Pass Element)

使用雙極晶體管或MOSFET來控制從輸入到輸出的電流。近年來,也有很多LDO通過內置電荷泵或控制電路等特殊設計,使其即使在較低的柵源電壓下也能驅動。

誤差放大器(Error Amplifier)

監測輸出并與參考電壓進行比較,從而控制通路元件。其增益特性與響應速度對精度和瞬態響應有很大影響。

保護功能

內置過流保護、過熱保護及反向電流保護等功能,確保LDO自身的安全性和對負載端的保護。

壓差電壓的原理

LDO特點——壓差電壓的定義為:通路元件在提供電流的同時能保持正常控制的最小輸入輸出電壓差。例如,對于使用PNP晶體管的LDO,其發射極-集電極間電壓與基極-發射極間電壓在臨近飽和狀態工作時的總和會決定壓差電壓。其簡單的模型公式如下所示。

Vdropout≈VCE(sat)+Voverhead

VCE(sat:飽和區的集電極-發射極間的電壓

Voverhead (control margin):誤差放大器為避免通路元件飽和而確保的裕量電壓(用于吸收溫度、工藝偏差以及環路增益下降的數十mV級別)

另一方面,基于MOSFET的LDO則通過在內部巧妙地設計柵極控制電路,使其能夠在低壓差區域內驅動P溝道或N溝道的MOSFET。例如,通過電荷泵等對柵極電壓進行補償,使得即使從外部看到的輸入—輸出電壓差在數百mV以下也能工作。當負載電流為Iout,MOSFET的導通電阻為RDS(on)時,可以表示如下(有時還需加上控制電路所需的最低電壓差。):

Vdropout=Iout×RDS(on)

雙極型LDO時

從產品規格書或晶體管特性中讀取飽和電壓VCE(sat)。

加上偏置電壓VBE和控制電路的裕量電壓,估算壓差電壓。

MOSFET型LDO時

假定負載電流Iout。

確認RDS(on),并通過Iout × RDS(on)計算出最小所需壓差。

同時考慮因柵極驅動電壓而產生的額外裕量,最終求出壓差電壓。

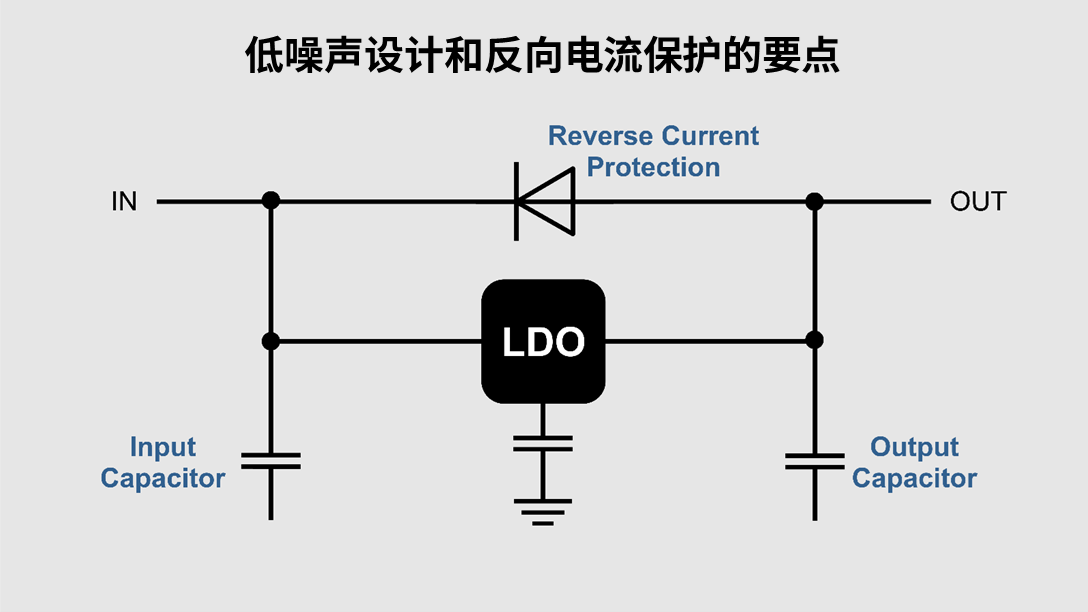

低噪聲設計和反向電流保護的要點

與開關穩壓器相比,LDO具有高頻噪聲更少的優點。但是,根據通路元件的選擇及內部電路結構的不同,雙極晶體管的基極電流路徑或參考電路的噪聲也可能成為問題。設計時需要考慮的要點如下:

旁路電容器

在參考電路或誤差放大器的電源引腳附近接入小容量電容器,以去除噪聲。

布局優化

合理配置輸入輸出電容器,優化GND布線,以抑制尖峰和紋波。

反向電流保護(Reverse Current Protection)

若電流從電池反向流入穩壓器,會導致誤動作或損壞。可添加保護二極管或開關器件等進行防護。

LDO的種類和主要參數

LDO根據其內部所用元件和設計思路,可分為多種類型。同時,在選型時也存在一些需要共同評估的參數。本節將對LDO的代表性種類以及評估其性能時不可或缺的主要參數進行梳理介紹。

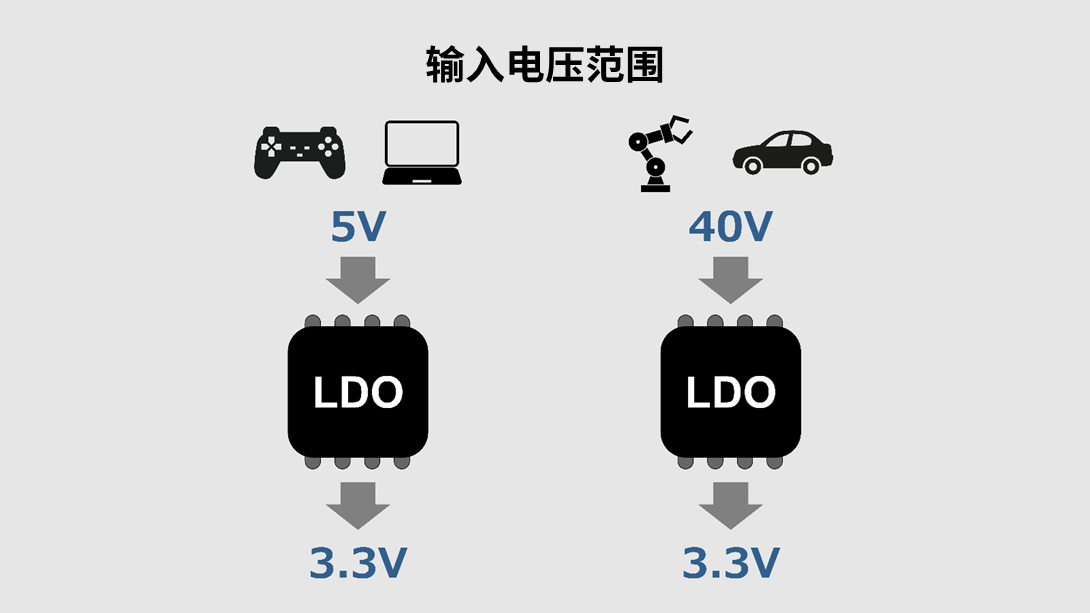

按電壓范圍分類(高電壓和低電壓適用)

LDO的特點是低壓差,但其輸入電壓范圍的跨度較大。例如,既有適用于5V以下工作的電池驅動的低電壓LDO,也有適用于超過30V或40V高輸入電壓的車載及工業設備的LDO。支持高電壓的LDO,其功率晶體管通常具有更高的耐壓和更強的保護功能。而對于生成1V左右等超低電壓領域的LDO,其在MOSFET的基礎上對柵極驅動進行優化,從而將壓差降至極限。

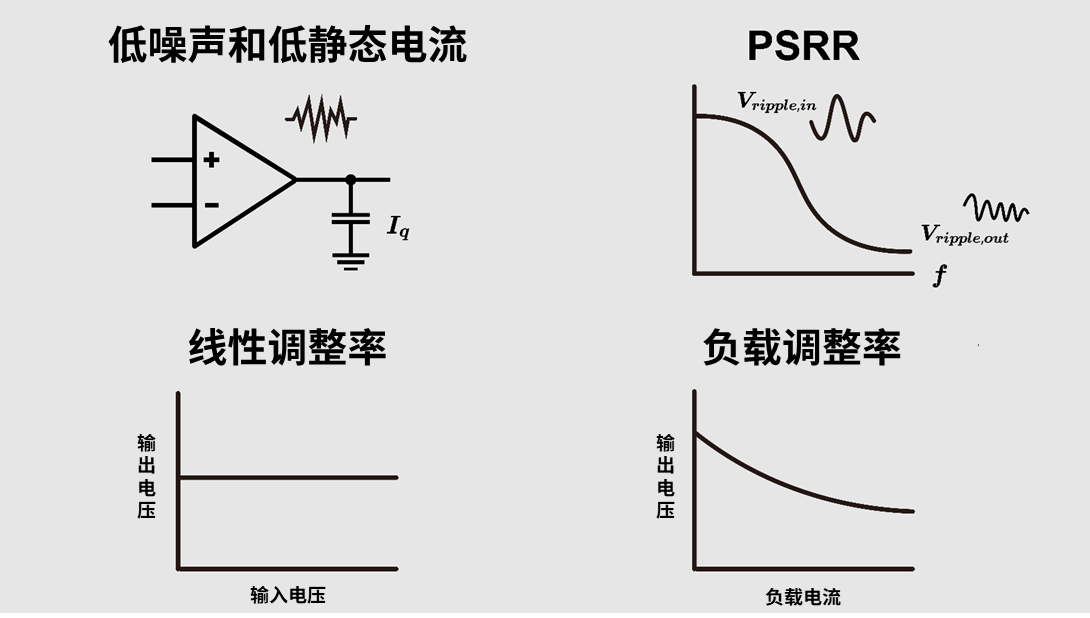

低噪聲、低靜態電流、PSRR、線性調整率和負載調整率

低噪聲和低靜態電流

低噪聲型

適用于為模擬電路或無線電路供電等時,噪聲對信號質量影響較大的應用場景。其設計降低了參考電路和誤差放大器的噪聲,并盡量抑制了通路元件的開關噪聲。

低靜態電流(Iq)型

目的是通過將待機時的消耗電流控制到很小來延長電池的驅動時間。有些產品通過小容量電容器和簡化的內部電路結構,將靜態電流控制在數μA以下。

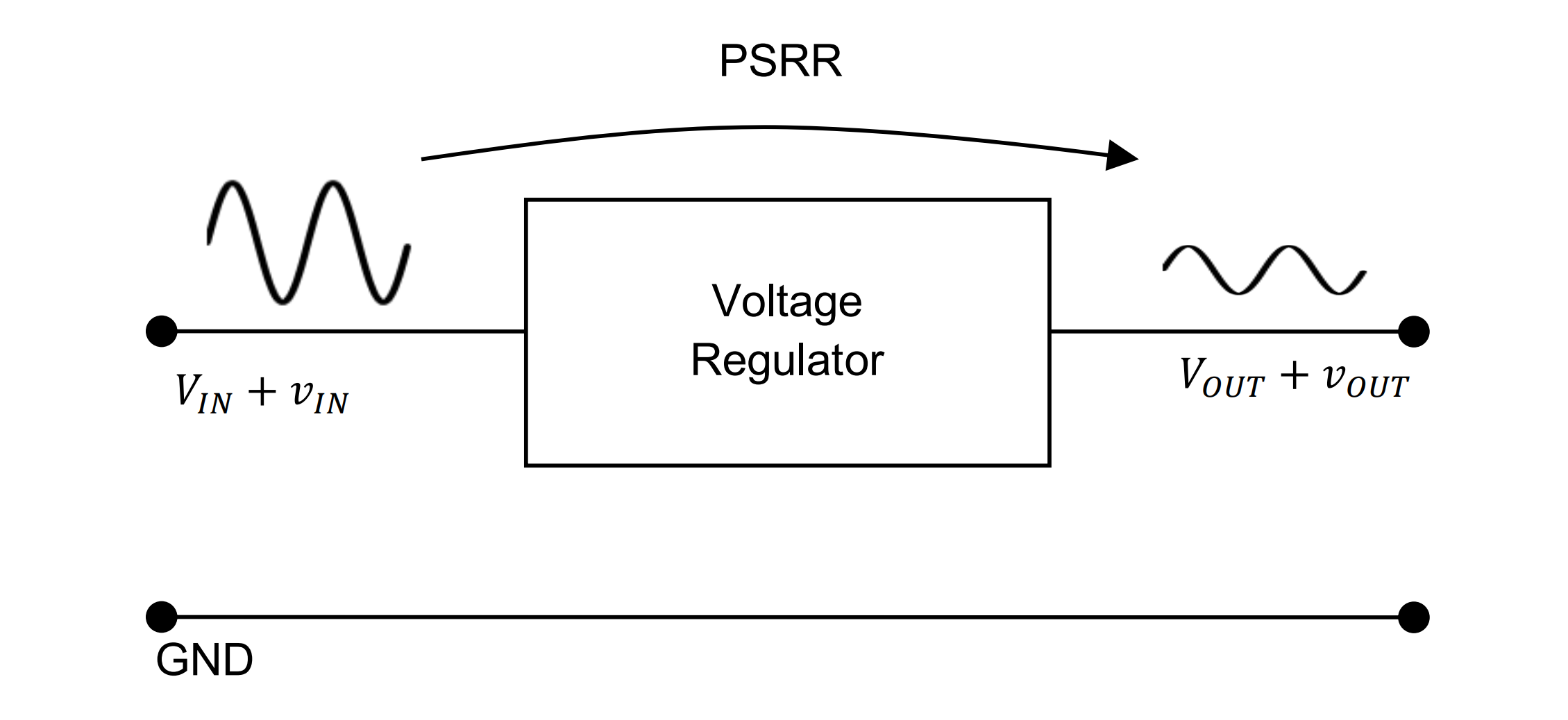

PSRR(Power Supply Ripple Rejection)

PSRR是衡量輸入側的紋波或噪聲有多大程度傳遞至輸出側的指標。通常以頻率特性表示,尤其在數十kHz以上的高頻區間的PSRR備受重視。例如,在音頻電路或高精度模擬電路中,選擇PSRR高的LDO可減少電源噪聲的影響,有助于提高精度。其定義如下:

PSRR(f)=20log10(Vripple,in(f)Vripple,out(f))

數值越大,表示對輸入紋波的抑制能力越強。其中,Vripple,in(f)為輸入側的紋波電壓,Vripple,out(f)為輸出側殘留的紋波電壓。

過程計算示例(PSRR求解思路)

在輸入端施加已知振幅的紋波電壓(例如:10mV峰值)。

測量輸出端出現的紋波幅度(例如:1mV峰值)。

分別以振幅或RMS進行比較,并按如下方式計算:

PSRR(f)=20log10(10mV1mV)=20log10(10)=20dB

線性調整率和負載調整率

線性調整率

表示輸入電壓變化時輸出電壓的波動程度。通常表示如下(常用mV/V或%/V表示):

Line regulation=ΔVoutΔVin

負載調整率

表示負載電流變化時輸出電壓的波動程度。表示如下(常用mV/mA或%/mA表示):

Load regulation=ΔVoutΔIout

二者都是量化LDO電壓控制性的指標。產品規格書中會標明Max值和typ值。考慮工作溫度范圍內的波動情況,并確認所實現的電路是否滿足必要的要求非常重要。

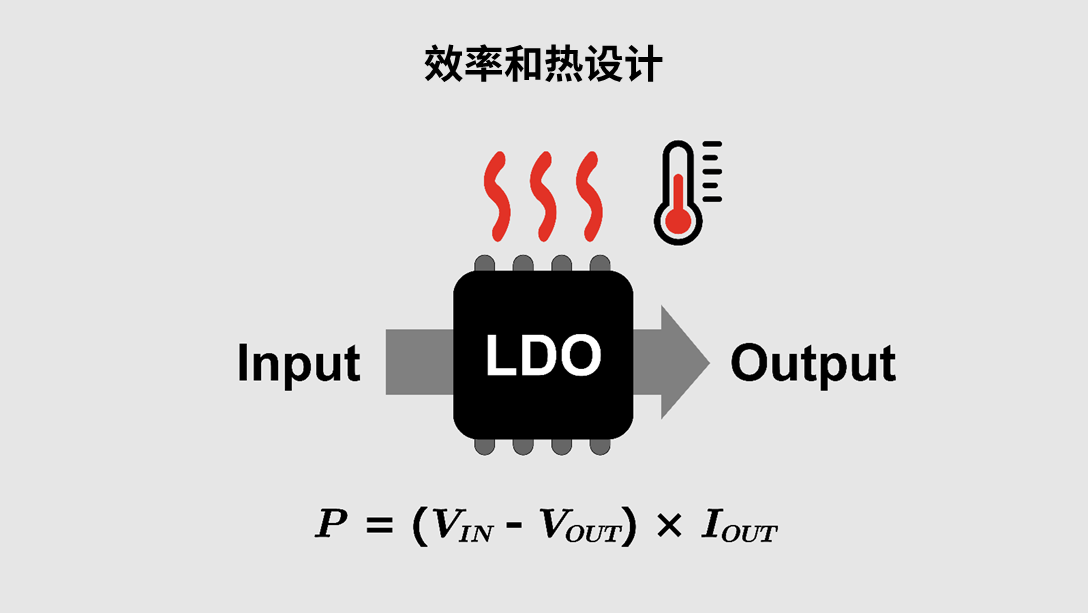

效率和熱設計(功耗、發熱、封裝)

作為線性穩壓器的LDO,其基本功耗可用以下公式進行估算:

Pdiss=(Vin?Vout)×Iout

這是輸入電源提供的功率與輸出端所用功率之差。

這部分損耗幾乎全部以熱的形式散發,因此當輸入輸出電壓差較大或處理大電流時,發熱會增加,需要考慮散熱器或電路板布線時的散熱設計。

與開關穩壓器不同,LDO在提升效率方面存在一定局限,但通過盡可能降低壓差電壓,可以抑制輸入與輸出間的電壓差,從而減少損耗。此外,由于不同封裝的熱阻不同,所以選擇PowerPAD或倒裝芯片等散熱特性優良的封裝也至關重要。

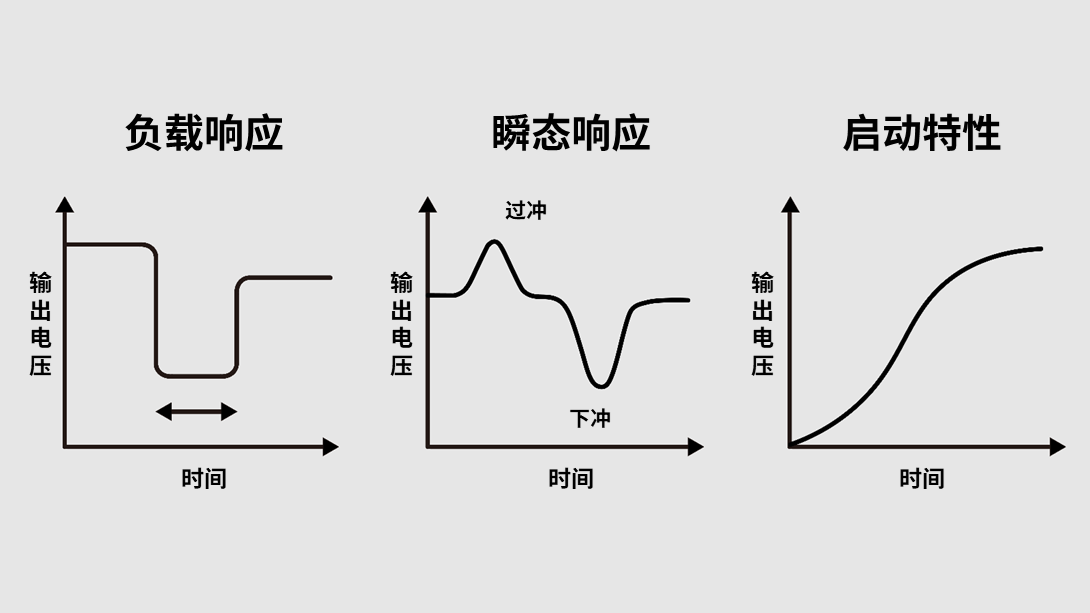

負載響應、瞬態響應和啟動特性

當電源負載發生瞬時增減時或LDO啟動時,輸出電壓的穩定程度是設計階段需要重點關注的內容。

負載響應

負載電流驟變時輸出電壓波動的大小及恢復所需的時間。受誤差放大器的速度、輸出電容器的容量和內部電阻等因素影響。

瞬態響應

電壓暫時出現過沖或下沖的現象。在需要高速響應的應用場景(如高速數字電路)中,可能成為大問題。

啟動特性

LDO在通電時輸出電壓上升過程中的動作。為避免急劇上升對負載造成不良影響,部分產品具有軟啟動功能。

近年來,還出現了將控制IC與周邊電路集成于一體的LDO模塊,這種減少電路板安裝工序和外置元件選型工作量的方法備受關注。此類模塊型產品的工作范圍和散熱設計明確,適合重視開發速度的應用場景。

LDO與其他方式的比較及選型方法

除了LDO之外,還有多種電壓調節方式,每種方式各有其優缺點。本節將通過與經常被比較的開關穩壓器和傳統線性穩壓器進行對比,重新確認LDO的特點,并梳理出不同應用場景的選型要點。

開關穩壓器 vs LDO(功耗和效率比較)

開關穩壓器通過脈寬調制(PWM)和脈沖頻率調制(PFM)等方式使開關器件高速導通和關斷,經由電感和電容器形成輸出電壓。代表性方式有降壓(Buck)、升壓(Boost)與升降壓兩用(Buck-Boost)等。在晶體管與二極管(或同步整流MOSFET)損耗更小時流通電流,從而實現高效率,效率超過80?90%也并不罕見。

另一方面,開關穩壓器通常需要電感和大容量電容器等外置元件,占用安裝空間且電路設計復雜。此外,高速開關容易引發噪聲(EMI)與紋波,因此需考慮通過屏蔽或優化布局予以抑制。

LDO以線性方式控制從輸入電壓至輸出電壓的電力,因此會產生(Vin – Vout)×Iout所示的損耗,這部分損耗作為熱量被耗散掉。從效率角度比較,開關穩壓器根據負載電流和設計的不同,可實現80%至90%以上的效率,而LDO的效率近似如下:

η≈VoutVin×100%

輸入輸出電壓差越大,效率就越低;但當壓差電壓非常小時,由于(Vin – Vout)本身可以抑制得很小,因此在實際應用中有時仍可維持一定的效率。此外,LDO具有不易產生高頻噪聲的優點,同時其外置元件只需輸入輸出電容器,這使得它安裝簡單且輸出紋波較小。

總而言之,若存在較大的壓降或更加注重高效率時,更適合選用開關穩壓器;而在電壓差較小的環境或對噪聲敏感的模擬電路等應用中,LDO更為有效。

傳統線性穩壓器 vs LDO(與三端穩壓器等的區別)

傳統線性穩壓器設計時,通常要求輸入電壓留有約2~3V的裕量,并以通路元件在遠離飽和區的狀態下進行控制為前提。而LDO則通過將通路元件的工作點推至接近飽和的狀態,從而成功地將壓差控制到數百mV以下。

通路元件的選擇與結構

傳統線性穩壓器為實現控制,通常在基極–發射極電壓或集電極–發射極電壓上留出一定裕量;而LDO通過采用MOSFET使其在柵源電壓較小時也能工作,或通過電路設計使雙極晶體管也允許在接近飽和狀態下進行控制等,以此降低壓差電壓。

反饋電路的優化

傳統線性穩壓器的控制特性相對寬松,而LDO則通常通過優化誤差放大器的偏置電壓和內部參考源設計,確保在較低電壓差下仍能實現穩定控制。

應用領域的差異

傳統線性穩壓器多用于將AC適配器等較高的輸入電壓降壓并輕松實現穩壓的應用場景,而LDO則在電池驅動或使用1~2V低電壓的數字IC等要求低電壓和低功耗的環境中更具發揮優勢。

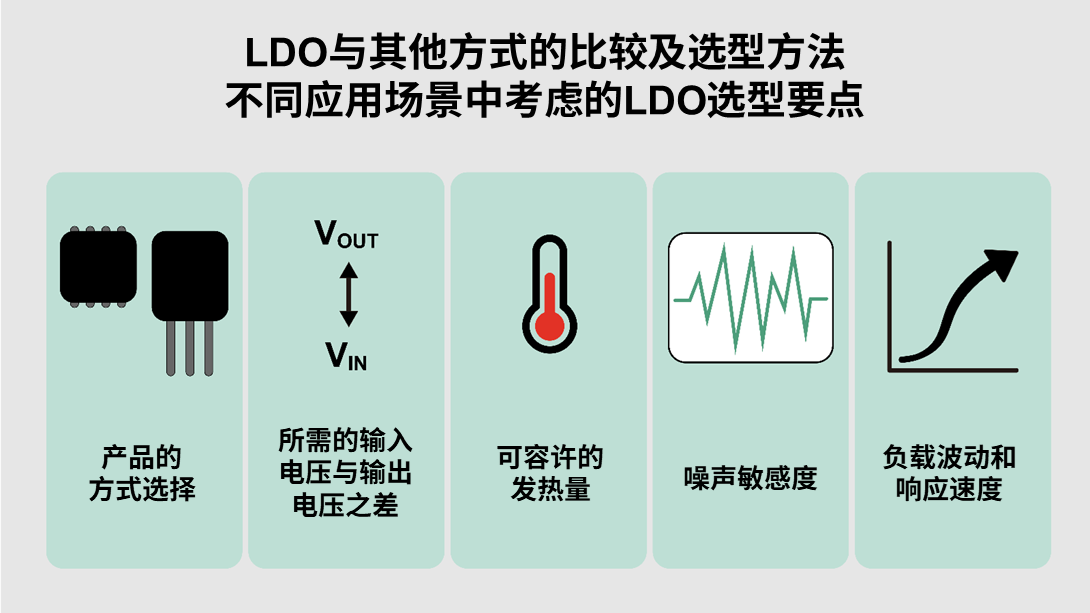

不同應用場景中考慮的LDO選型要點

LDO的主要選型要點如下:

所需的輸入輸出電壓差

當電池的終止電壓(最低電壓)接近輸出電壓時,必須選擇壓差電壓小的LDO。

可容許的發熱量

由于LDO的(Vin – Vout)× Iout會轉化為熱,因此散熱設計和封裝的選擇很重要。

噪聲敏感度

在模擬電路或高頻電路中,PSRR和低噪聲特性尤為重要。

消耗電流

對于希望盡量降低待機電流的應用場景,優先選擇低Iq型。

負載波動和響應速度

對于有急劇負載波動的電路,建議選用瞬態響應性能優異的LDO。

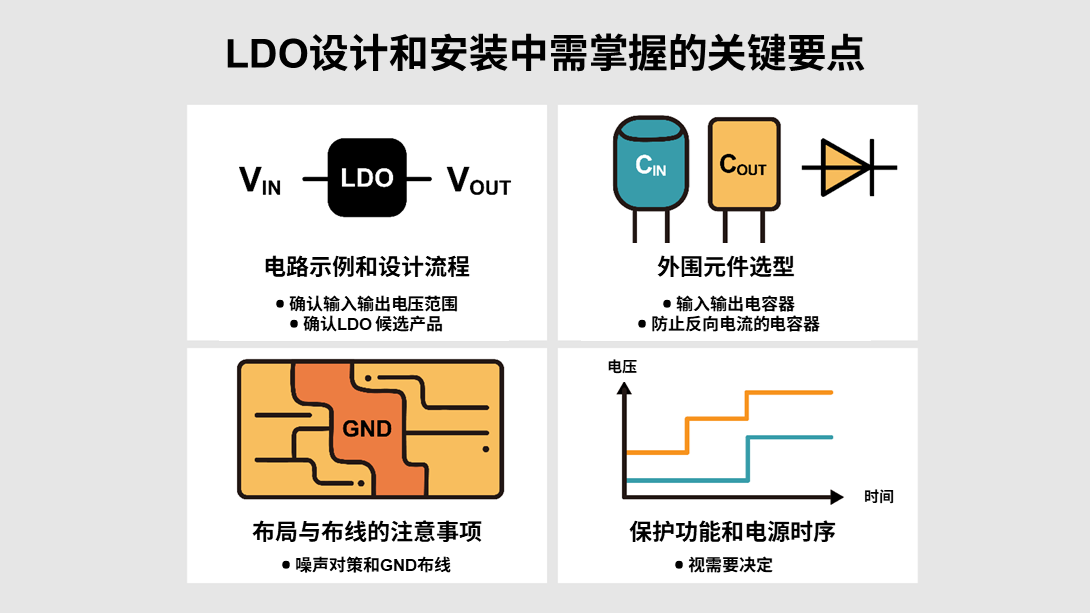

LDO設計和安裝中需掌握的關鍵要點

在實際將LDO嵌入電路時,應參考產品規格書中推薦的元件和布局指南,進行滿足各項特性的設計。本節將逐步介紹典型的設計流程和注意事項。

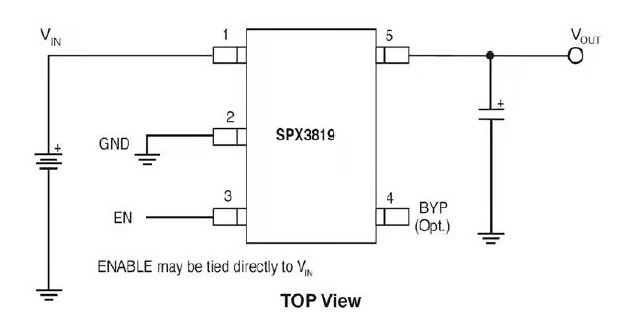

電路示例和設計流程(基礎設計~元件選型)

LDO的設計流程大致遵循以下步驟:

確認輸入輸出電壓范圍

根據是電池驅動還是AC適配器等,掌握預期電源的最小和最大電壓。

確認所需的輸出電流和負載特性

掌握最大負載電流將達到多少A,并了解瞬時負載波動幅度。

確認LDO候選產品

參考產品規格書,尋找滿足壓差電壓、PSRR、消耗電流、保護功能等要求的產品。

選擇外圍元件

由于輸出電容器的容量和ESR范圍直接關系到LDO工作的穩定性,務必確認制造商的推薦值。

熱設計

結合封裝和安裝條件,計算(Vin – Vout)× Iout是否在容許范圍內。必要時考慮擴大銅箔面積等散熱措施。

外圍元件選型(輸入與輸出電容器、防反向電流二極管等)

LDO的輸出電容器對于確保相位補償與誤差放大器的穩定工作至關重要。產品規格書中通常會寫明推薦容量和ESR范圍,若偏離這些范圍,可能導致振蕩或瞬態響應惡化。

輸入電容器用于輔助瞬時電流供應以及抑制輸入電源的紋波。通常采用數μF的陶瓷電容器,但若預計存在較大的負載波動,有時可追加更大容量的電容器。

防反向電流二極管在存在電池等備份電源時需要考慮使用。在多電源切換的設計中,通常會加入二極管以防止電流通過LDO的通路元件發生反向流動。

布局和布線的注意事項(噪聲對策和GND布線等)

雖說LDO基本上噪聲較少,但仍建議在布局時注意以下事項:

確保最短路徑

將輸入電容器和輸出電容器安裝在LDO引腳附近,以減少不必要的布線電感和寄生電阻。

統一管理GND布線

根據需要將電源GND和信號GND分離,防止噪聲混入測量系統。

確保熱擴散

若有散熱焊盤,應在電路板內層或背面設置過孔,以促進散熱。

保護功能的運用和電源時序(按需簡要使用)

LDO通常配備過流保護、過熱保護等安全功能,但重要的是不要過度依賴這些功能,而應評估實際環境中可能出現的過載程度后進行選型。

另外,對于多電壓的CPU和FPGA等需要多路電源線按順序啟動時,有時會使用LDO的使能引腳進行時序控制。結合延時電路或微控制器控制,使所需電源適當啟動,從而提升系統運行的可靠性。

LDO的最新技術動向

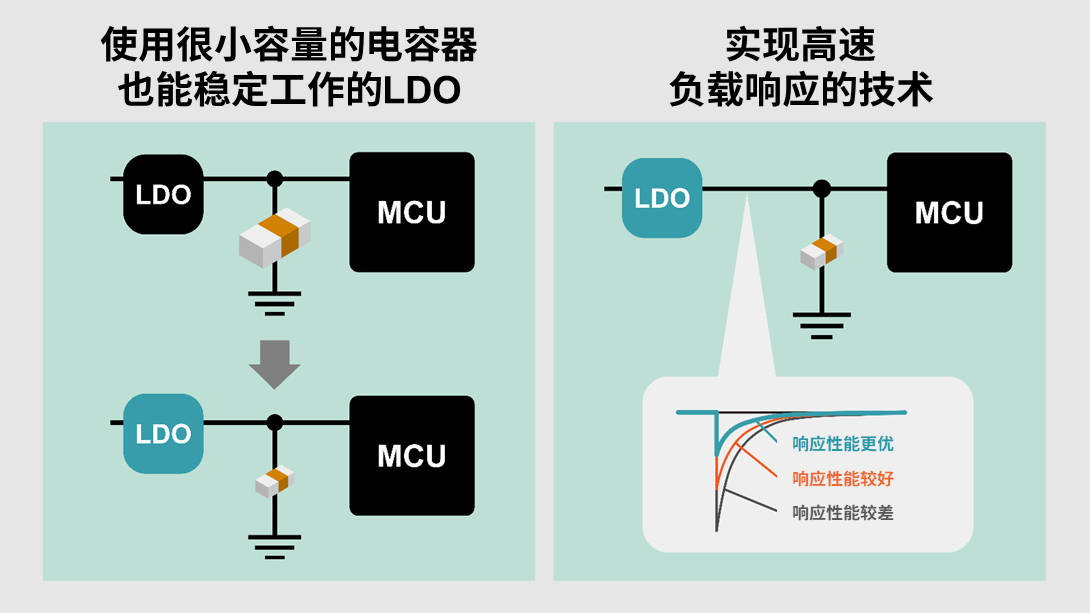

近年來,在LDO領域,針對更嚴苛的低功耗要求與縮減安裝空間的需求日益增多,以下新的技術方案備受關注。這些技術通過實現“超小容量輸出電容器的適用”和“高速負載響應性能的提升”,正在逐步克服傳統LDO難以應對的難題。

使用很小容量的電容器也能穩定工作的技術

技術概要

傳統LDO為確保穩定工作,通常需要1μF左右的輸出電容器。最近,通過對模擬電路寄生分量的徹底優化,改進誤差放大器和布線,出現了使用nF量級的電容器也不會發生振蕩的控制技術。

主要優勢

減少元件數量和安裝空間 :可大幅減少輸出電容器的容量與數量

降低成本 :通過電容器小型化或數量削減,有望降低成本

提升可靠性 :通過減少汽車與工業等領域中常用的電容器安裝數量,降低元件故障風險和安裝不良風險

實現高速負載響應的技術

技術概要

為了在負載電流急劇變化時將輸出電壓的波動幅度控制在更小范圍,已開發出提升LDO內部反饋電路與誤差放大電路速度的技術。代表性的方法是通過將控制系統和補償系統分離或組合多級專用放大器,從而在避免發生不穩定振蕩的前提下,將響應速度提升至極限。

主要優勢

提升電源品質 :可迅速響應數字IC急劇的消耗電流變化和高精度模擬電路的瞬時負載波動

優化電容器容量 :即使不采用大容量電容器,也能獲得足夠的響應性能,從而提升設計靈活性

持續演進與未來展望

新技術的結合

通過將“適用很小容量的電容器”和“高速負載響應技術”相結合,正逐步實現例如采用nF級電容器時,仍可在急劇的負載波動下保持穩定輸出的LDO。

應用領域的擴展

物聯網設備和可穿戴設備等需要兼顧低功耗和小型化的應用需求預計將持續增長。此外,在汽車和工業設備領域,不僅要求縮小安裝空間,還需實現更高可靠性(滿足溫度特性和耐壓等安全標準),這使得配備上述先進技術的LDO受到越來越多的關注。

各半導體制造商正不斷擴充集成了多個電源線的模塊化LDO以及實現系統整體節能的解決方案,其應用領域正在不斷擴大。

總結

LDO能夠在保持輸入輸出電壓差較小的狀態下工作,因體積小、低噪聲、節能而被應用于各類設備。適用于移動設備、車載設備和工業設備等各種領域中需要低功耗和散熱對策的電路。

LDO基礎要點回顧

定義 :Low Dropout Regulator是即使輸入輸出電壓差很小也能工作的線性穩壓器

電路結構 :通過通路元件、誤差放大器和保護功能來穩定輸出電壓,其特點是采用低壓差電壓設計

主要參數 :壓差電壓、PSRR、線性調整率和負載調整率、發熱和效率、負載響應等是選型時的重要參數

比較 :與開關穩壓器相比噪聲更少,與傳統線性穩壓器相比可在更低壓差下工作

設計和安裝 :外圍元件選型和布局直接關系到工作的穩定性,同時需要考慮熱設計和保護功能

未來趨勢

近年來,物聯網設備和可穿戴設備等電池容量有限卻要求長續航的領域不斷增加。在這些領域,超低壓差、超低靜態電流規格的LDO需求日益增長,各制造商正致力于提升其特性。此外,面向車載系統也開發了很多高耐壓LDO,LDO在工業與汽車領域也得到了廣泛應用。

另外,在需要復雜電源結構的系統中,通常會使用開關穩壓器進行初步降壓,然后在最后階段使用LDO來降低噪聲。由此可見,LDO在電源設計中占據重要地位,未來在高性能和超低噪聲等方面的技術演進也備受期待。

-

電容器

+關注

關注

64文章

6963瀏覽量

107948 -

半導體

+關注

關注

339文章

30870瀏覽量

265015 -

ldo

+關注

關注

35文章

2452瀏覽量

160171 -

線性穩壓器

+關注

關注

5文章

1171瀏覽量

71566

原文標題:R課堂 | LDO基礎知識介紹

文章出處:【微信號:羅姆半導體集團,微信公眾號:羅姆半導體集團】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文詳解LDO的電源抑制比

一文介紹LDO噪聲及分類

開發者學習筆記——View&Canvas

Altera FPGA CPLD學習筆記

一文講解LDO學習筆記

一文講解LDO學習筆記

評論