12位DAC63204W和10位DAC53204W(DACx3204W)是引腳兼容的四通道、緩沖、電壓輸出和電流輸出智能數模轉換器(DAC)系列。這些器件支持Hi-Z掉電模式和斷電條件下的Hi-Z輸出。DAC輸出提供力檢測選項,可用作可編程比較器和電流源或灌電流。多功能GPIO、功能生成和NVM使這些智能DAC能夠實現無處理器應用和設計重用。這些器件可自動檢測I2C、SPI和PMBus接口,并包含內部基準電壓源。

這些智能DAC的功能集與微型封裝和低功耗相結合,是電壓裕度和縮放、用于偏置和校準的直流設定點以及波形生成等應用的絕佳選擇。

*附件:dac53204w.pdf

特性

- 具有靈活配置的可編程電壓或電流輸出:

- 電壓輸出:

- 1LSB DNL

- 收益為 1 ×、1.5 ×、2 ×、3 ×和 4 ×

- 電流輸出:

- 1LSB INL 和 DNL(8 位)

- ±25μA、±50μA、±125μA、±250μA輸出范圍選項

- 電壓輸出:

- 適用于所有通道的可編程比較器模式

- VDD關閉時的高阻抗輸出

- 高阻抗和電阻下拉掉電模式

- 50MHz SPI 兼容接口

- 自動檢測I2C、SPI或PMBus接口

- 1.62V VIH,VDD = 5.5V

- 通用輸入/輸出 (GPIO) 可配置為多種功能

- 預定義波形生成:正弦波、三角波、鋸齒波

- 用戶可編程非易失性存儲器 (NVM)

- 內部、外部或電源作為參考

- 工作范圍廣:

- 電源:1.8V 至 5.5V

- 溫度范圍:–40°C 至 +125°C

- 微型封裝:16引腳DSBGA(1.76mm×1.76mm)

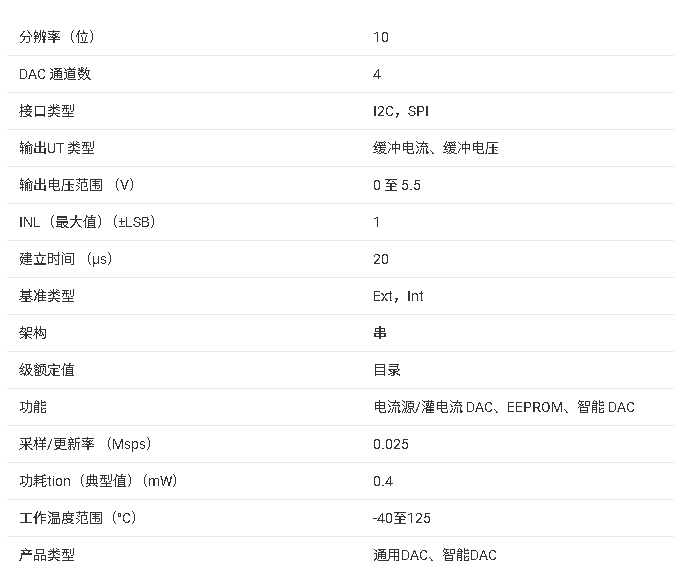

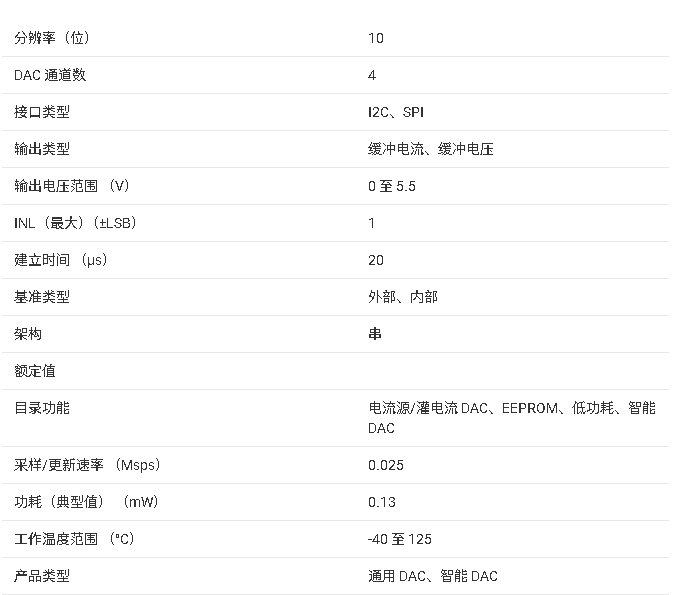

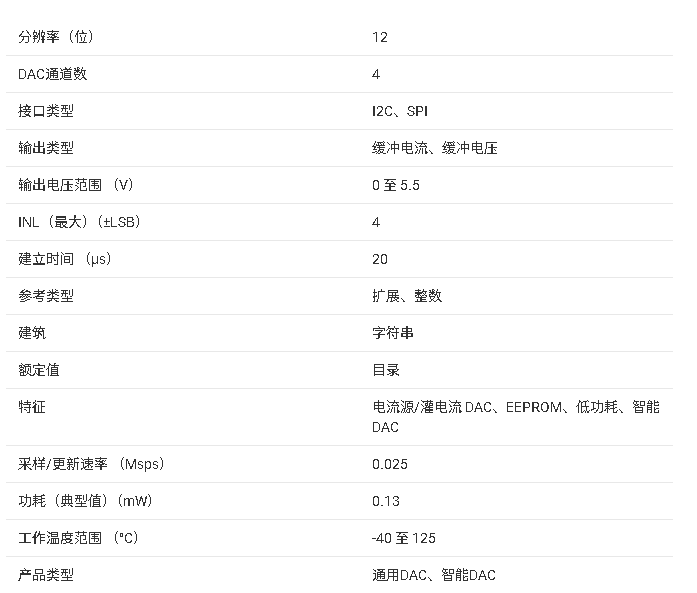

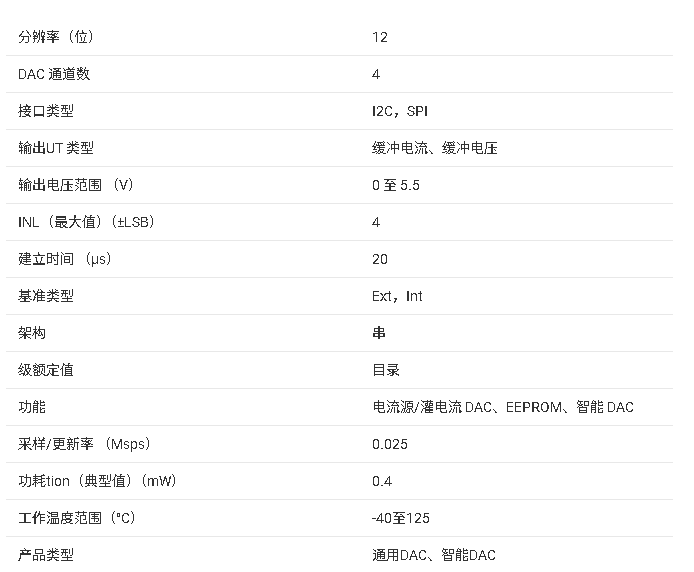

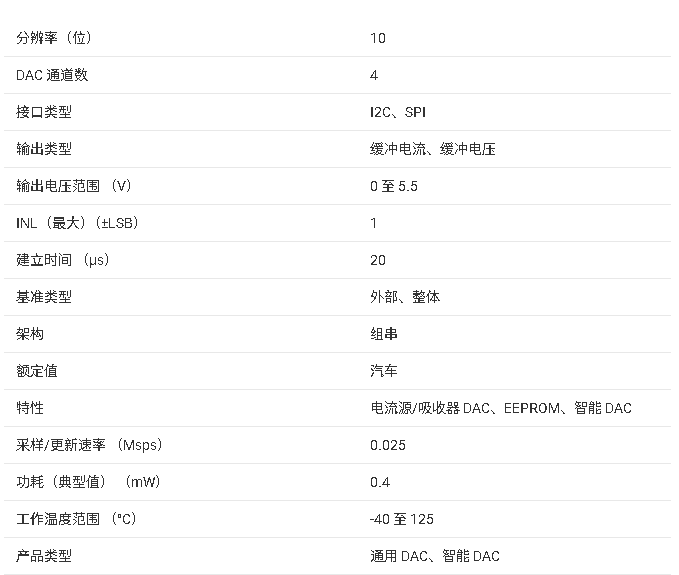

參數

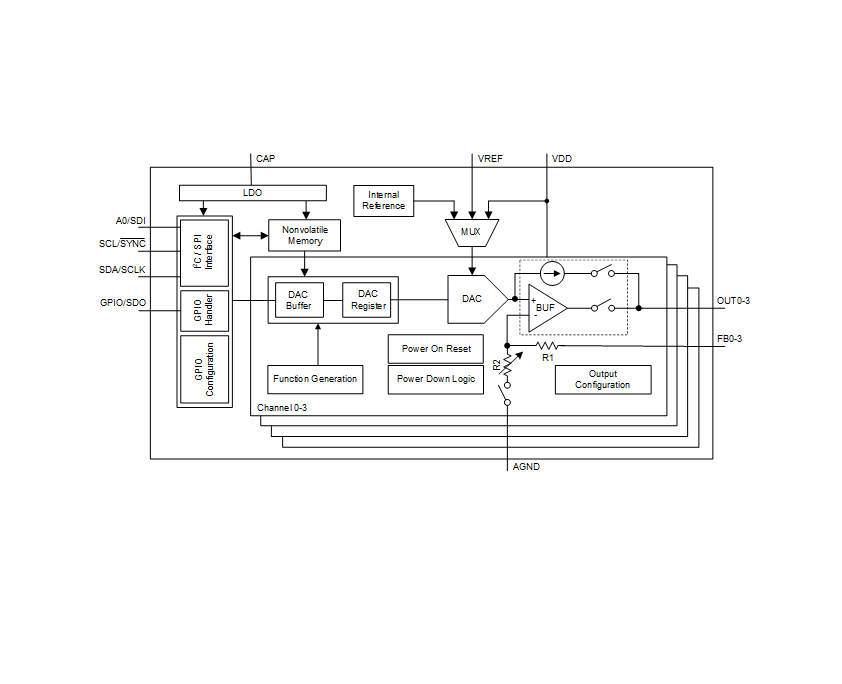

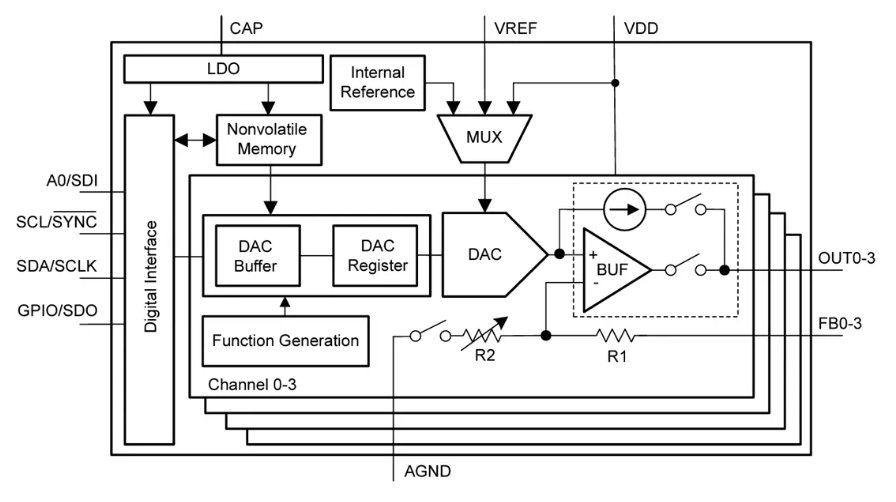

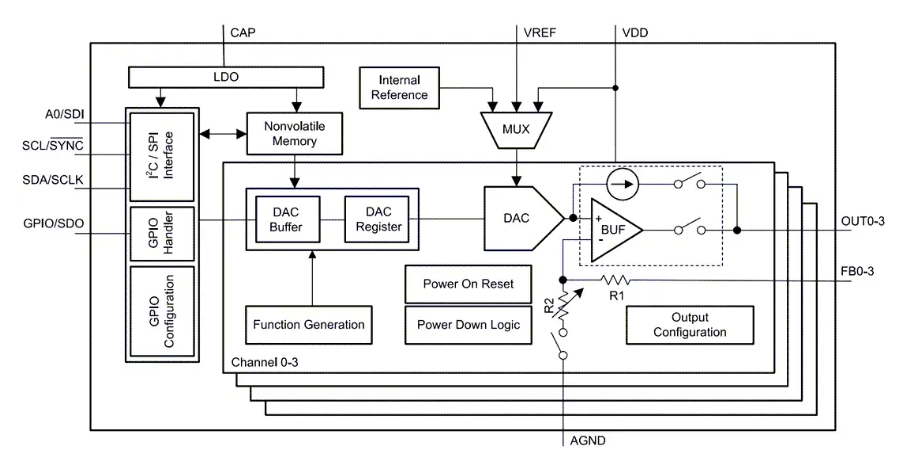

方框圖

一、產品概述與型號差異

DACx3204W 系列是高度集成的 “智能 DAC”,通過四通道獨立配置、多接口自動識別、內置診斷與波形生成功能,適配小型化系統設計。兩款型號僅分辨率不同,其他功能與封裝完全兼容,便于根據精度需求靈活選型。

1. 型號核心差異

| 型號 | 分辨率 | 核心精度指標 | 適配場景 |

|---|---|---|---|

| DAC53204W | 10 位 | 積分非線性(INL)±1.25 LSB,成本更優 | 對精度要求適中的工業控制模塊 |

| DAC63204W | 12 位 | 積分非線性(INL)±5 LSB,支持更高精度輸出 | 光學模塊、高精度傳感器校準 |

2. 基礎參數總覽

| 類別 | 關鍵指標 | 說明 |

|---|---|---|

| 封裝規格 | 1.76mm×1.76mm 16 引腳 DSBGA(YBH 封裝) | 超小尺寸,0.4mm 最大高度,適配高密度布局 |

| 工作溫度 | -40℃~+125℃ | 滿足工業級寬溫環境需求 |

| 供電范圍 | VDD:1.7V | 單電源供電,適配不同系統電壓需求 |

| 靜態電流 | 電壓輸出模式典型 150μA / 通道;電流輸出模式典型 42μA~200μA / 通道 | 低功耗,適配電池或環路供電場景 |

| 核心集成 | 12 位比較器、1.21V 內部基準、NVM、波形生成器 | 減少外圍器件,簡化系統設計 |

二、核心功能與性能參數

1. 多模式輸出模塊(電壓 / 電流)

作為核心功能,DAC 支持電壓與電流輸出獨立配置,覆蓋不同信號需求,且各通道可單獨設置輸出模式與參數:

(1)電壓輸出模式

- 性能參數 :

- 輸出范圍:依賴參考源與增益,內部 1.21V 基準下支持 1.5×/2×/3×/4× 增益(如 4× 增益時輸出 0~4.84V),外部參考或 VDD 作為參考時增益固定 1×;

- 精度:DAC63204W(12 位)總未調整誤差(TUE)≤1.5% FSR,DAC53204W(10 位)INL±1.25 LSB;

- 動態特性:建立時間 20μs(1/4

3/4 量程,±10% FSR),輸出噪聲(0.1Hz10Hz)典型 50μVpp,電源抑制比(AC)-68dB。

- 關鍵功能 :

- 增益靈活配置:支持內部基準(1.5×~4×)、外部基準(1×)、VDD 作為基準(1×)三種模式,適配不同輸出范圍需求;

- 高阻輸出:VDD 掉電時輸出自動進入高阻態, leakage 電流≤500nA,避免影響后端電路;

- 可編程壓擺率:支持 1

32 LSB 步長、4μs5.1ms / 步時間配置,避免輸出信號突變導致的系統干擾。

(2)電流輸出模式

- 性能參數 :

- 輸出范圍:支持 ±25μA/±50μA/±125μA/±250μA 四檔可選,8 位分辨率;

- 精度:積分非線性(INL)±1 LSB,增益誤差 ±1.3% FSR,輸出阻抗典型 60MΩ;

- 動態特性:建立時間 60μs(1/4

3/4 量程,±1 LSB),輸出噪聲(0.1Hz10Hz)典型 150nApp。

- 關鍵功能 :

- 雙向電流輸出:支持 sourcing/sinking 雙向電流,適配電流源 / 灌應用場景;

- 低泄漏設計:電流模式下反饋引腳(FBx)懸空時泄漏電流最小化,保障輸出精度。

2. 智能功能模塊

(1)可編程波形生成

支持正弦波、三角波、鋸齒波(含反向鋸齒波)三種預設波形,無需處理器干預即可獨立生成,簡化信號源設計:

- 波形參數 :

- 正弦波:24 個離散點 / 周期,支持 0°/90°/120°/240° 四相位配置,頻率由壓擺率決定(如 4μs / 步時頻率≈10.4Hz);

- 三角波 / 鋸齒波:由 DAC-X-MARGIN-HIGH/LOW 寄存器設定波形上下限,頻率 = 1/[2× 步長時間 ×(量程 / 步長)](三角波)或 1/[步長時間 ×(量程 / 步長 + 1)](鋸齒波);

- 應用價值 :可直接作為測試信號源或控制信號,減少對外部 MCU 的依賴,降低系統功耗。

(2)非易失性存儲器(NVM)

內置用戶可編程 NVM,支持存儲寄存器配置參數,實現上電自動加載,無需每次啟動重新配置:

- 存儲內容 :包括 DAC 輸出范圍、增益、波形參數、電源 - down 模式等關鍵配置;

- 可靠性指標 : endurance(-40℃~+85℃)20000 次擦寫,數據 retention(25℃)50 年,滿足長期穩定使用需求;

- CRC 校驗 :NVM 數據加載時自動進行 16 位 CRC 校驗,檢測數據損壞(NVM-CRC-FAIL-USER/INT 標志位提示故障)。

(3)可編程比較器模式

每個 DAC 通道可配置為可編程比較器,利用反饋引腳(FBx)實現閾值檢測,適配故障診斷場景:

- 工作模式 :

- 無滯回模式:直接比較 FBx 輸入與 DAC 輸出;

- 滯回模式:通過 DAC-X-MARGIN-HIGH/LOW 設定滯回閾值,避免噪聲誤觸發;

- 窗口比較器模式:檢測 FBx 輸入是否在設定窗口內,輸出結果存儲于 CMP-STATUS 寄存器;

- 輸出配置 :支持推挽 / 開漏輸出,可反轉輸出極性,適配不同系統電平需求。

3. 多接口與控制功能

(1)自動識別數字接口

支持 SPI、I2C、PMBus 三種接口自動檢測,無需硬件配置,簡化系統集成:

- SPI :默認 3 線模式(SCLK/SYNC/SDI),GPIO 可配置為 SDO 實現 4 線讀回,寫操作最高 50MHz,讀操作最高 2.5MHz;

- I2C :支持標準模式(100kHz)、快速模式(400kHz)、快速模式 +(1MHz),通過 A0 引腳可配置 4 個從地址,支持廣播地址同步多器件;

- PMBus :I2C 模式下兼容 PMBus 命令(如 Margin High/Low、Turn On/Off),適配電源管理系統。

(2)通用輸入輸出(GPIO)多功能配置

GPIO 引腳可配置為 13 種輸入 / 輸出功能,實現處理器 - less 控制,提升系統可靠性:

- 輸入功能 :觸發故障轉儲(FAULT-DUMP)、DAC 電源 - down、比較器復位、波形啟停等,支持邊沿 / 電平觸發;

- 輸出功能 :指示 NVM 忙、DAC 通道忙、窗口比較器結果等狀態,避免額外通信開銷;

- 應用價值 :系統故障時可通過 GPIO 直接觸發保護動作(如切換 DAC 至安全輸出),無需軟件干預。

三、功能架構與典型應用

1. 核心架構

采用 “數字控制 - 模擬輸出 - 診斷監控” 三層架構,模塊協同實現高集成度與靈活性:

- 數字控制層 :含接口檢測、NVM 管理、波形生成邏輯,負責指令解析、參數存儲與波形時序控制;

- 模擬輸出層 :每個通道獨立的 DAC 核心(電阻串架構)+ 輸出緩沖,支持電壓 / 電流模式切換,FBx 引腳實現反饋與比較器輸入復用;

- 診斷監控層 :NVM CRC 校驗、通道忙狀態檢測、比較器故障提示,保障輸出穩定性與系統安全性。

2. 典型應用場景:可編程電流源(光學模塊)

(1)應用原理

DACx3204W 通過電壓輸出控制外部 MOSFET,實現大于 250μA 的大電流輸出,FBx 引腳補償 MOSFET 因溫度、老化導致的電壓漂移,GPIO 引腳控制電流啟停,適配光學模塊激光驅動等場景:

- 核心電路 :DAC 輸出電壓(VSET)通過電阻 RSET(如 3Ω)設定電流范圍,外部 MOSFET 擴展輸出電流(0~200mA),FBx 引腳監測 MOSFET 源極電壓,動態調整 DAC 輸出以補償漂移;

- 關鍵參數 :VSET 典型 0.6V(對應 200mA 電流),DAC 代碼通過公式計算(如 DAC63204W 內部 1.21V 基準、1.5× 增益時,代碼 = 0x54A)。

(2)設計要點

- 電源設計 :VDD 引腳并 0.1μF 去耦電容,CAP 引腳并 1.5μF LDO 旁路電容,保障電源穩定性;

- 布局建議 :模擬信號(OUTx/FBx)與數字信號(SCLK/SDA)嚴格分區,參考引腳(VREF)靠近器件放置,減少噪聲串擾;

- 可靠性設計 :通過 NVM 存儲 DAC 配置參數,上電自動加載;GPIO 配置為 Margin-High/Low 觸發,實現電流啟停的可編程壓擺率(如 8μs / 步、8 LSB 步長,總 slew 時間 1.36ms)。

四、電氣特性與設計建議

1. 關鍵電氣特性(典型值,TA=25℃,VDD=5.5V)

| 參數類別 | 指標(電壓輸出模式) | 指標(電流輸出模式,±250μA 范圍) |

|---|---|---|

| 靜態精度 | DAC63204W INL±5 LSB,DNL±1 LSB | INL±1 LSB,DNL±1 LSB,增益誤差 ±1.3% FSR |

| 動態特性 | 建立時間 20μs,輸出噪聲 50μVpp(0.1Hz~10Hz) | 建立時間 60μs,輸出噪聲 150nApp(0.1Hz~10Hz) |

| 電源抑制比 | AC -68dB(50Hz/60Hz) | DC 0.23 LSB/V,AC 0.65 LSB/V |

| 輸出能力 | 短路電流 60mA(VDD=5.5V),輸出阻抗 500kΩ | 輸出 compliance 電壓 400mV,輸出阻抗 60MΩ |

2. 設計建議

(1)電源與參考設計

- 去耦配置 :VDD 引腳就近并 0.1μF 陶瓷電容(X7R 材質),CAP 引腳并 1.5μF 低 ESR 電容,抑制電源噪聲;

- 參考選擇 :使用內部 1.21V 基準時,需設置 EN-INT-REF=1,VREF 引腳并 0.1μF 電容;使用外部基準時,確保基準電壓≤VDD,且基準上電晚于 VDD。

(2)PCB 布局

- 分區隔離 :模擬區域(OUTx/FBx/VREF)與數字區域(SCLK/SDA/GPIO)分開布局,模擬地與數字地單點連接,避免串擾;

- 散熱設計 :DSBGA 封裝底部熱焊盤需連接至大面積接地銅皮,配合散熱過孔,降低結溫(結到環境熱阻 RθJA=81.2℃/W);

- 敏感信號保護 :FBx 引腳布線盡量短,遠離數字時鐘線(SCLK),減少高頻干擾導致的比較器誤觸發。

(3)接口與 NVM 配置

- SPI 讀回 :默認 3 線模式無讀回功能,需在 NVM 中配置 GPIO 為 SDO,讀操作時鐘最高 2.5MHz(FSDO=1 時);

- NVM 編程 :編程前需確保器件未鎖定(DEV-LOCK=0),編程后通過 NVM-RELOAD 驗證數據加載,避免配置丟失;

- PMBus 兼容 :啟用 EN-PMBUS=1 后,支持 Margin High/Low 等 PMBus 命令,需先配置 PMBUS-PAGE 寄存器選擇通道。

-

處理器

+關注

關注

68文章

20286瀏覽量

253285 -

PMBus

+關注

關注

3文章

173瀏覽量

31973 -

引腳

+關注

關注

16文章

2112瀏覽量

55831 -

電壓輸出

+關注

關注

0文章

154瀏覽量

26203 -

GPIO

+關注

關注

16文章

1330瀏覽量

56299

發布評論請先 登錄

基于LNK3204D的1.65W、非隔離、抽頭式Buck轉換器設計

基于LNK3204D PG的1.44W非隔離 Buck 轉換器設計

DACx3204W 12位和10位四路電壓和電流輸出智能DAC數據表

DACx3204?Q1汽車類、12位和10位四路電壓和電流輸出智能DAC數據表

德州儀器DACx3004W智能數模轉換器技術解析

?智能DAC技術解析:DACx3204系列在精密電壓與電流輸出中的應用

DAC53004W 10 位四通道智能 DAC 技術總結

DAC63004W 12 位四通道智能 DAC 技術總結

DAC63204W 12 位四通道智能 DAC 技術總結

DAC53204-Q1 與 DAC63204-Q1 技術文檔總結

DACx300x 系列技術文檔總結

DACx1408 系列八通道高壓輸出 DAC 技術參數與應用總結

DACx0504 系列技術規格與應用總結

DACx0508 系列技術規格與應用總結

DACx3204W 系列技術文檔總結

DACx3204W 系列技術文檔總結

評論