隨著人工智能(AI)、汽車電子和物聯(lián)網(wǎng)(IoT)等應(yīng)用的迅猛發(fā)展,把模擬、數(shù)字、射頻等功能集成于單一芯片的數(shù)模混合信號芯片已成為主流趨勢。此類芯片廣泛滲透至生活與產(chǎn)業(yè)場景中,然而其首次流片成功率通常較純模擬IC/數(shù)字IC低10%-30%。這是由于數(shù)字電路與模擬電路本身在設(shè)計方法學(xué)、驗證難度和工藝要求等方面存在顯著差異。數(shù)字電路通常基于標準單元庫設(shè)計,重點高集成度和功耗優(yōu)化;而模擬電路則依賴PDK,需全面考量器件的物理特性、噪聲、失配等因素。

在數(shù)模混合芯片中,常見的Bug類型包括:

接口與時序問題:例如數(shù)模接口時序失配、信號電平不兼容;復(fù)位信號出現(xiàn)毛刺或異步復(fù)位恢復(fù)時序錯誤,致使寄存器進入亞穩(wěn)態(tài)或控制邏輯異常;芯片上電時序、休眠喚醒流程設(shè)計不當,造成模塊狀態(tài)異常。

電源完整性問題:如同步開關(guān)噪聲、地彈現(xiàn)象,以及電源噪聲耦合至敏感模擬電路,當I/O或核心邏輯同時開關(guān)時,噪聲通過電源/地網(wǎng)絡(luò)傳播,影響供電質(zhì)量。

跨域交互問題:如數(shù)字輔助校準算法或控制邏輯存在缺陷,導(dǎo)致ADC/DAC微分非線性(DNL)與積分非線性(INL)超出規(guī)格等。

設(shè)計與制造失配問題:如前后仿結(jié)果與流片硅后測試結(jié)果不一致,寄生參數(shù)提取不完整或影響評估不足等。

為確保數(shù)字設(shè)計與模擬設(shè)計在同一芯片協(xié)同工作,必須進行復(fù)雜的電路設(shè)計和嚴格的數(shù)模混合仿真硅前驗證。在芯片持續(xù)朝著更高集成度、更先進工藝節(jié)點邁進,且復(fù)雜度呈指數(shù)級增長的背景下,數(shù)模混合仿真驗證工程師面臨著三個關(guān)鍵維度的挑戰(zhàn):

仿真速度與精度的兩難困境:數(shù)模混合芯片中的模擬部分需要晶體管級精度(如SPICE模型),而數(shù)字部分依賴高層次抽象(如Verilog/System Verilog)。不同抽象層次協(xié)同存在技術(shù)難點,仿真耗時極長。全芯片級仿真涉及海量計算,驗證周期長達數(shù)周。為追求速度而在SPICE精度上妥協(xié),可能引發(fā)流片后的災(zāi)難性后果。

數(shù)模接口跨域協(xié)同的復(fù)雜性:數(shù)模接口是功能失效的高頻發(fā)生區(qū)域。模擬信號為連續(xù)的電壓或電流值,而數(shù)字信號為離散的邏輯電平。不同仿真器間需要通過數(shù)模轉(zhuǎn)換和模數(shù)轉(zhuǎn)換接口來實現(xiàn)信號轉(zhuǎn)換。接口精度(分辨率和轉(zhuǎn)換速率)直接影響仿真結(jié)果的保真程度。若設(shè)置過于粗糙,將會引入誤差;若設(shè)置過于精細,則會進一步降低仿真速度。怎樣高效且精準地驗證數(shù)字邏輯與模擬電路之間的交互,是對仿真工具跨域協(xié)同能力的極限挑戰(zhàn)。

時間同步與容量極限的挑戰(zhàn):數(shù)字仿真器采用“事件驅(qū)動”模式,模擬仿真器采用“時間步進”模式。如何讓數(shù)字仿真器在合適的模擬時間點“暫停”以交換數(shù)據(jù),是復(fù)雜的調(diào)度難題。同步不準確會引發(fā)時序錯誤,比如在關(guān)鍵時刻遺漏毛刺或出現(xiàn)建立/保持時間違規(guī)。超大規(guī)模集成電路中上億級晶體管的設(shè)計規(guī)模不斷突破傳統(tǒng)仿真工具的容量上限,全芯片級別的數(shù)模混合仿真變得極為困難。

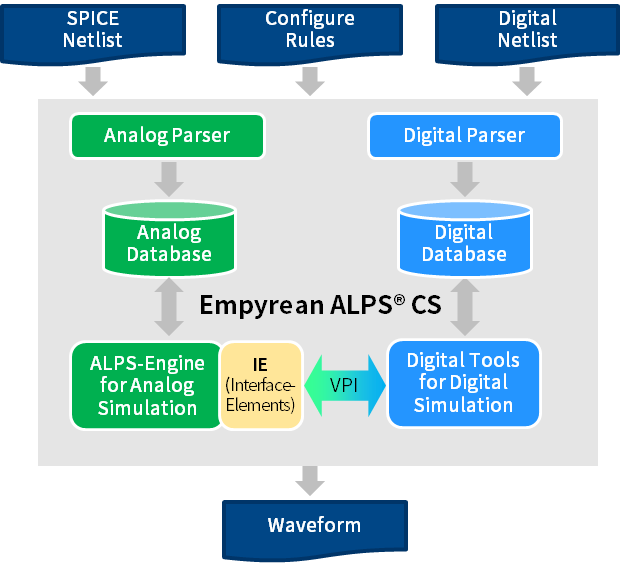

為應(yīng)對上述挑戰(zhàn),華大九天推出了Empyrean ALPS CS(Accurate Large capacity Parallel SPICE Co-Simulation)數(shù)模混合信號仿真工具。該工具基于 SPICE 精度的數(shù)模協(xié)同仿真架構(gòu),通過數(shù)模同步協(xié)同和并行技術(shù)突破等核心能力,大幅度提升數(shù)模混仿效率,為業(yè)界提供了一套在速度、精度與容量維度均具備優(yōu)勢的高效數(shù)模混合仿真驗證解決方案。ALPS CS全面支持涵蓋Verilog、SystemVerilog、VerilogA、VerilogAMS等主流硬件描述語言的前后仿真流程,并且能夠依托LSF集群開展分布式仿真,從而從容應(yīng)對復(fù)雜芯片的仿真驗證挑戰(zhàn)。

核心技術(shù)一:高效的數(shù)模接口跨域協(xié)同與時間同步機制

鑒于當前數(shù)模混合芯片中通常存在模擬域和數(shù)字域的多個反饋環(huán)路,數(shù)字設(shè)計與模擬設(shè)計呈現(xiàn)多層次融合,且相互作用復(fù)雜;ALPS CS通過多項關(guān)鍵技術(shù)研發(fā)以確保混合信號仿真高效性與結(jié)果可靠性:

標準接口兼容:支持借助VPI接口與數(shù)字仿真器實現(xiàn)無縫對接,同時能夠解析Hspice、Spectre等多種模擬網(wǎng)表格式,可輕松融入現(xiàn)有的設(shè)計流程,降低工具替換的遷移成本以及工程師的使用難度。

精準數(shù)模同步技術(shù):運用協(xié)同工作點收斂(Co-simulation Bias Point Convergence)與主從步長協(xié)同(Master-Slave Timestep Coordination)算法,精確掌控數(shù)字事件與模擬信號在交互界面的時序同步,杜絕因步長不匹配而導(dǎo)致的狀態(tài)錯誤,確保跨域仿真的準確性。

智能接口元件(IE):具備內(nèi)置自動化的數(shù)模/模數(shù)信號轉(zhuǎn)換功能,依據(jù)配置精確模擬信號的上升/下降時間以及電壓閾值,簡化跨域驗證設(shè)置流程,有效提升驗證效率。

核心技術(shù)二:基于智能矩陣求解與并行計算的高速仿真引擎

仿真速度是決定驗證效率的關(guān)鍵因素。ALPS CS傳承了ALPS仿真器家族在性能方面的技術(shù)積累,并將其充分運用到數(shù)模混合仿真,通過智能矩陣求解以及高效的并行計算,進一步提高了大規(guī)模數(shù)模混合芯片的驗證效率。

智能矩陣求解算法:與傳統(tǒng)仿真器固定單一的矩陣求解模式不同,ALPS CS內(nèi)置了數(shù)十種差異化的求解策略,具備華大九天獨有的精度無損智能矩陣求解(Smart Matrix Solver)方案。在仿真過程中,該算法可實時動態(tài)分析電路的拓撲結(jié)構(gòu)與電氣特性,自主匹配并切換至最優(yōu)求解方案,從底層提升求解效率。

多核并行技術(shù):與傳統(tǒng)方案無法并行的情況不同,ALPS CS采用業(yè)界領(lǐng)先的并行計算架構(gòu),能夠高效調(diào)度多核CPU的硬件算力,對大規(guī)模電路的仿真任務(wù)進行精細化拆解和分布式并行處理,充分發(fā)揮硬件算力資源潛能。

核心技術(shù)三:數(shù)模混仿中集成大容量/高速/高精度的模擬仿真器ALPS

現(xiàn)代大規(guī)模集成電路的設(shè)計規(guī)模呈爆發(fā)式增長,對仿真工具的容量支持能力提出了極高要求。ALPS CS依托優(yōu)化的內(nèi)存管理機制,在遵循SPICE精度標準的基礎(chǔ)上,能夠穩(wěn)定支持超過1億個器件規(guī)模的超大規(guī)模電路仿真,滿足復(fù)雜芯片設(shè)計的驗證需求。

同時集成高速/高精度模擬仿真器ALPS,采用無損仿真技術(shù),通過直接求解全電路方程,精確復(fù)現(xiàn)晶體管級的物理行為。其在信號傳輸特性、路徑時序參數(shù),及數(shù)模接口響應(yīng)等方面,均可實現(xiàn)與芯片實測高度一致的仿真結(jié)果,為“一次流片成功”提供了核心技術(shù)支撐。

客戶案例應(yīng)用成效

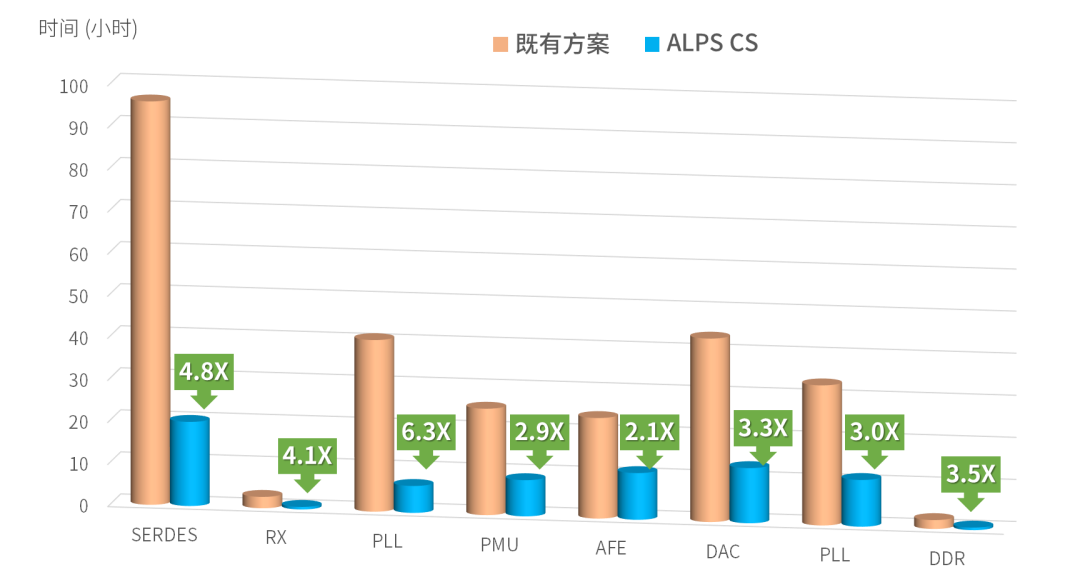

ALPS CS已在多家客戶的應(yīng)用場景中成功落地,彰顯出顯著的速度優(yōu)勢。無論是器件數(shù)量僅25K的小規(guī)模DDR芯片,在進行前仿真時,現(xiàn)有方案需耗時2.1小時,而ALPS CS僅需0.6小時,加速比達到3.5倍;還是器件數(shù)量較多的大規(guī)模高速串行數(shù)據(jù)傳輸SERDES芯片,前仿真時現(xiàn)有方案需95.9小時,ALPS CS僅需20.0小時,加速比高達4.8倍,單次仿真可節(jié)省75.9小時。鎖相環(huán)PLL在前仿真中的加速比可達3倍,后仿真加速比更是高達6.3倍。在其他諸如接收器RX、電源管理PMU等不同類型、不同規(guī)模的芯片仿真中,ALPS CS同樣展現(xiàn)出顯著的加速效果。由此可見,ALPS CS能夠大幅縮短單次仿真的時間,進而縮短整體IC研發(fā)周期。

總結(jié)

ALPS CS的技術(shù)優(yōu)勢與應(yīng)用價值

Empyrean ALPS CS依托在仿真速度、精度和容量這三大核心維度的突破性技術(shù)革新,搭建起一套高效且可靠的數(shù)模混合信號驗證體系。它借助高效的數(shù)模接口跨域協(xié)同與時間同步機制,充分確保數(shù)字仿真器和模擬仿真器實現(xiàn)“順暢”通信。憑借獨有的精度無損智能矩陣求解以及高效多核并行技術(shù),在保證速度的同時不降低精度;通過優(yōu)化內(nèi)存管理,支持超1億級數(shù)量的器件規(guī)模仿真。總體而言,ALPS CS的通過仿真速度提升,將單次混合仿真驗證時長從“周”縮短至“天”。ALPS CS為復(fù)雜數(shù)模混合芯片設(shè)計的高效驗證提供關(guān)鍵的EDA工具支持,尤其能夠助力面臨先進工藝挑戰(zhàn)的芯片設(shè)計團隊突破數(shù)模混合驗證的瓶頸,大幅縮短驗證周期,加速大規(guī)模數(shù)模混合芯片產(chǎn)品成功推向市場。

北京華大九天科技股份有限公司(簡稱“華大九天”)成立于2009年,一直聚焦于EDA工具的開發(fā)、銷售及相關(guān)服務(wù)業(yè)務(wù),致力于成為全流程、全領(lǐng)域、全球領(lǐng)先的EDA提供商。

華大九天主要產(chǎn)品包括全定制設(shè)計平臺EDA工具系統(tǒng)、數(shù)字電路設(shè)計EDA工具、晶圓制造EDA工具、先進封裝設(shè)計EDA工具和3DIC設(shè)計EDA工具等軟件及相關(guān)技術(shù)服務(wù)。其中,全定制設(shè)計平臺EDA工具系統(tǒng)包括模擬電路設(shè)計全流程EDA工具系統(tǒng)、存儲電路設(shè)計全流程EDA工具系統(tǒng)、射頻電路設(shè)計全流程EDA工具系統(tǒng)和平板顯示電路設(shè)計全流程EDA工具系統(tǒng);技術(shù)服務(wù)主要包括基礎(chǔ)IP、晶圓制造工程服務(wù)及其他相關(guān)服務(wù)。產(chǎn)品和服務(wù)主要應(yīng)用于集成電路設(shè)計、制造及封裝領(lǐng)域。

華大九天總部位于北京,在南京、成都、深圳、上海、香港、廣州、北京亦莊、西安和天津等地設(shè)有全資子公司,在武漢、廈門、蘇州等地設(shè)有分支機構(gòu)。

-

集成電路

+關(guān)注

關(guān)注

5462文章

12653瀏覽量

375487 -

模擬電路

+關(guān)注

關(guān)注

126文章

1609瀏覽量

105716 -

仿真

+關(guān)注

關(guān)注

55文章

4529瀏覽量

138599 -

華大九天

+關(guān)注

關(guān)注

5文章

119瀏覽量

13945

原文標題:從周到天:華大九天ALPS CS 通過數(shù)模域同步協(xié)同和并行計算技術(shù)突破提升數(shù)模混合仿真效率

文章出處:【微信號:華大九天,微信公眾號:華大九天】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

合見工軟與華大九天攜手共建國產(chǎn)EDA數(shù)模混合信號設(shè)計與仿真解決方案

利用Multisim和華大九天EDA工具進行比較器設(shè)計

中國EDA戰(zhàn)略研討會暨華大九天成立大會召開

華大九天首創(chuàng)模擬電路異構(gòu)仿真系統(tǒng)

關(guān)于華虹宏力與華大九天用國產(chǎn)EDA工具助力IP設(shè)計的介紹和說明

EDA企業(yè)華大九天正式啟動上市

華大九天與概倫電子,誰將真正成為國產(chǎn)EDA第一股?

國內(nèi)誕生EDA第一股,華大九天上市獲批

華大九天是國企嗎 華大九天eda什么水平

華大九天是做什么的 華大九天上市時間

華大九天屬于哪個板塊 華大九天發(fā)展前景

合見工軟與華大九天攜手共建國產(chǎn)EDA數(shù)模混合信號設(shè)計與仿真解決方案

芯華章與華大九天推出數(shù)模混合仿真解決方案,引領(lǐng)EDA生態(tài)新篇章

華大九天ALPS模擬仿真器的Snapshot功能解析

華大九天ALPS CS技術(shù)提升數(shù)模混合信號仿真效率

華大九天ALPS CS技術(shù)提升數(shù)模混合信號仿真效率

評論