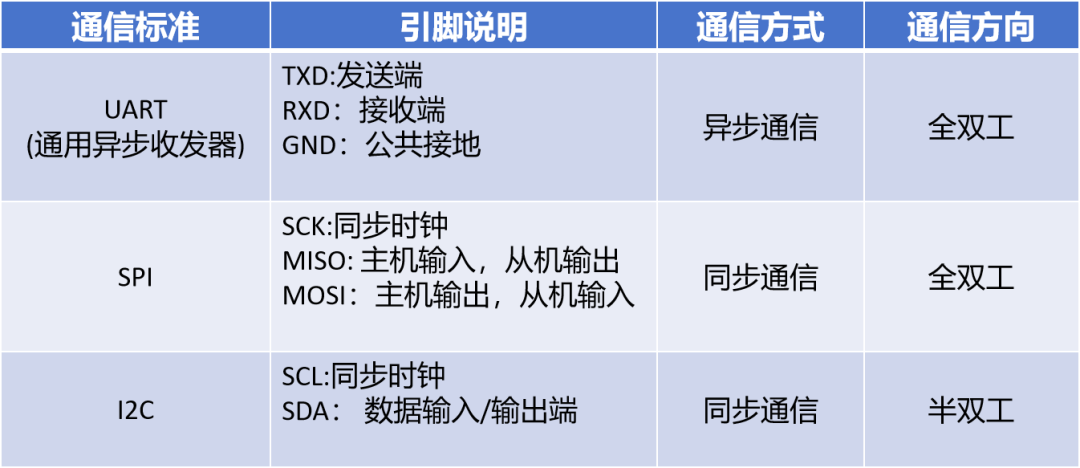

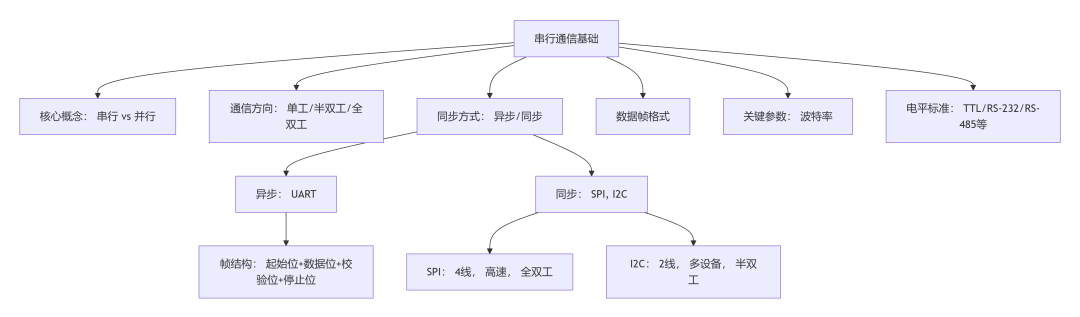

串行通信是電子設備中數據交換的基石。最常見的串行通信協議有UART,SPI,I2C等。

本文將介紹串行通信相關的基礎知識。為后面用FPGA實現這些串行協議的案例做準備。

并行通信和串行通信

并行通信:數據各個位用多條數據線同時進行傳輸 (傳輸速度快,但占用引腳資源多)。

串行通信:數據分成一位一位的形式在一條數據線上逐個傳輸(通信線路簡單,占用資源少,但速度慢)。

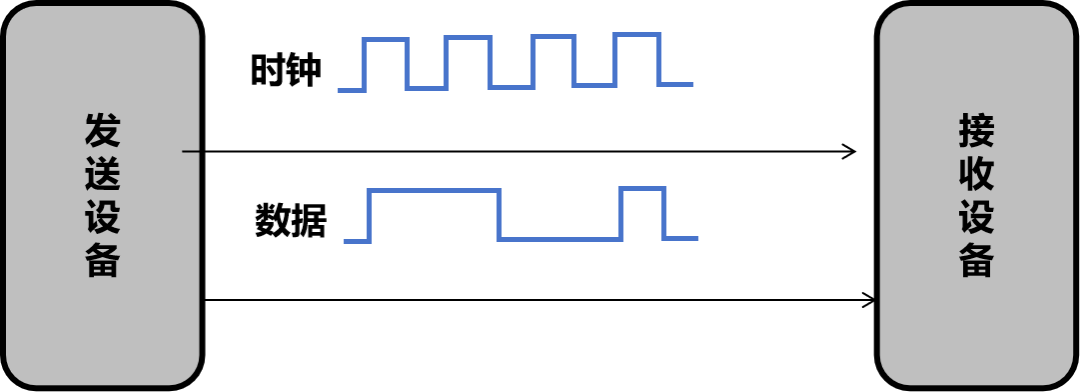

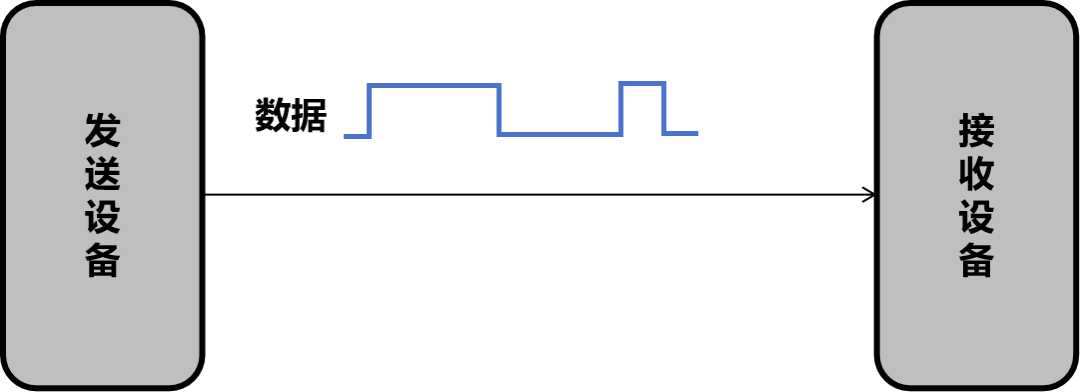

同步通信和異步通信

同步通信:帶時鐘同步信號的數據傳輸,發送方和接收方在同一時鐘的控制下同步傳輸數據。

異步通信:不帶時鐘同步信號的數據傳輸,發送方和接收方使用各自的時鐘控制數據的發送和接收過程。

在沒有時鐘同步的情況下,收發雙方約定好 ,比如發送方在每秒傳輸 115200個 數據,那么,接收方也在每秒接收 115200個 數據。

異步通信需要起始位和停止位來界定一個數據幀。雙方時鐘誤差累積會導致誤碼,故單次傳輸數據量不宜過大(通常≤10位)。

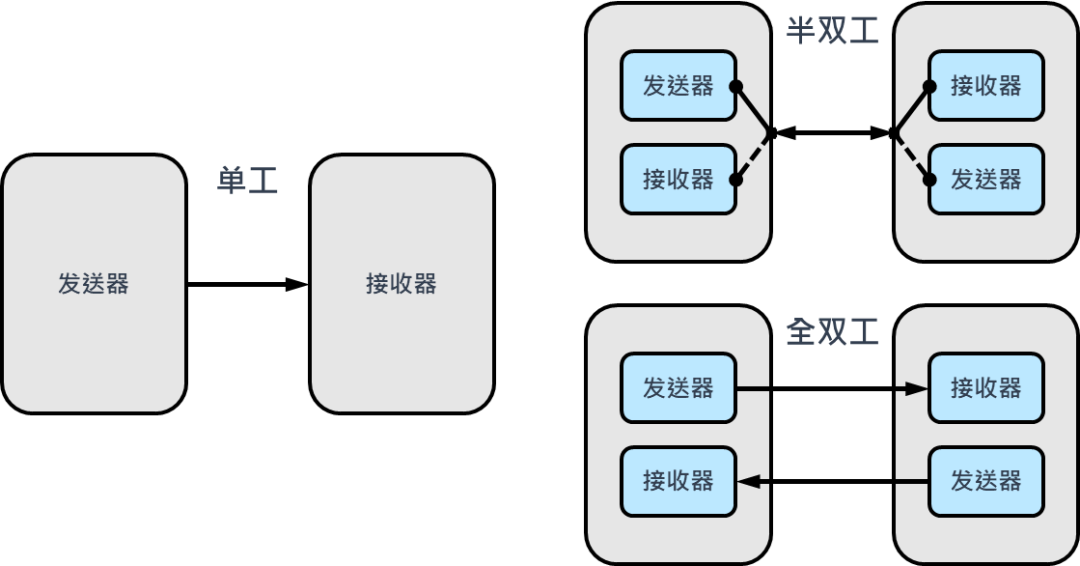

單工、半雙工、全雙工

串行通信的傳輸方向有如下三種:

單工通信:數據只能單向傳輸;

半雙工通信:數據可以雙向傳輸,但不能同時進行(如I2C);

全雙工通信:數據可以同時雙向傳輸(如UART、SPI)。

常見的串行通信接口:

前面已經發布過FPGA實現SPI協議的相關案例,有興趣可以參考:

05-基于FPGA和LTC2308的數字電壓表設計-用FPGA實現SPI協議通訊

04-基于FPGA和LTC2308的數字電壓表設計-SPI協議詳解

近期將發布不同FPGA開發板上的串口應用案例的設計。

后期還將發布基于FPGA的HDMI發送器(ADV7513)的I2C協議控制相關的設計,敬請期待。

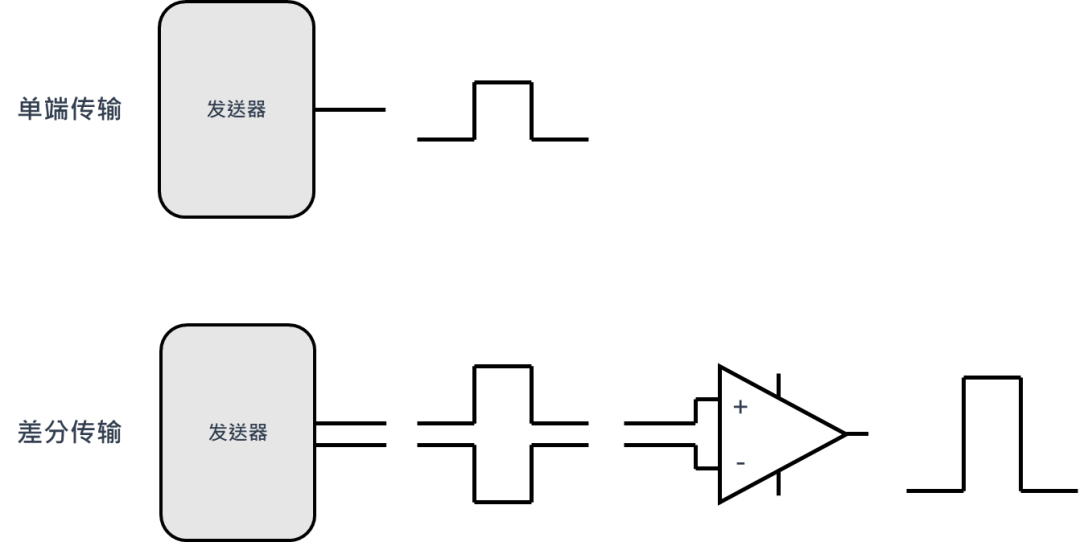

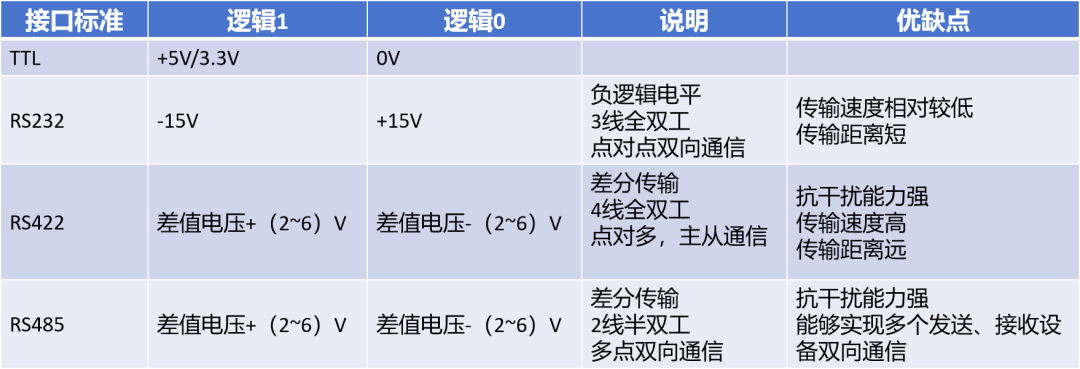

單端傳輸和差分傳輸

單端傳輸:用信號線對GND的電壓值來表示邏輯"0"和"1";

差分傳輸:用兩根信號線來傳輸一路信號,兩根信號線上傳輸的信號幅值相等,相位差為180°(極性相反),用它們的差值來表示邏輯"0"和"1"。

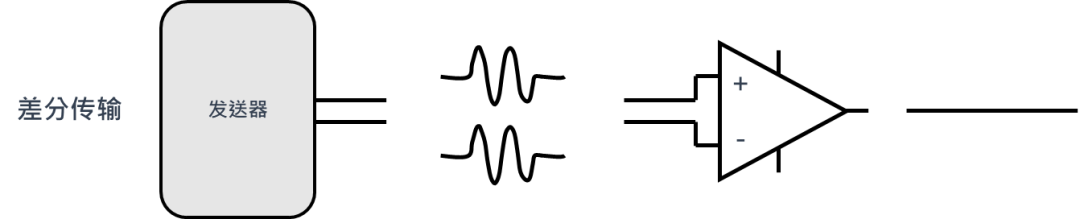

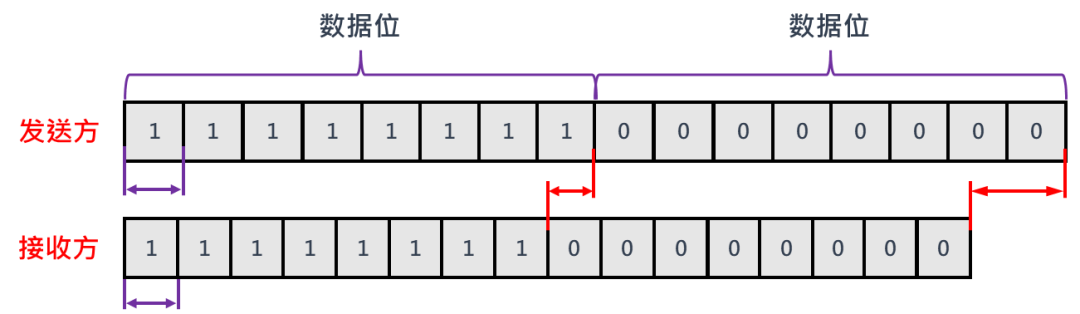

差分傳輸利于消除共模干擾(共模干擾是指在導線與地之間產生一個與有用信號同向的無用電信號,如下所示)。

從兩信號線差值可知引入的噪聲并不會影響接收端判斷傳輸的數據。

UART協議

UART 是universal asynchronous receiver-transmitter的縮寫,是一種采用全雙工異步串行通信的通信方式。

UART傳輸格式

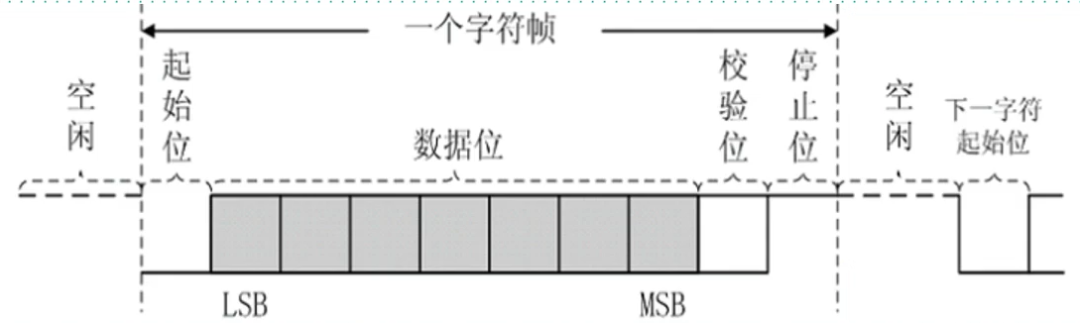

UART協議層的通信協議數據格式如下:

空閑:高電平(總線空閑);

起始位:低電平;

數據位:先發低位,后發高位,數據位可以是5位,6位,7位,8位(數據位具體是多少位由串口收發雙方提前約定好);

校驗位:分奇校驗和偶校驗,該位可省略;

停止位:1位、1.5位、2位可選。

UART傳輸速率

串口通信的速率用波特率表示,它表示每秒傳輸的符號數,單位是Bd。

因為UART編碼方式(采用NRZ)非常簡單,一個符號就是一個比特。所以,當人們說“串口速率為115200”時,實際指的是波特率為115200 Baud,同時比特率也是115200 bps。

常用的波特率有9600、19200、38400、57600 、115200。

串口傳輸的位周期

位周期代表串口傳輸一個bit所占用的時間。假設系統時鐘是50MHz,波特率是115200Bd,那么串口發送和接收時,數據的每個位將占用1/115200=8.68us,每個位占用50000000/115200 ≈ 434個系統時鐘周期。

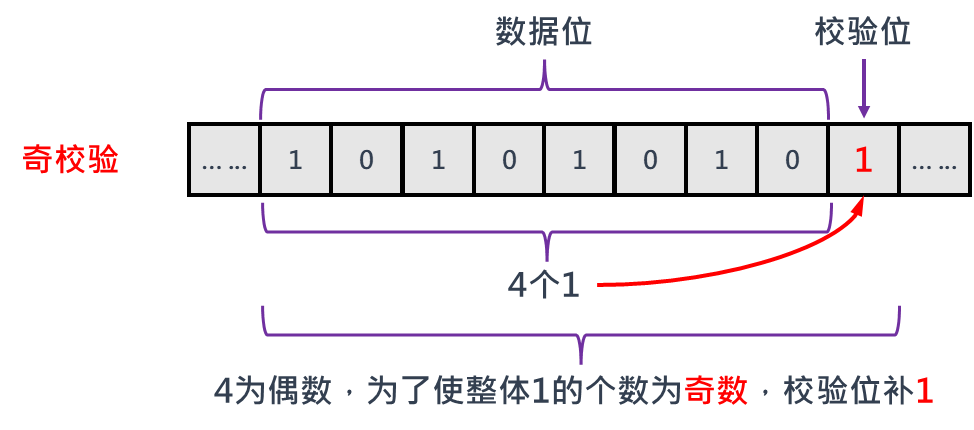

奇偶校驗

奇偶校驗(Parity Check)是一種驗證數據傳輸正確與否的方法。

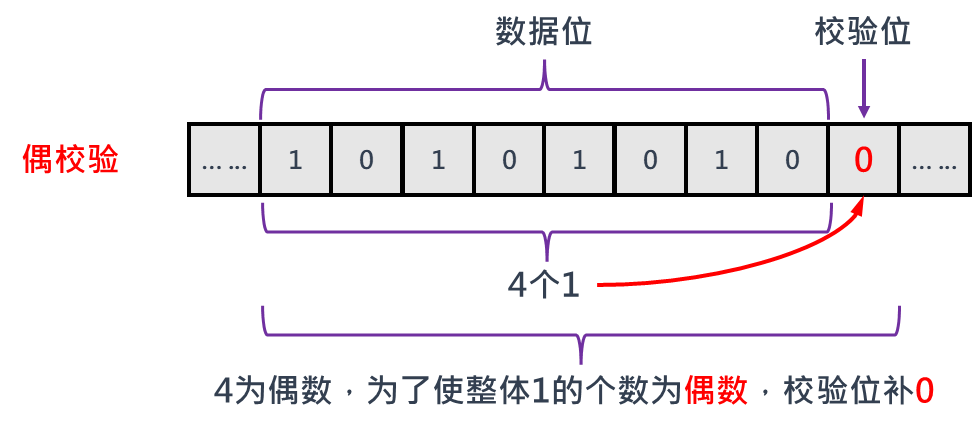

奇校驗(Odd Parity):通過設置校驗位為"1"或"0",讓傳輸的數據(包含校驗位)中"1"的個數為奇數。

偶校驗(Even Parity):通過設置校驗位為"1"或"0",讓傳輸的數據(包含校驗位)中"1"的個數為偶數。

以發送數據"10101010"為例(數據中包含4個"1"),奇校驗時校驗位應設置為"1":

偶校驗時校驗位應設置為"0":

奇偶校驗的缺點:無法檢測雙位錯誤;沒辦法確定哪一位出錯;不能修正。所以一般應用中有的人會直接舍棄校驗位。

消除累計誤差

UART發送方和接收方使用各自的時鐘,在這種情況下容易產生累計誤差。比如發送方首先發送1-bit數據,它計時了1s后開始發送第二個1-bit數據,可是接收方在接收第一個1-bit數據時,它只計時了0.9s,發送方在發送完一個8-bit數據后,會產生誤差;如果第二次發送數據時又緊接著發,那誤差累計就會導致誤差越來越大。

為了消除累計誤差,UART一次只能發送一個字節的數據,不能連續發送多個字節數據。

電平轉換

UART是通信協議,它定義了數據的格式。UART通常以 TTL/CMOS 電平在芯片之間傳輸。其邏輯 1 是 3.3V/5V,邏輯 0 是 0V。它只在板級或極短距離內有效,因為 TTL 電平抗干擾能力差,傳輸距離短。

想要UART通信抗干擾能力強,傳輸距離變遠,在物理層上需要采用RS-232, RS-422, RS-485標準進行UART信號傳輸。

FPGA 的 UART 模塊(TTL 電平)不能直接接 RS-232 或 RS-422/485 網絡,需要一個 “電平轉換芯片” 作為橋梁。

就拿DE2-115開發板上的RS232接口來說,RS232的電平使用負邏輯電平,和FPGA 的電平(TTL)不一樣,需要中間的轉換芯片,DE2-115開發板采用的是ZT3232LEEY,將+-15v的邏輯電平轉換為TTL電平。

RS-232 、 RS-422和RS-485的物理接口一般采用DB9接口或者鳳凰頭接口(接口形式不固定,也有其他物理接口比如網口等)。

DB9接口:

鳳凰頭接口:

這是 RS-232、RS-422 和 RS-485 標準在最常見的 DB9 接口上的物理接口引腳定義表格:

但DB9的體積比較大,為了節省開發板的空間,現在大多用USB口替代,比如C5G和TSP開發板,分別用FT232R和CP2102N來作為USB電平和TTL電平之間的轉換,以及uart協議和USB協議之間的轉換。

具體流程如下:

FPGA 仍通過 UART (TTL) 發送數據。

數據發送給 USB轉UART芯片。

該芯片將簡單的 UART 協議數據打包成復雜的 USB 協議數據包。

電腦接收到 USB 數據包后,需要安裝驅動程序,將其解包還原成 UART 數據,并在操作系統中創建一個虛擬串口(如 COM3)。

這樣,上位機軟件就可以像操作傳統串口一樣,通過這個虛擬串口與 FPGA 通信了。

所以,當我們在設計FPGA串口收發的時候,只需要按UART協議收發數據,CH340G、FT232R和CP2102N芯片會幫我們完成uart與外部USB設備之間信號轉換。

TSP開發板的USB轉UART橋接芯片采用CP2102N,C5G開發板采用FT232R,DE10-Standard開發板采用CH340G,DE23-Lite開發板采用FT2232H。

后續即將發布:

2-基于TSP 開發板的FPGA 串口通信設計 (CP2102N)

3-基于DE10-Standard 開發板的FPGA 串口通信設計 (CH340G)

4-基于DE23-Lite 開發板的FPGA 串口通信設計 (FT2232H)

5-基于C5G 開發板的FPGA 串口通信設計 (采用Nios II控制Intel Uart IP進行串口收發)

本文知識點總結如下:

-

FPGA

+關注

關注

1656文章

22317瀏覽量

631088 -

I2C

+關注

關注

28文章

1547瀏覽量

130578 -

uart

+關注

關注

22文章

1305瀏覽量

106186 -

同步通信

+關注

關注

0文章

29瀏覽量

9457 -

串行通信

+關注

關注

4文章

604瀏覽量

37008

原文標題:1-串行通信基礎知識

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

串行通信相關的基礎知識

串行通信相關的基礎知識

評論