引言

在高速串行通信中,CDR(Clock-Data-Recovery)時(shí)鐘與數(shù)據(jù)恢復(fù)功能起著關(guān)鍵作用。CDR電路可以從數(shù)據(jù)流中同時(shí)提取出數(shù)據(jù)和時(shí)鐘,鏈路上不再需要伴隨信號發(fā)送隨路時(shí)鐘,大量節(jié)省IO資源和布線成本,并且完全消除在高速通訊中因數(shù)據(jù)和時(shí)鐘相位偏差導(dǎo)致的傳輸錯(cuò)誤,對長距離傳輸友好;采用了CDR電路的系統(tǒng),數(shù)據(jù)收發(fā)兩端在時(shí)鐘系統(tǒng)上可以完全解耦,帶來非常大的系統(tǒng)靈活性。

智多晶FPGA通過普通邏輯和IO資源實(shí)現(xiàn)了CDR應(yīng)用的支持,在上限200~250Mbps[2]速率范圍內(nèi)提供了更為有力的通訊技術(shù)方案。

Bit CDR Demo介紹

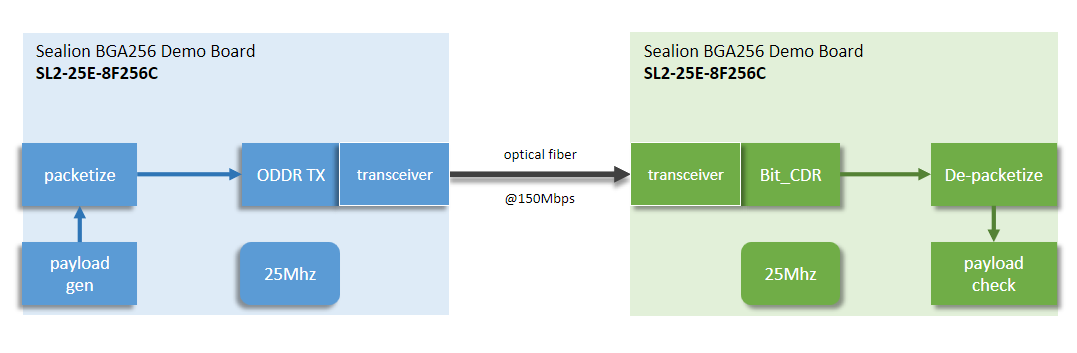

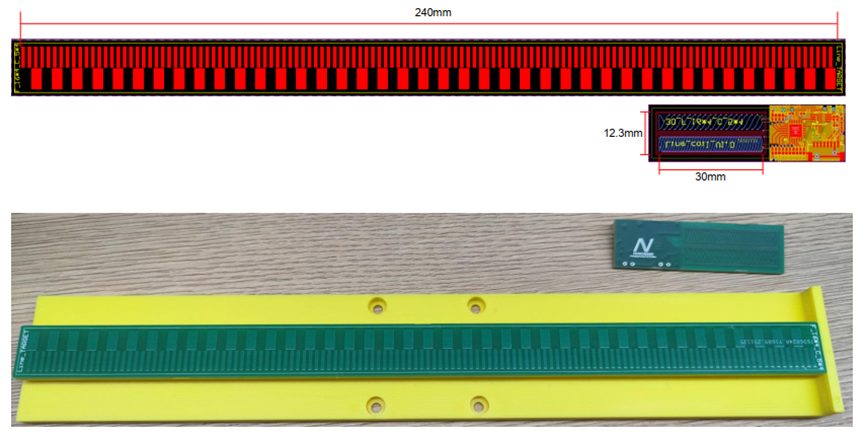

Bit_CDR Demo中的核心模塊CDR基于過采樣原理,在Sealion器件上可以支持到200Mbps。Demo使用了兩張基于Sealion 25K FPGA的電路板,其中一張板做發(fā)送端,另一張板作為接收端。開發(fā)板上各有一對雙波長光模塊相互作為收發(fā),光模塊之間使用20KM的光纖連接,模擬真實(shí)應(yīng)用環(huán)境。兩張開發(fā)板工作于自己晶振產(chǎn)生的獨(dú)立時(shí)鐘,數(shù)據(jù)速率定為150Mbps。

Demo系統(tǒng)示意框圖

考慮到Demo演示的合理性,整體技術(shù)方案上選擇以IEEE802.3協(xié)議為框架來搭建。使用IEEE802.3協(xié)議,可以保證產(chǎn)生的串行數(shù)據(jù)在傳輸過程中可以保持DC平衡,編碼后不會出現(xiàn)長0和長1碼,還具備較強(qiáng)的錯(cuò)誤識別能力。由于IEEE802.3協(xié)議框架在應(yīng)用上的通用性,demo本身也具備足夠的應(yīng)用參考價(jià)值。

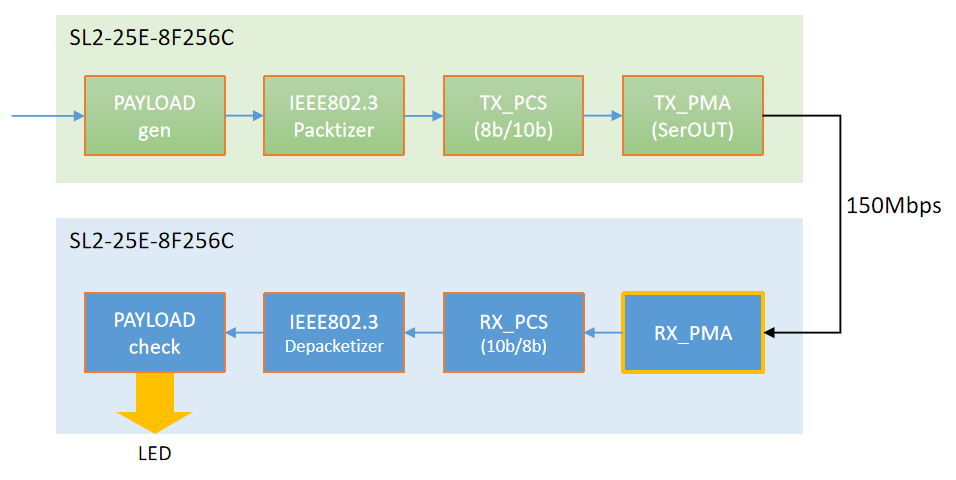

Bit_CDR_DEMO技術(shù)框圖

發(fā)送端:數(shù)據(jù)生成模塊自動(dòng)生成有規(guī)律的報(bào)文數(shù)據(jù);報(bào)文經(jīng)過以太網(wǎng)IEEE802.3協(xié)議模塊打包;在TX_PCS模塊進(jìn)行8b10b編碼;在TX_PMA模塊以150Mbps速率串化輸出至光模塊。

接收端:光模塊接收下來的差分信號,在RX_PMA模塊中完成信號識別和采樣、數(shù)據(jù)窗的同步判斷、10bit并行數(shù)據(jù)和時(shí)鐘的恢復(fù);在RX_PCS模塊中完成8b10b解碼;在以太網(wǎng)IEEE802.3協(xié)議模塊進(jìn)行payload解包,最后在PAYLOAD check模塊對解出的數(shù)據(jù)包進(jìn)行規(guī)律正確性檢查并輸出報(bào)錯(cuò)。

Demo效果

在上述的TX-RX環(huán)路平臺上,我們通過錯(cuò)誤統(tǒng)計(jì)計(jì)數(shù)器和計(jì)時(shí)器,對誤碼率進(jìn)行了簡單的實(shí)測和評估,誤碼率低于10^-12。

Demo特性

采用過采樣方式實(shí)現(xiàn)CDR功能

能夠恢復(fù)數(shù)據(jù)和時(shí)鐘

可靈活支持串并轉(zhuǎn)換數(shù)據(jù)格式

串并轉(zhuǎn)換特征碼(comma word)可配置

通過IEEE802.3鏈路驗(yàn)證

支持鏈路狀態(tài)檢測和管理控制

誤碼率低于10^-12 [1]

應(yīng)用場景

200M~250Mbps[2]速率以內(nèi)的單lane通訊。

工業(yè)設(shè)備子卡與主板之間的多節(jié)點(diǎn)背板通訊(M-LVDS)

長距離通訊光端機(jī)

應(yīng)用中針對傳輸phy芯片的cost-down

[注]

[1]基于20Km光纖和150Mbps速率條件下測得。

[2]速率上限取決于器件。

-

FPGA

+關(guān)注

關(guān)注

1662文章

22469瀏覽量

638126 -

串行通信

+關(guān)注

關(guān)注

4文章

608瀏覽量

37194 -

時(shí)鐘系統(tǒng)

+關(guān)注

關(guān)注

1文章

133瀏覽量

12982

原文標(biāo)題:“芯”技術(shù)分享 | 智多晶Bit_CDR Demo

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

什么使集成CDR的誤碼率有益?

國產(chǎn)智多晶FPGA介紹及應(yīng)用

AT32F415 Audio 24bit實(shí)例demo

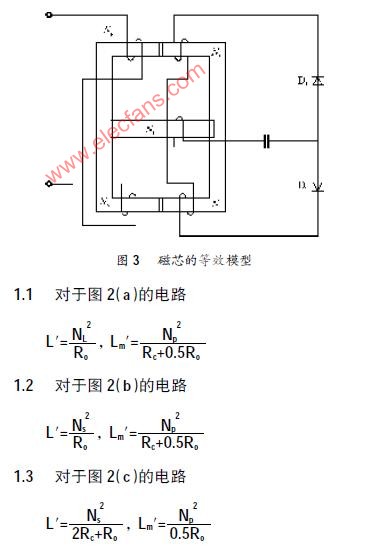

基于磁集成的CDR電路

HASS試驗(yàn)對CDR的PPM容忍度要求

多晶硅生產(chǎn)流程是什么_單晶硅與多晶硅的區(qū)別

多晶硅太陽能板品牌_多晶硅太陽能板價(jià)格

Demo介紹UART 9bit通信的同步幀方式

LTC6115 Demo Circuit - Current and Voltage Sensor Monitor Circuit for 16-Bit ?Σ ADC

智多晶DDR Controller介紹

智多晶AXI視頻通訊DEMO方案介紹

智多晶CPRI協(xié)議DEMO介紹

智多晶Bit_CDR Demo介紹

智多晶Bit_CDR Demo介紹

評論