核心概述

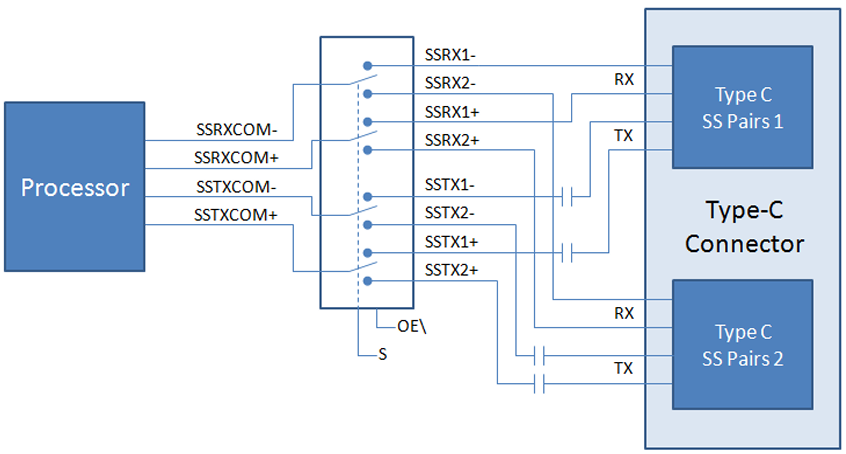

FSW6860是四方杰芯研發的混合信號切換芯片,集成 “五通道高速差分信號 2:1 復用 / 解復用” 與 “兩路低速 SPDT 模擬開關” 功能,專為 USB Type-C 接口的多設備信號共享設計。其高速通道滿足 USB 3.1 Gen 1(5Gbps)速率需求,低速通道適配音頻等低速模擬信號,兼具高信號完整性與低功耗特性,適合對通道集成度、速率兼容性有高要求的場景。

關鍵特性(高速 / 低速通道對比)

| 特性分類 | 高速通道(五通道差分 2:1) | 低速通道(兩路 SPDT) | 備注 |

|---|---|---|---|

| 通道數量 / 類型 | 5 組差分通道,2:1 Mux/DeMux | 2 組單刀雙擲(SPDT) | 高速側重高速數字信號,低速側重模擬信號 |

| 核心帶寬 | 7.5GHz@-3dB | 600MHz@-3dB | 高速支持 USB 3.1 Gen 1,低速支持音頻 / 低速數據 |

| 隔離度 | -39dB@5GHz | -100dB@100KHz | 低速通道隔離性能更優,適配敏感模擬信號 |

| 串擾 | -41dB@5GHz | -97dB@100KHz | 同上 |

| 導通電阻(Typ.) | 6.5Ω(VIS=1.5V,ION=8mA) | 1.5~3.9Ω(分電壓區間) | 低速通道導通電阻隨信號電壓變化更明顯 |

| 目標應用 | USB 3.1、PCIe、FPD Link | 音頻信號切換 | 功能場景明確區分 |

| ESD 耐受 | 2kV HBM | 未單獨標注(默認兼容) | 高速通道可靠性參數明確 |

核心引腳配置(表格)

| 引腳號 | 引腳名稱 | 信號類型 | 關鍵描述 |

|---|---|---|---|

| 5-6 | COMAN/COMAP | I/O | 高速通道 1 的公共端差分信號對(負 / 正) |

| 7-8 | COMBN/COMBP | I/O | 高速通道 2 的公共端差分信號對(負 / 正) |

| 9-10 | COMCN/COMCP | I/O | 高速通道 3 的公共端差分信號對(負 / 正) |

| 11-12 | COMDN/COMDP | I/O | 高速通道 4 的公共端差分信號對(負 / 正) |

| 14-15 | COMEN/COMEP | I/O | 高速通道 5 的公共端差分信號對(負 / 正) |

| 16 | SEL | I | 高速通道選擇:L = 公共端→A 端口,H = 公共端→B 端口 |

| 17 | _EN | I | 總使能引腳,低電平有效;高電平時所有通道高阻 |

| 2 | S11 | I | 低速通道 1 選擇:L=A1→B01,H=A1→B11 |

| 46 | S12 | I | 低速通道 2 選擇:L=A2→B02,H=A2→B12 |

| 48 | A1 | I/O | 低速通道 1 的公共信號端 |

| 47 | B01 | I/O | 低速通道 1 的常閉端口 |

| 4 | B11 | I/O | 低速通道 1 的常開端口 |

| 43 | A2 | I/O | 低速通道 2 的公共信號端 |

| 42 | B02 | I/O | 低速通道 2 的常閉端口 |

| 44 | B12 | I/O | 低速通道 2 的常開端口 |

| 3/35/45 | VCC1/VCC3/VCC2 | Power | 電源正極(1.8~4.5V,多組供電增強穩定性) |

| 13/24/36 | GND2/GND3/GND4 | Ground | 電源地(多組接地降低干擾) |

真值表(通道控制邏輯)

高速通道控制(SEL + _EN)

| _EN(總使能) | SEL(通道選擇) | 高速通道狀態(公共端 COM ? 端口) |

|---|---|---|

| High(關斷) | X(任意) | 所有高速通道呈 Hi-Z(高阻態) |

| Low(使能) | Low | COM ? A 端口(DAxP/DAxN) |

| Low(使能) | High | COM ? B 端口(DBxP/DBxN) |

注:x=0~4,對應 5 組高速差分信號。

低速通道控制(S11/S12 + _EN)

| _EN(總使能) | S11(低速通道 1) | 低速通道 1 狀態(A1 ? 端口) | S12(低速通道 2) | 低速通道 2 狀態(A2 ? 端口) |

|---|---|---|---|---|

| High(關斷) | X | Hi-Z | X | Hi-Z |

| Low(使能) | Low | A1 ? B01(常閉) | Low | A2 ? B02(常閉) |

| Low(使能) | High | A1 ? B11(常開) | High | A2 ? B12(常開) |

電氣參數(分高速 / 低速通道)

高速通道電氣參數(TA=25℃,VCC3=3V)

| 參數名稱 | 符號 | 測試條件 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|---|

| 靜態電流 | IQ | SEL=0/VCC,_EN=0 | - | - | 28 | uA |

| 關斷電流 | IPO | SEL=0/VCC,_EN=VCC | - | - | 1 | uA |

| 輸入高電平 | VIH | VCC=1.8~4.5V | 1.6 | - | - | V |

| 輸入低電平 | VIL | VCC=1.8~4.5V | - | - | 0.4 | V |

| 導通電阻 | RON_HS | VIS=1.5V,ION=8mA | - | 6.5 | - | Ω |

| 通道間電阻匹配 | RMATCH | VIS=0~1.2V,ION=8mA | - | 0.1 | - | Ω |

| 使能時間 | tEN | RL=50Ω,CL=0pF,VIS=0.6V | - | 80 | 150 | uS |

| 關斷時間 | tDIS | RL=50Ω,CL=0pF,VIS=0.6V | - | 40 | 250 | nS |

| 開啟時間 | tON | RL=50Ω,CL=0pF,VIS=0.6V | - | 400 | 1200 | nS |

| 關閉時間 | tOFF | RL=50Ω,CL=0pF,VIS=0.6V | - | 130 | 800 | nS |

| 先斷后合時間 | tBBM | RL=50Ω,CL=0pF,VIS=0.6V | - | 250 | 500 | nS |

| -3dB 帶寬 | BW-3dB | RL=50Ω,CL=0pF,0dBm 信號 | - | 7.5 | - | GHz |

| 隔離度 | Off | RL=50Ω,f=5GHz,VIS=0.2VPP | - | -39 | - | dB |

| 串擾 | XTALK | RL=50Ω,f=5GHz,VIS=0.2VPP | - | -41 | - | dB |

| 插入損耗 | IL | f=5GHz | - | -1.48 | - | dB |

低速通道電氣參數(TA=25℃,VCC1/VCC2=3.3V)

| 參數名稱 | 符號 | 測試條件 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|---|

| 靜態電流 | ICC | IA=0,VSEL=0/VCC | - | - | 2.0 | uA |

| 輸入高電平 | VIH | VCC=3.3~5.5V | 1.6 | - | - | V |

| 輸入高電平 | VIH | VCC=1.5~3.3V | 1.4 | - | - | V |

| 輸入低電平 | VIL | VCC=3.3~5.5V | - | - | 0.6 | V |

| 輸入低電平 | VIL | VCC=1.5~3.3V | - | - | 0.4 | V |

| 導通電阻(V=4.0~5.5V) | RON4 | IA=30mA | - | 1.5 | 1.8 | Ω |

| 導通電阻平坦度(V=4.0~5.5V) | RFLAT4 | IA=30mA | - | 0.3 | - | Ω |

| 開啟 / 關閉時間 | TON/TOFF | VA=1.5V,CL=35pF,RL=50Ω | - | 200 | - | nS |

| 先斷后合時間 | TBBM | VA=1.5V,CL=35pF,RL=50Ω | - | 500 | - | nS |

| -3dB 帶寬 | BW | RL=50Ω,CL=0pF | - | 600 | - | MHz |

| 總諧波失真 | THD | 20Hz~20KHz,VA=600mVp-p,RL=32Ω | - | -80 | - | dB |

應用場景

USB Type-C 生態:USB-C 集線器、擴展塢,實現多設備(如 U 盤、顯示器)共享一個 USB-C 接口;

臺式機 / 筆記本 PC:內部 USB 3.1 信號與低速音頻信號的混合切換(如主機與外設間的信號路由);

服務器 / 存儲區域網絡:PCI Express 背板的高速信號共享,或存儲設備的 I/O 端口切換;

其他高速接口:FPD LinkII/III 視頻信號(如車載顯示、工業攝像頭)與低速控制信號的協同切換。

PCB 設計要點

封裝優先0402或0603,嚴禁使用 0805 或 C-packs(避免寄生參數影響高速信號);

容值推薦0.1μF,且同一差分對的電容容值需完全匹配(減少信號 skew);

放置位置:僅能在開關單側邊放置(避免隔斷直流偏置電壓),若系統共模電壓 > 2V,需額外提供 < 2V 的 VBIAS 偏置。

信號布線:

高速差分信號(USB 3.1、PCIe)需等長、平行、緊密耦合,線距控制在 5~8mil,阻抗匹配 50Ω;

低速音頻信號遠離高速信號和數字控制引腳(SEL、S11/S12),避免串擾。

電源與接地:

多組 VCC 引腳(VCC1/VCC2/VCC3)旁需各放置 1 顆0.1μF 去耦電容,接地路徑最短;

多組 GND 引腳(GND2/GND3/GND4)需均連接到完整地平面,降低地彈噪聲。

3.8 封裝與包裝信息

封裝類型:QFN6x6-48L(6mm×6mm,48 引腳無鉛方型扁平封裝,底部帶裸露熱焊盤,增強散熱);

包裝方式:卷帶包裝(Tape and Reel),每卷3000 顆;

頂部絲印:格式為 “AXX YYWW”,其中 YY = 年份(如 24=2024)、WW = 周數(01~53)、AXX = 內部 ID 碼。

版本修改記錄

| 版本號 | 修訂內容 |

|---|---|

| first edition | 初始版本 |

| V1.0 | 1. 更新第 2-3 頁 “引腳配置”;2. 更新第 6 頁 “電氣特性” 的測試條件及 “TX/RX 導通電阻” |

| V2.0 | 1. 更新第 2 頁 “引腳配置” |

| V3.0 | 1. 更新第 2 頁 “訂貨信息” |

| V4.0 | 1. 更新第 6 頁 “電氣特性”;2. 更新第 1 頁 “關鍵特性” |

| V5.0 | 1. 更新第 11 頁 “重要聲明與免責條款” |

4. 關鍵問題

問題 1:FSW6860 的 “高速通道” 與 “低速通道” 在功能定位、參數設計上為何差異顯著?分別適配哪些具體場景?

答案:差異源于 “信號類型與速率需求的本質不同”,具體設計邏輯與場景適配如下:

功能定位差異:

高速通道:針對USB 3.1 Gen 1(5Gbps)、PCIe等高速數字差分信號,核心訴求是 “低損耗、高帶寬、抗串擾”,因此設計為五通道集成(滿足多組高速信號同步切換),帶寬達 7.5GHz,隔離度 - 39dB@5GHz,確保高速信號完整性;

低速通道:針對音頻、低速控制信號(如 I2C)等模擬 / 低速數字信號,核心訴求是 “高線性、低失真、高隔離”,因此設計為兩路 SPDT 開關,THD 低至 - 80dB(20Hz~20KHz),隔離度 - 100dB@100KHz,避免模擬信號受干擾。

場景適配:

高速通道:USB-C 擴展塢的多設備高速數據切換(如 U 盤與移動硬盤共享 USB 3.1 接口)、PCIe 背板信號路由;

低速通道:筆記本音頻接口切換(如耳機與揚聲器切換)、低速傳感器信號(如溫感)的路徑選擇。

問題 2:若需為 FSW6860 尋找替代型號,結合文檔參數,需優先匹配哪些關鍵指標?為何這些指標是核心?

答案:需優先匹配 **“通道配置、速率兼容性、核心電氣參數、封裝”** 四大類指標,具體原因如下:

通道配置:必須匹配 “五通道高速差分 2:1 + 兩路低速 SPDT” 結構 ——FSW6860 的核心價值是 “混合信號集成”,若替代型號通道數不足(如僅 3 路高速)或無低速通道,需額外增加芯片,導致 BOM 成本上升、PCB 面積增加;

速率兼容性:高速通道需支持USB 3.1 Gen 1(5Gbps),且帶寬≥7.5GHz@-3dB—— 帶寬不足會導致 5Gbps 信號衰減過大,眼圖閉合,無法滿足 USB 協議要求;

核心電氣參數:需匹配隔離度≥-39dB@5GHz、串擾≤-41dB@5GHz、導通電阻≤6.5Ω—— 隔離度 / 串擾不足會導致通道間信號泄漏,導通電阻過大會增加信號損耗,均影響信號完整性;

封裝:需為QFN6x6-48L—— 封裝不兼容會導致 PCB 焊盤無法復用,需重新設計布局,增加開發周期。

示例:若某替代型號為 “五通道高速 + 兩路低速、USB 3.1 Gen 1、帶寬 7.6GHz、隔離度 - 40dB@5GHz、QFN6x6-48L”,則可初步判定為合格替代候選。

問題 3:FSW6860 的控制引腳(SEL、_EN、S11、S12)協同工作時,需注意哪些邏輯順序?如何避免切換過程中的信號沖突或設備損壞?

答案:需遵循 “先使能、后選擇” 的邏輯,并關注 “先斷后合” 特性,具體注意事項如下:

協同工作邏輯順序:

第一步:拉低_EN引腳(低電平有效),使芯片從 “高阻態” 切換為 “就緒態”;

第二步:配置SEL引腳(高速通道選擇)和S11/S12引腳(低速通道選擇)—— 需確保高速與低速通道的選擇邏輯與外部設備需求一致(如高速選 A 端口時,低速通道 1 選 B01);

禁止操作:嚴禁在_EN=High(關斷)時單獨切換 SEL/S11/S12,此時通道為高阻態,切換無意義,且可能因電平突變產生噪聲。

避免信號沖突的關鍵措施:

利用 “先斷后合(tBBM)” 特性:高速通道 tBBM=250~500ns,低速通道 tBBM=500ns,切換時芯片會先斷開原通道、再閉合新通道,避免兩個端口同時導通導致短路;

控制信號同步:SEL 與 S11/S12 的切換需同步(延遲≤100ns),若高速通道已切換但低速通道未切換,會導致 “高速數據傳輸 + 低速信號中斷”,影響設備正常工作(如 USB-C 顯示器的視頻信號正常但音頻中斷);

外部電平匹配:控制引腳(SEL/S11/S12)需滿足VIH≥1.6V、VIL≤0.4V(VCC=3.3~4.5V),避免因電平不確定(如懸空)導致通道誤切換。

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54320瀏覽量

468508 -

模擬混合信號

+關注

關注

0文章

1047瀏覽量

15852

發布評論請先 登錄

深入解析 LTC2672:五通道高性能 DAC 的卓越之選

LTC2662:五通道電流源輸出 DAC 的技術詳解

深入解析MC100EL17:5V ECL 四通道差分接收器

ADP5050:五通道集成電源解決方案的深度剖析

高效五通道數字相機電源芯片MAX1565的全面解析

高速信號處理利器:TMUXHS4412 4通道 20Gbps差分2:1/1:2復用器/解復用器深度解析

德州儀器TB5D1M與TB5D2H:高性能四通道差分PECL驅動器解析

探索TB3R1與TB3R2:四通道差分PECL接收器的卓越性能

探索PCA9518:可擴展五通道I2C集線器的卓越性能與應用

EMS4100高速USB3.1模擬開關芯片方案,可pin對pin替代ASW3410不更改電路

四方杰芯FSW7227芯片簡介:USB2.0二切一開關芯片替代SGM7227

芯詳EMS4100: USB 3.1高速模擬開關芯片,替代ASW3410方案

四方杰芯 FSW6860 芯片簡介:五通道高速差分 + 低速模擬混合信號切換芯片 功能替代 ASW3642

四方杰芯 FSW6860 芯片簡介:五通道高速差分 + 低速模擬混合信號切換芯片 功能替代 ASW3642

評論