隨著硅基集成電路進(jìn)入后摩爾時(shí)代,二維過渡金屬硫化物(TMDCs,如MoS?、WS?)憑借原子級(jí)厚度、優(yōu)異的開關(guān)特性和無懸掛鍵界面,成為下一代晶體管溝道材料的理想選擇。然而,金屬電極與二維半導(dǎo)體間的接觸問題一直是制約其發(fā)展的核心障礙——接觸電阻過高(>800 Ω·μm)、費(fèi)米能級(jí)釘扎(FLP)效應(yīng)嚴(yán)重、納米尺度接觸穩(wěn)定性不足,難以滿足先進(jìn)工藝節(jié)點(diǎn)需求(IRDS標(biāo)準(zhǔn)要求總電阻≤220 Ω·μm)。本文通過結(jié)合TLM接觸電阻測(cè)試儀對(duì)接觸電阻的提取系統(tǒng)綜述面向硅產(chǎn)線兼容的二維半導(dǎo)體接觸工程技術(shù),從性能指標(biāo)、關(guān)鍵挑戰(zhàn)到創(chuàng)新解決方案,為未來產(chǎn)業(yè)化提供路線圖。

二維半導(dǎo)體接觸性能的評(píng)價(jià)維度

/Xfilm

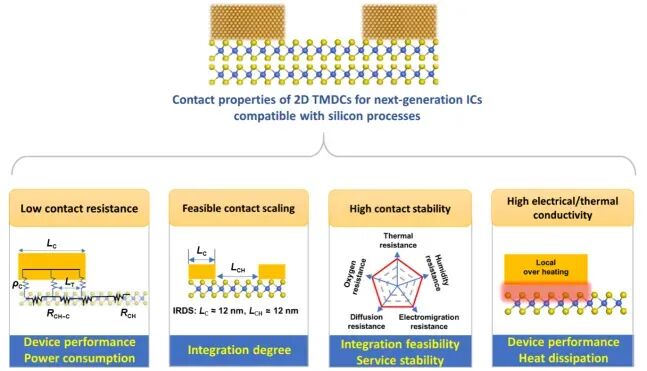

符合硅基工藝兼容性要求的二維TMDCs接觸特性示意圖

為匹配硅基工藝要求,論文提出多維度評(píng)價(jià)體系:

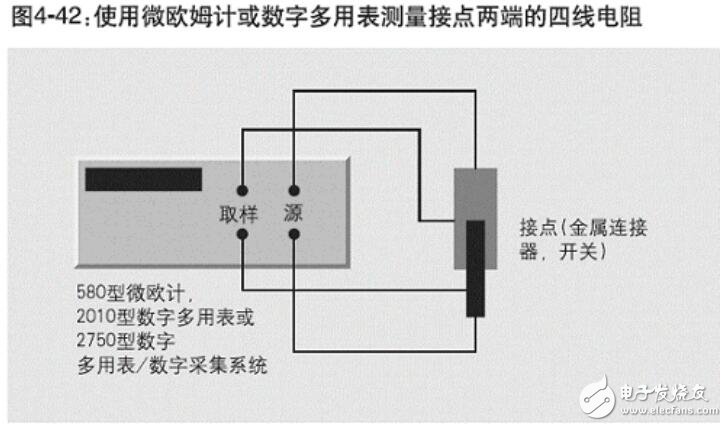

- 接觸電阻(RC):衡量2D TMDCs與金屬電極接觸性能的關(guān)鍵指標(biāo),直接影響器件性能和功耗,主導(dǎo)器件功耗與驅(qū)動(dòng)電流,需低于117 Ω·μm,常用的RC提取方法有Y函數(shù)法、四探針法和傳輸線法(TLM,目前最常用方法)。

- 接觸尺寸微縮性:決定集成密度,需實(shí)現(xiàn)<12 nm接觸長(zhǎng)度(LC)且避免電流擁擠效應(yīng);

- 接觸穩(wěn)定性:需耐受后端工藝(BEOL)450℃退火及環(huán)境因素(氧化、濕氣);

- 電/熱導(dǎo)率:影響信號(hào)傳輸效率與散熱;

- 工藝兼容性:支持8/12英寸晶圓級(jí)制造。

當(dāng)前最優(yōu)Y摻雜MoS?總電阻235 Ω·μm,但仍高于硅基250 Ω·μm的標(biāo)準(zhǔn),而傳統(tǒng)Au接觸MoS?在LC縮至30nm時(shí)RC激增13倍,凸顯優(yōu)化必要性。

二維半導(dǎo)體接觸的挑戰(zhàn)

/Xfilm

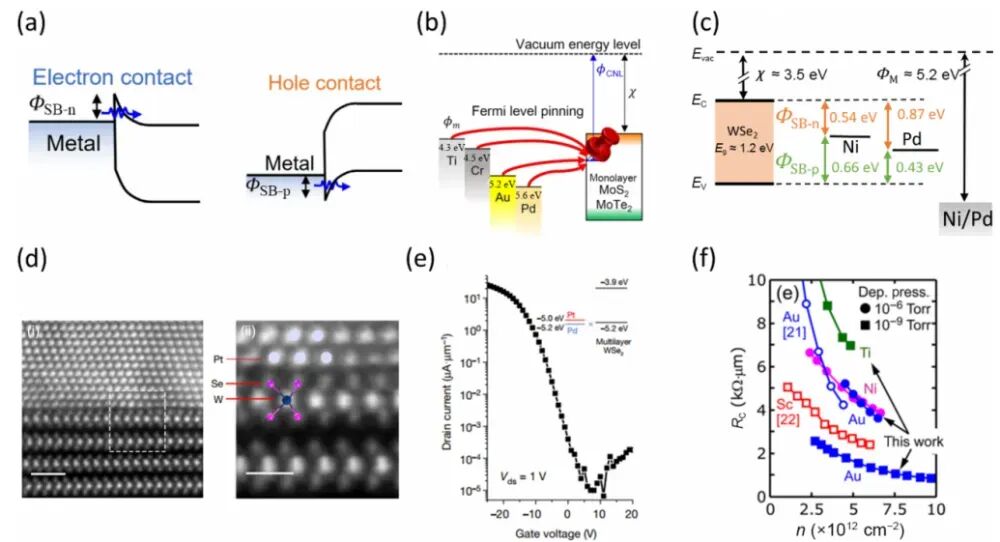

- 費(fèi)米能級(jí)釘扎與非理想載流子注入

(a) 金屬功函數(shù)調(diào)控載流子注入示意圖;(b) FLP效應(yīng)示意圖;(c) Ni/Pd與WSe?的實(shí)際能帶對(duì)齊;(d) Pt/WSe?原子分辨率圖像;(e) Pt接觸多層WSe?的轉(zhuǎn)移曲線;(f) 不同沉積壓力下的RC對(duì)比

界面缺陷(硫空位、金屬擴(kuò)散)引發(fā)強(qiáng)烈FLP效應(yīng),使肖特基勢(shì)壘高度(SBH)偏離理論值。例如Ti/MoS?接觸中,F(xiàn)LP導(dǎo)致實(shí)際SBH固定在0.15 eV附近,與金屬功函數(shù)無關(guān),電子注入效率降低60%。

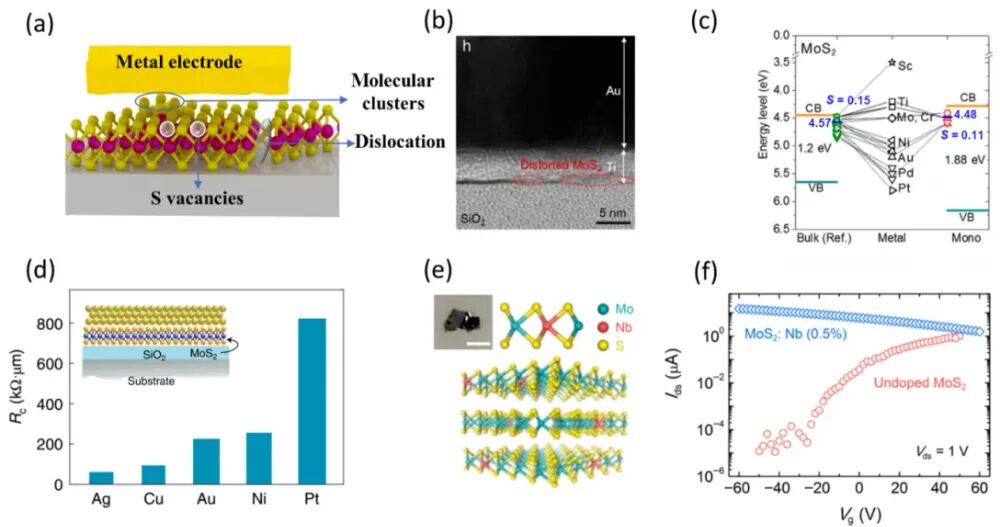

- 超薄層摻雜困境

(a) 界面缺陷示意圖;(b) Ti/Au電極沉積引起的MoS?界面無序;(c) 不同金屬電極與MoS?的FLP效應(yīng);(d) 不同金屬與MoS?的vdW接觸電阻;(e) Ni原子取代摻雜示意圖;(f) Ni摻雜前后MoS?晶體管的傳輸曲線

硅基重?fù)诫s技術(shù)無法移植:離子注入破壞單層TMDCs晶格,摻雜濃度難超1013 cm?2;表面吸附摻雜(如K/NO?)穩(wěn)定性差,易在空氣中失效。

- 尺寸微縮與穩(wěn)定性矛盾

熱穩(wěn)定性:低熔點(diǎn)金屬接觸(Bi/In)RC可低至42 Ω·μm,但熔點(diǎn)<300℃,無法承受BEOL工藝;電化學(xué)穩(wěn)定性:Ti/Ni電極易氧化,Cu擴(kuò)散導(dǎo)致界面降解。

硅工藝兼容的接觸工程突破

/Xfilm

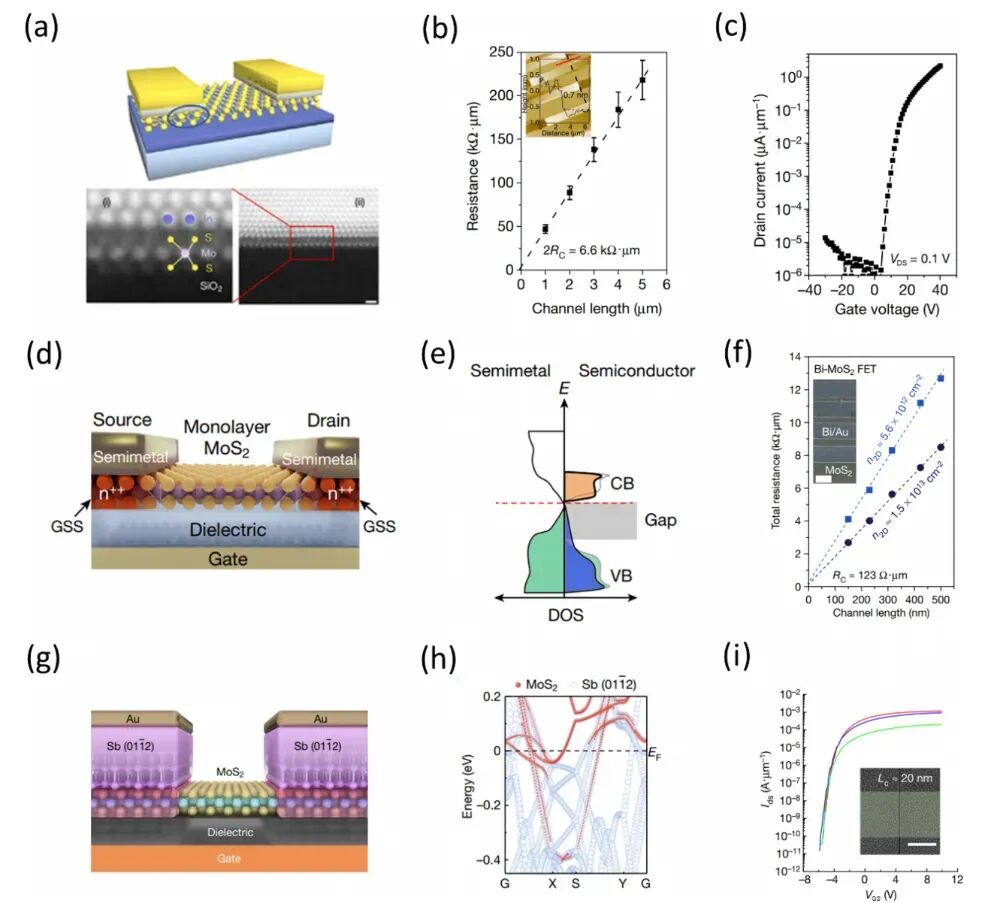

- 接觸電阻優(yōu)化

低熔點(diǎn)金屬的vdW接觸:(a) In/MoS?vdW接觸TEM圖;(b) TLM提取RC;(c) MoS?FET轉(zhuǎn)移特性;(d) Bi接觸MoS?示意圖;(e) 半金屬-半導(dǎo)體態(tài)密度示意圖;(f) Bi-MoS?的TLM曲線;(g) Sb(01?12)接觸示意圖;(h) Sb-MoS?能帶結(jié)構(gòu);(i) 20nm LC器件的轉(zhuǎn)移特性

范德華接觸:通過轉(zhuǎn)移金屬電極或低溫沉積低熔點(diǎn)金屬(In、Bi),實(shí)現(xiàn)原子級(jí)銳利界面,避免FLP效應(yīng)。Bi/MoS?接觸電阻RC僅123 Ω·μm,接近量子極限。

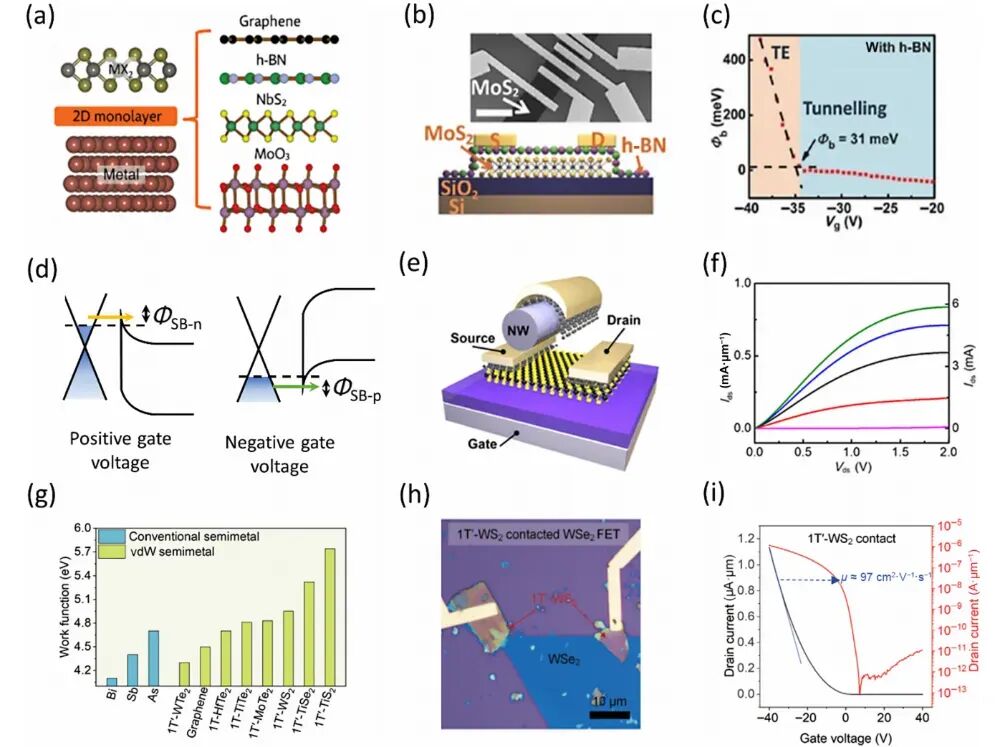

通過緩沖層優(yōu)化RC:(a) 金屬/緩沖層/MX?結(jié)構(gòu)示意圖;(b) h-BN緩沖層器件SEM圖;(c) h-BN厚度對(duì)SBH的調(diào)控;(d) 石墨烯接觸能帶對(duì)齊;(e) 石墨烯混合接觸器件示意圖;(f) 80nm MoS?晶體管轉(zhuǎn)移曲線;(g) 二維半金屬功函數(shù)總結(jié);(h) 1T'-WS?接觸WSe?器件光學(xué)圖;(i) 器件轉(zhuǎn)移曲線

緩沖層工程:插入h-BN/石墨烯層抑制金屬誘導(dǎo)間隙態(tài)(MIGS),使SBH從158 meV降至31 meV。

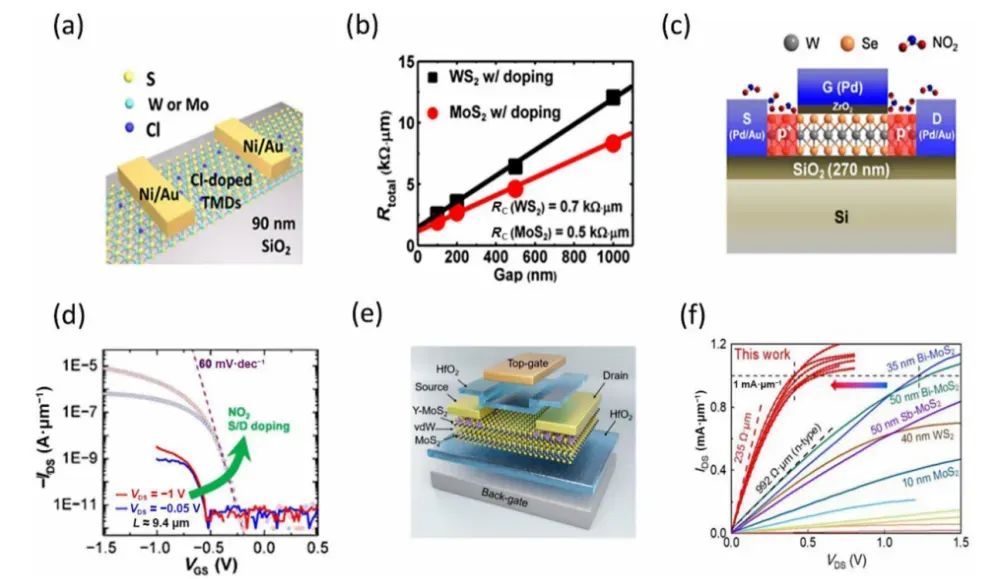

摻雜工程優(yōu)化接觸:(a) Cl摻雜示意圖;(b) WS?/MoS?接觸電阻;(c) NO?摻雜示意圖;(d) WSe?摻雜前后轉(zhuǎn)移曲線;(e) Y摻雜MoS?晶體管示意圖;(f) 亞50nm器件總電阻對(duì)比

相變摻雜:Y原子誘導(dǎo)MoS?從半導(dǎo)體相(2H)向金屬相(1T)轉(zhuǎn)變,形成歐姆接觸,總電阻235 Ω·μm且支持晶圓級(jí)加工。

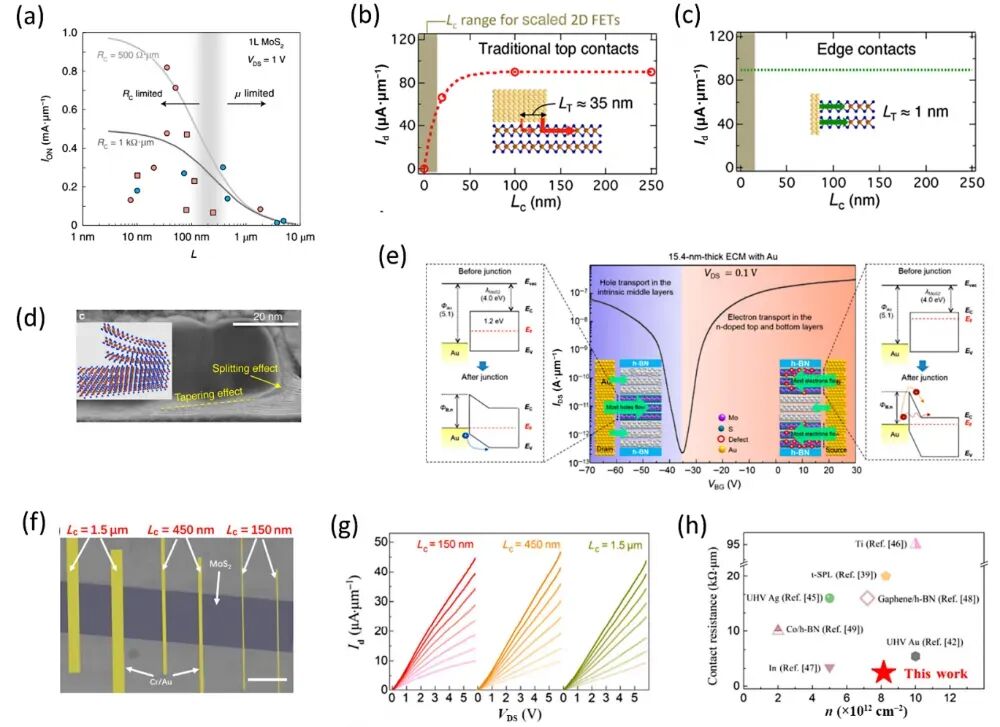

- 尺寸微縮:邊緣接觸的突破性進(jìn)展

二維TMDCs邊緣接觸:(a) 接觸電阻對(duì)器件性能的影響;(b,c) 邊緣接觸與頂部接觸電流對(duì)比;(d) 二維材料分裂示意圖;(e) 多層材料邊緣載流子分離注入;(f) 單層MoS?邊緣接觸器件;(g,h) 輸出特性與RC值

傳統(tǒng)頂接觸在LC<100 nm時(shí)RC呈指數(shù)增長(zhǎng),而邊緣接觸通過側(cè)向載流子注入規(guī)避該問題:氬等離子體刻蝕 MoS?,Ni邊緣接觸實(shí)現(xiàn) 20 nm LC,電流密度達(dá)1.23 mA/μm( @1V );多層TMDCs邊緣接觸呈現(xiàn)雙極傳輸特性,為互補(bǔ)邏輯設(shè)計(jì)提供新思路。

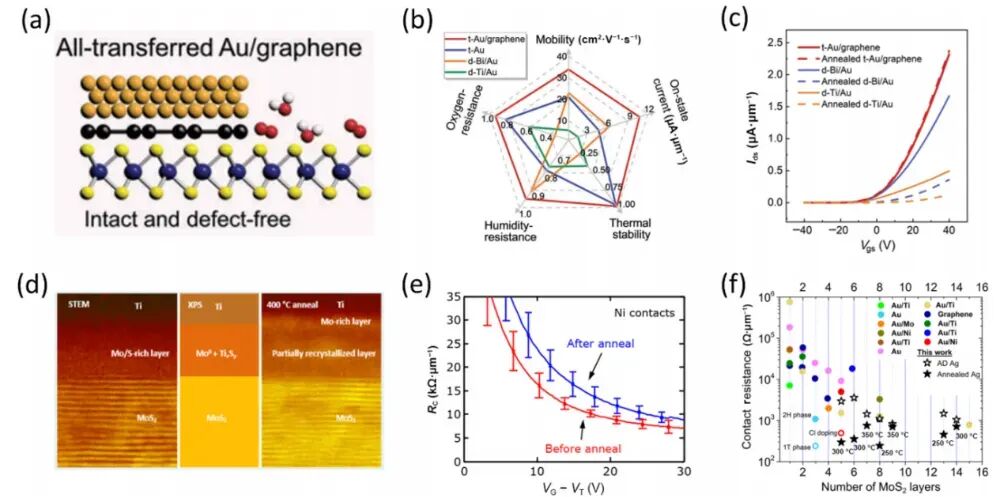

- 穩(wěn)定性提升:高熔點(diǎn)材料與封裝策略

接觸界面穩(wěn)定性優(yōu)化:(a) 石墨烯全轉(zhuǎn)移接觸器件;(b) 器件綜合特性;(c) 不同接觸退火性能對(duì)比;(d) Ti高溫?cái)U(kuò)散;(e) Ni接觸退火前后RC變化;(f) Ag接觸RC退火變化

合金電極:Sn/Au形成Au0.88Sn0.12(熔點(diǎn)521℃),將熱預(yù)算提升至400℃;全范德華封裝:石墨烯/Au電極在350℃退火后性能衰減<5%,遠(yuǎn)優(yōu)于傳統(tǒng)Ti/Au。接觸電阻優(yōu)化已逼近硅基水平:通過摻雜工程(Y/Cl)和半金屬接觸(Sb/Bi),成功將RC降低至42–235 Ω·μm,部分超越硅基節(jié)點(diǎn)標(biāo)準(zhǔn)。邊緣接觸技術(shù)更突破尺寸縮放極限,LC縮至5nm仍保持優(yōu)異電學(xué)性能。下一步需重點(diǎn)解決熱穩(wěn)定性協(xié)同優(yōu)化與晶圓級(jí)摻雜均一性問題,以滿足后摩爾時(shí)代集成電路需求。

-

集成電路

+關(guān)注

關(guān)注

5458文章

12605瀏覽量

375000 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30913瀏覽量

265216 -

接觸電阻

+關(guān)注

關(guān)注

1文章

128瀏覽量

12683

發(fā)布評(píng)論請(qǐng)先 登錄

什么是接觸電阻?

什么是接觸電阻?怎么測(cè)試接觸電阻?

接觸電阻原理及組成

接觸電阻是什么,接觸電阻過大的原因是什么

二維半導(dǎo)體晶體管實(shí)際溝道長(zhǎng)度的極限

劉開輝教授課題組在12英寸二維半導(dǎo)體晶圓批量制備研究中取得進(jìn)展

太陽能電池接觸電阻測(cè)試中的影響因素

NFC和二維碼掃描二合一的設(shè)備,用于產(chǎn)線數(shù)據(jù)采集

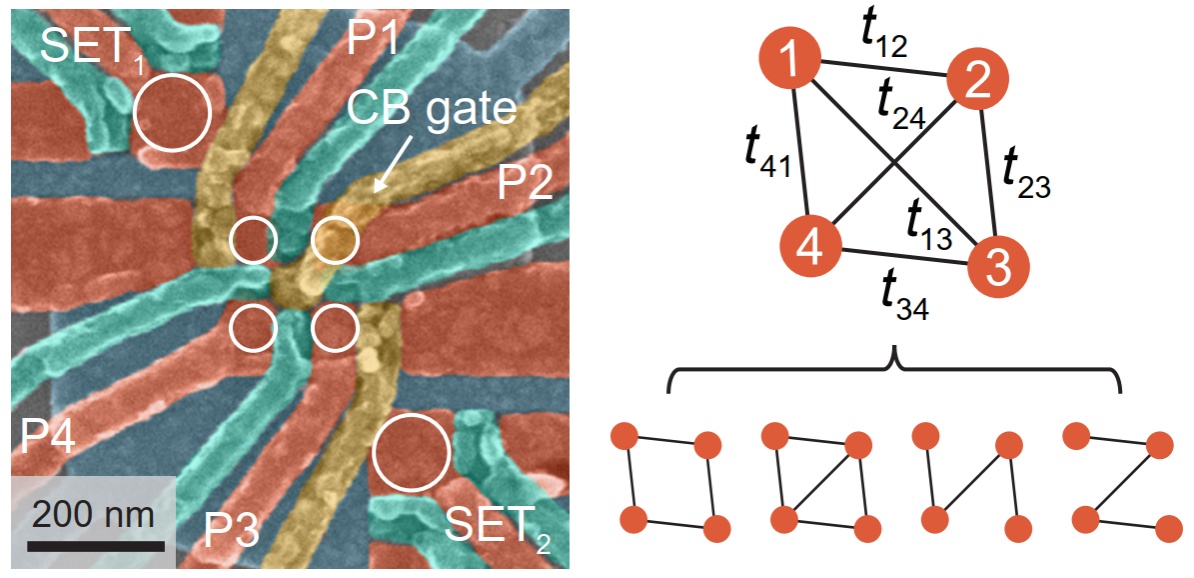

中國科大實(shí)現(xiàn)耦合高度可調(diào)的二維硅基量子點(diǎn)陣列

產(chǎn)線效率翻倍!二維碼掃碼器這樣用就對(duì)了

半導(dǎo)體歐姆接觸工藝 | MoGe?P?實(shí)現(xiàn)超低接觸電阻的TLM驗(yàn)證

從實(shí)驗(yàn)室到應(yīng)用:半金屬與單層半導(dǎo)體接觸電阻的創(chuàng)新解決方案

基于傳輸線模型(TLM)的特定接觸電阻率測(cè)量標(biāo)準(zhǔn)化

面向硅基產(chǎn)線:二維半導(dǎo)體接觸電阻的性能優(yōu)化

面向硅基產(chǎn)線:二維半導(dǎo)體接觸電阻的性能優(yōu)化

評(píng)論