作者:Laura Peters

文章來源:https://semiengineering.com/identifying-sources-of-silent-data-corruption/

在大型數據中心,靜默數據錯誤(SDE,Silent Data Errors)正引發廣泛擔憂 —— 這類錯誤會在系統內傳播,對 AI 訓練任務等長時間運行的程序造成嚴重影響。

從技術角度看,靜默數據錯誤(又稱靜默數據損壞-SDC,Silent Data Corruption)本身并不常見。但在由數千臺服務器組成的集群中(這些服務器搭載數百萬臺高利用率運行的處理器芯片),這類破壞性事件卻變得十分普遍。盡管任務模式測試正捕獲更多靜默數據錯誤,但事實證明,要檢測出所有數據損壞錯誤,其復雜程度遠超預期 ——這需要對設計、制造、可測試性設計(DFT)、測試流程,以及軟硬件運維環節進行針對性調整。

新思科技(Synopsys)工程架構總監 Jyotika Athavale指出:“當受影響的器件處理數據時,若無意中導致所處理數據出現未被察覺的錯誤,便會引發靜默數據損壞。例如,受影響的中央處理器(CPU)可能在完全沒有數據損壞提示的情況下,對數據進行錯誤計算。如今,計算密集型機器學習算法需在數萬個節點上執行,這類數據損壞可能在不觸發任何警報的情況下破壞整個數據集,而解決此類問題往往需要數月時間,進而帶來巨額成本損失。此外,該問題的復雜性與規模也使其難以通過主動措施防范;更關鍵的是,芯片生產周期較長,針對靜默數據損壞(SDC)的修復方案可能需要數年時間才能在新硬件中落地。”

靜默數據錯誤的棘手之處在于,其并非源于單一來源或單一機制。普迪飛(PDF Solutions )首席技術官 Andrzej Strojwas 表示:“靜默數據損壞(SDC)的潛在根本原因繁多。有人認為最可能的誘因是測試疏漏,但許多此類故障只有在實際應用環境中被觸發后才會顯現。例如,由于嚴苛的容差要求和形形色色的布局模式,晶體管層面可能存在漏電這類系統性缺陷。測試過程中可能遺漏對特定模式的敏感性檢測,進而演變為可靠性問題。此外,器件老化也是重要因素,會導致閾值電壓發生變化。不過,通過適當的測試結構設計,這些問題都可得到有效應對。”

靜默數據損壞(SDC)可能發生在硅片全生命周期的任何階段,這也是業界采用多種硅生命周期管理方法應對此類錯誤的核心原因。

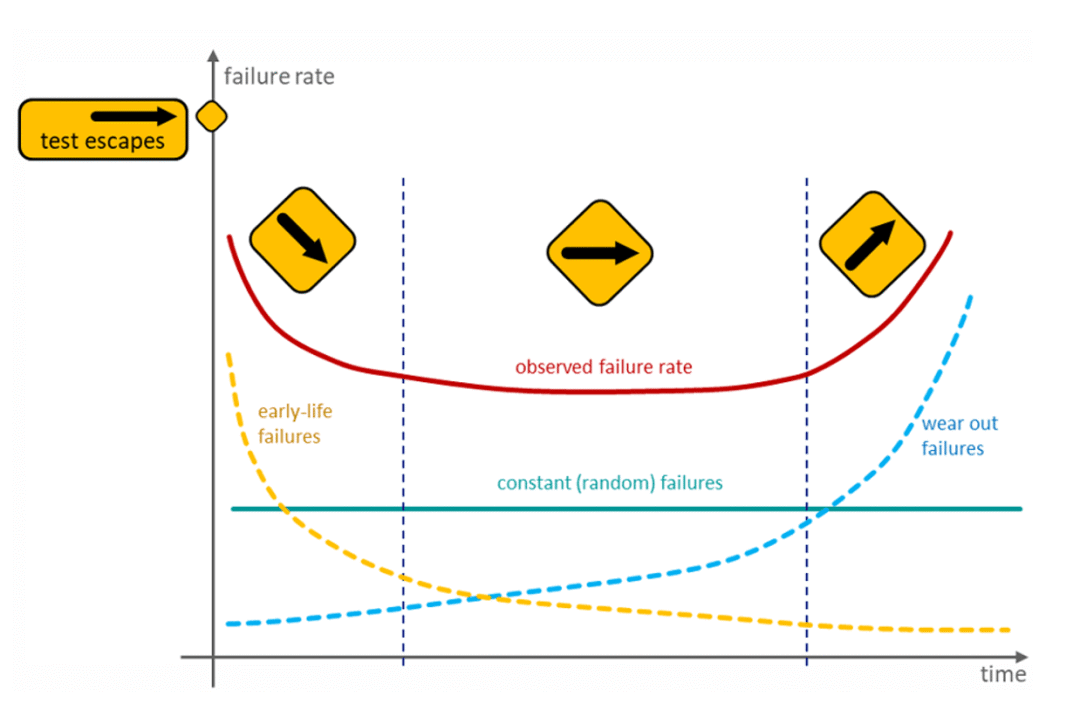

西門子 EDA(Siemens)旗下 Tessent 部門工程副總裁Janusz Rajski解釋道:“要消除早期失效現象,必須通過壓力測試加速器件老化。生產階段則需采用高質量、確定性的測試方法,同時在系統內也需執行相同的測試流程。部分企業會在核心閑置時開展測試,也有企業將其作為預防性維護措施,按周或按月定期執行,但無論哪種方式,系統內的測試都會非常全面 —— 這無疑是一項重大變革。”

(圖 1:器件全生命周期內的半導體故障率。來源:西門子EDA )

Janusz Rajski補充道:“靜默數據損壞(SDC)是個亟待解決的嚴重問題。多家企業發布的數據顯示,每 1000 臺服務器中,約有 1 臺可能受到此類問題影響。顯然,在任務關鍵型或安全關鍵型應用中,其影響會更為嚴重。超大規模數據中心最先發現這一問題,正是因為其處理器數量龐大,但實際上其他領域也存在類似情況。”

在測試層面,工程師們也在深入研究芯片架構優化方向。愛德萬測試(Advantest)應用研究與技術副總裁Ira Leventhal表示:“我們需要一種我稱之為‘架構感知測試’的方法 —— 因為在邏輯芯片中,只有特定的計算單元才有可能將故障傳播至整個網絡。因此,核心思路也就變成了‘將特定測試向量聚焦于核心的這些關鍵區域’—— 不僅要采用傳統掃描測試并核驗結果,還需將部分功能測試整合到自動測試設備(ATE)的測試環節中。”

測試越接近任務模式,就越容易捕獲靜默數據錯誤導致的故障結果。

Ira Leventhal指出:“我們可在 93k 測試工具上使用 LinkScale 卡,通過高速接口開展掃描測試,本質上是讓器件按照實際任務模式的運行邏輯工作。這種情況下,無需像系統級測試那樣運行全套測試場景,只需聚焦核心的特定區域,通過特定方式驅動器件運行,即可觸發靜默數據損壞(SDC)問題。這在異構集成場景中尤為重要 —— 我們需在芯片級發現所有潛在問題,確保芯片具備抵御靜默數據損壞的能力。這類措施能幫助我們在問題管控中占據主動。”

然而,即便在測試環節占據主動,企業也逐漸意識到,解決靜默數據損壞(SDC)問題真正需要的是整個供應鏈的協同。盡管器件制造商、測試企業與可測試性設計(DFT)提供商之間的合作已催生出更完善的篩選與緩解方案,但隨著器件和系統復雜度不斷提升,靜默數據錯誤問題只會愈發嚴峻,因此行業仍需長期策略支撐。例如,Meta 正探索如何提升應用對靜默數據損壞的容錯能力。Meta 工程總監斯里Sriram Sankar表示:“我們正在推進一項長期工作,旨在改進并推廣具備內在抗靜默數據損壞(SDC)能力的架構解決方案與設計模式。”

鑒于整個供應鏈解決靜默數據損壞(SDC)問題的緊迫性,OCP啟動了 “服務器組件彈性工作流” 項目,參與者包括AMD、安謀Arm、谷歌Google、英特爾Intel、微軟Microsoft、Meta 和英偉達NVIDIA等多家企業。去年 6 月,該項目為六個以解決靜默數據錯誤(SDE)為目標的研究項目提供了資金支持。

其他企業也認為,這一領域需要研究界的深度參與。谷歌工程總監Rama Govindaraju在近期的小組討論中表示:“僅依靠過往的方法,無法顯著推動問題的解決進程。 這一領域需要更多創新性研究,因為它需要更全面的解決方案,且必須引入新想法、創新性思路。靜默數據損壞(SDC)是個極其復雜的問題,需要開發大量研究成果和端到端解決方案。”

追溯靜默數據損壞(SDC)的根源,需從設計階段著手。新思科技杰出架構師Adam Cron指出:“我們曾交流過的一家芯片設計企業表示,即便是設計錯誤,也可能成為靜默數據錯誤(SDE)的來源。硅后驗證工具可為多線程應用生成邊界情況工作負載;隨后,在制造測試和現場測試階段,借助硅后激勵器可在硅片層面發現設計錯誤。這些測試也可用于仿真和驗證環節,以判斷設計邏輯是否存在問題。但有時,只有借助實際流片的硅片,才能發現這些特殊錯誤。”

Adam Cron特別強調,流片制造的實際硅片對于識別新故障(尤其是新工藝節點下的故障)至關重要:“內存有時需要針對新工藝的內建自測試(BiST)算法,以發現這些新的缺陷特征。通過流片制造實際硅片,是防范特定設計風格或物理布局方案日后演變為靜默數據錯誤(SDE)的有效保障。”

目前,半導體行業在兩方面取得了顯著進展:一是通過測試更有效地篩選缺陷,二是通過軟件管控靜默數據錯誤(SDE)造成的損害。然而,設計中的 “邊際性”(marginality)和工藝中的變異性,可能是靜默數據損壞(SDC)的核心誘因,且這類誘因極難察覺。有些潛伏性缺陷能通過所有測試和檢查,但一旦處于實際應用環境中,就可能在現場發生故障。

泰瑞達(Teradyne)技術與營銷總監Nitza Basoco解釋道:“就靜默數據錯誤(SDE)而言,某些知識產權(IP)模塊可能存在邊際性問題,但在‘零時刻’(time zero,即出廠時)仍可通過測試。然而,當信號路徑與環境條件呈現特定組合時,這類邊際性缺陷可能演變為關鍵性缺陷。而且,由于缺陷對多種因素的組合敏感,其是否會導致故障具有不確定性。”

盡管傳統測試是在故障發生后進行檢測,但部分策略已轉向預防導向。proteanTecs 聯合創始人兼首席技術官 Evelyn Landman表示:“我們專注于預測這些故障 —— 如今,一個主要問題是,這些故障會反饋給設備供應商,而供應商需投入巨額資源進行故障分析。在很多情況下,他們無法復現故障,導致‘未發現故障’(no trouble found,簡稱 NTF)率居高不下。我們的核心目標是從源頭避免故障發生。我們發現,在未采用我們方法的案例里,部分退回的故障芯片存在缺陷,而通過我們的方法本可提前發現這些問題。”

例如,借助對漏電流敏感的專用工藝監視器,結合模型可預測每顆芯片的預期漏電流。若實際漏電流超過預期值,即表明可能存在導致靜默數據錯誤的缺陷。

第二種方法是通過遙測監視器追蹤時序余量 —— 時序余量的變化是預測故障的關鍵指標。時序余量變化可能由多種因素引起,例如連接松動導致金屬線電阻升高,或特征粗糙度導致晶體管計算速度變慢。

時序延遲還與故障傳播路徑密切相關:若時序延遲沿短路徑傳播,微小延遲可能不會被察覺;若沿較長的關鍵路徑傳播,即便微小延遲也可能導致故障。然而,所有這些監視器都會占用硅片面積,產生成本開銷。尤其是在先進工藝節點下,器件可集成的傳感器數量有限,一旦空間耗盡便無法再增加。因此,遙測傳感器的部署必須經過周密規劃,優先部署在最關鍵的位置。

靜默數據錯誤發生率上升的部分原因,可能與芯片處于高壓力運行模式的時間增加有關。

Nitza Basoco指出:“系統級芯片(SoC)的設計初衷并非使其以最高電壓、最高頻率、高功耗狀態 24 小時不間斷運行 —— 原本設計的高負載運行時長本就較短。但如今,芯片大部分時間都處于高壓力環境中,因此故障風險顯著升高。我們需要明確芯片的實際運行工況,并調整相關設計或運行參數,以確保這些器件在與認證環境差異極大的工況下,仍能保持較長的使用壽命。”

Ira Leventhal提出了靜默數據損壞的三大管控方法:“在靜默數據損壞問題的管控方面,我們有三種核心手段 —— 檢測錯誤、降低錯誤發生率、構建缺陷容錯系統。這三種手段必須同時采用。我把它比作通信領域的問題應對邏輯:我們從不期望通信鏈路絕對可靠,因此始終會執行錯誤檢查。若系統檢測到錯誤,便會啟動重試機制 —— 這是預期的運行模式。”

此外,針對靜默數據損壞(SDC)的測試并非孤立進行。Adam Cron補充道:“任何用于檢測缺陷組件的設計結構,都有助于發現那些故障時會‘靜默失效’的器件。目前尚無專門針對靜默數據錯誤的工具,但任何可反映硅片整體質量狀況的特征都十分有用。例如,將工藝監視器與異常值檢測分析技術相結合,可幫助篩選出可能在現場出現問題的芯片。”

由于 Meta、谷歌等企業已找到通過軟件管控靜默數據錯誤的方法,行業對這類錯誤的警報聲已有所緩和。Nitza Basoco 提醒道:“目前,問題已得到初步控制,但如果靜默數據錯誤(SDE)的發生率上升到現有管控措施或臨時應對方案無法應對的程度,行業必須提前做好準備。”

行業也在積極針對多芯片組件采取預防措施。Janusz Rajski表示:“適用于 3D 集成電路(3D-IC)的可測試性設計(DFT)架構正逐步形成,該架構會將靜默數據損壞錯誤和設計規模不斷擴大的問題納入考量。測試壓縮并非新技術,但在這些核心中的應用已非常普遍。其次,流掃描網絡(可實現打包數據在不同核心間的傳輸)已應用于大多數大型設計,能以極高速度傳輸數據。我們還在開發 iJTAG 技術,以支持對大量儀器進行并行編程。在去年的國際測試會議(ITC)上,我們推出了在線測試(in-system test)技術,該技術可提供確定性測試能力,尤其適用于關注靜默數據錯誤或有特定可靠性、可用性與可維護性(RAS)需求的客戶。最后,還需借助監視器掌握工藝邊界(如工藝 - 電壓 - 溫度(PVT)邊界),部署時序裕量傳感器、路徑傳感器等結構傳感器,同時將傳感器讀數與測試結果進行關聯分析。”

結語

盡管通過可測試性設計(DFT)、工藝監視器和更全面的測試流程,制造和測試階段捕獲的靜默數據錯誤數量不斷增加,但在識別靜默數據錯誤(SDE)的所有根本原因、降低其造成的影響,以及防止其在數據中心內部傳播方面,行業仍有很長的路要走。

盡管如此,領先企業已積極采取行動:他們不僅采用更全面的基于任務模式的測試方法,還引入了系統內測試技術。超大規模數據中心運營商、集成電路(IC)制造商、測試企業、可測試性設計(DFT)提供商和 EDA 企業之間加強數據共享與協作,將有助于形成更全面的解決方案,同時避免供應鏈內部出現勞動重復的情況。

-

數據中心

+關注

關注

18文章

5651瀏覽量

75017 -

SDC

+關注

關注

0文章

50瀏覽量

16254 -

數據損壞

+關注

關注

0文章

4瀏覽量

5439

發布評論請先 登錄

一文讀懂傳感器的原理與結構

一文讀懂,電容如何識別資料下載

一文讀懂 | 識別靜默數據損壞的來源

一文讀懂 | 識別靜默數據損壞的來源

評論