在網(wǎng)卡、交換機、路由器、以太網(wǎng)等網(wǎng)絡(luò)設(shè)備中,晶振頻率的選擇是根據(jù)設(shè)備的核心功能、芯片要求以及通信協(xié)議標(biāo)準(zhǔn)來決定的。

使用 25MHz及其倍數(shù)關(guān)系的晶振 ,主要是因為這個頻率體系 與以太網(wǎng)標(biāo)準(zhǔn)、通信協(xié)議、芯片架構(gòu)緊密匹配 ,可以帶來設(shè)計簡化、成本降低和性能提升。下面詳細(xì)解釋一下這個問題:

一、為什么選擇25MHz作為基礎(chǔ)頻率?

25MHz并不是一個隨意選擇的數(shù)字,它之所以被廣泛使用,是因為它與網(wǎng)絡(luò)通信中一些核心頻率存在 整數(shù)倍關(guān)系 ,便于倍頻或分頻使用。

符合以太網(wǎng)標(biāo)準(zhǔn)頻率需求

· 百兆以太網(wǎng)(100BASE-TX) :使用25MHz時鐘作為數(shù)據(jù)傳輸頻率。

· 千兆以太網(wǎng)(1000BASE-T) :使用125MHz時鐘,即25MHz × 5。

· 10GbE(萬兆以太網(wǎng))及以上 :雖然主時鐘頻率更高(156.25MHz等),但通常仍可通過PLL從25MHz晶振倍頻得到。

這說明,25MHz作為基礎(chǔ)時鐘頻率, 可以直接或間接地支持主流以太網(wǎng)速率的PHY/MAC工作頻率 。

二、技術(shù)實現(xiàn)上的便利性

1. 易于使用PLL實現(xiàn)倍頻

網(wǎng)絡(luò)芯片(如PHY、MAC、交換芯片)內(nèi)部常使用 PLL(Phase Locked Loop,鎖相環(huán)) 電路來生成所需的工作時鐘頻率。25MHz是一個適中的輸入頻率,能夠高效地產(chǎn)生常見的高速頻率,如:

· 25MHz × 2 = 50MHz

· 25MHz × 4 = 100MHz

· 25MHz × 5 = 125MHz

· 25MHz × 6.25 = 156.25MHz(用于10GbE)

因為25MHz是一個 低整數(shù)倍數(shù)容易計算的基礎(chǔ)頻率 ,它使得 PLL 的設(shè)計更簡單,鎖定更快,輸出更穩(wěn)定。

2.兼容主流芯片需求

大多數(shù)網(wǎng)絡(luò)設(shè)備芯片廠商(如 Broadcom、Realtek、Marvell、Intel 等)在PHY或MAC的輸入時鐘要求中, 明確支持25MHz晶振輸入 ,或者提供25MHz輸入下的工作模式。

1.EMI控制更好,信號完整性高

相較于更高頻率的晶振(如50MHz、100MHz、125MHz、150MHz及200MHz),25MHz在電磁干擾(EMI)方面具有明顯優(yōu)勢:

· 較低的基頻意味著較少的諧波干擾;

· PCB布線更容易滿足EMI設(shè)計規(guī)范;

· 對外殼、電源完整性要求較低,方便系統(tǒng)集成。

2.晶振器件成熟、穩(wěn)定、成本低

25MHz晶振已經(jīng)是電子行業(yè)中 應(yīng)用最廣泛的頻率之一 ,具有以下優(yōu)勢:

· 大量現(xiàn)成產(chǎn)品,種類豐富;

· 制造成本低,采購價格便宜;

· 供應(yīng)鏈成熟,交期短,品質(zhì)穩(wěn)定。

這對大規(guī)模生產(chǎn)的網(wǎng)絡(luò)設(shè)備廠商具有極大的吸引力。

四、實際設(shè)計中的應(yīng)用示例

以一個千兆以太網(wǎng)交換機為例:

· 主控芯片要求輸入125MHz工作頻率;

· 設(shè)計時可使用一顆25MHz晶振,通過芯片內(nèi)置的PLL倍頻到125MHz;

· 同時,25MHz時鐘也可通過時鐘樹分配給其他模塊,如PHY、MAC或時鐘同步模塊;

· 這樣就實現(xiàn)了 統(tǒng)一時鐘源、簡化時鐘架構(gòu)、降低系統(tǒng)復(fù)雜度和成本 。

總結(jié)

網(wǎng)絡(luò)設(shè)備使用25MHz及其倍數(shù)關(guān)系的晶振,原因可以歸結(jié)為以下幾點:

| 原因類別 | 具體解釋 |

|---|---|

| 協(xié)議兼容 | 符合以太網(wǎng)標(biāo)準(zhǔn)(100M / 1G / 10G)所需的頻率倍數(shù) |

| 設(shè)計便利 | 易于通過PLL倍頻生成高速時鐘,簡化電路設(shè)計 |

| 信號完整性 | EMI低,便于滿足電磁兼容要求 |

| 成本效益 | 供應(yīng)鏈成熟、價格低、性能穩(wěn)定 |

| 芯片兼容 | 絕大多數(shù)PHY/MAC芯片支持25MHz晶振輸入 |

-

通信協(xié)議

+關(guān)注

關(guān)注

28文章

1093瀏覽量

42291 -

晶振

+關(guān)注

關(guān)注

35文章

3608瀏覽量

73685 -

頻率

+關(guān)注

關(guān)注

4文章

1588瀏覽量

62228 -

網(wǎng)絡(luò)設(shè)備

+關(guān)注

關(guān)注

0文章

344瀏覽量

30899

發(fā)布評論請先 登錄

電科網(wǎng)安中標(biāo)中直機關(guān)2025年網(wǎng)絡(luò)設(shè)備框架協(xié)議采購項目

晶振倍頻率干擾的解決方法

深圳光量子工廠啟示:PCI 加速卡為何偏向 25MHz 2016 有源晶振?

華為助力校園網(wǎng)網(wǎng)絡(luò)設(shè)備安全技術(shù)要求標(biāo)準(zhǔn)發(fā)布

芯盾時代助力上海某銀行建設(shè)網(wǎng)絡(luò)設(shè)備3A管理系統(tǒng)

網(wǎng)絡(luò)設(shè)備為什么選用25MHz及倍數(shù)頻率?

為什么網(wǎng)絡(luò)設(shè)備需要UPS電源?一文看懂電力守護的底層邏輯

touchgfx handletickevent 執(zhí)行的頻率 是由什么決定的?

三大核心網(wǎng)絡(luò)設(shè)備的運維要點

明微SM16306SJ和SM16206S的區(qū)別

NH13734網(wǎng)絡(luò)測試巴倫(BALUN)現(xiàn)貨庫存

工業(yè)網(wǎng)絡(luò)設(shè)備挑選不用愁,帶你快速選型

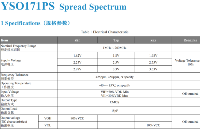

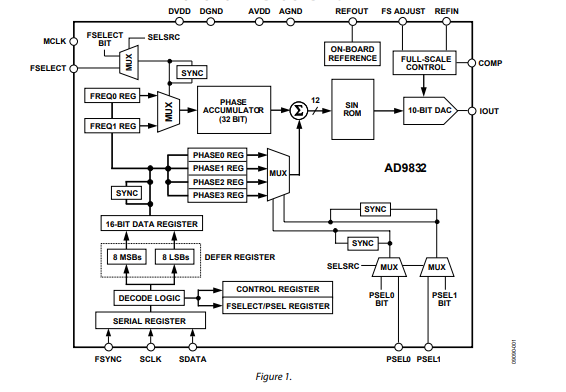

AD9832 25MHZ直接數(shù)字頻率合成器、波形發(fā)生器技術(shù)手冊

27MHz差分晶體振蕩器在網(wǎng)絡(luò)交換設(shè)備與路由器中的應(yīng)用方案

網(wǎng)絡(luò)設(shè)備為什么選用25MHz及倍數(shù)頻率?

網(wǎng)絡(luò)設(shè)備為什么選用25MHz及倍數(shù)頻率?

評論