在上期中,我們探討了優化電能計量中隔離式電流檢測的信號鏈成本和精度。

本期,為大家帶來的是《使用混合熱插拔架構防止高電流故障》,將討論設計高電流輸入電路保護具有哪些挑戰,以及混合熱插拔電路如何在任何故障情況下保護MOSFET。

引言

隨著云的快速采用,以及物聯網、人工智能和高性能邊緣計算等技術趨勢的出現,人們需要更快速、更靈活的企業系統來高效地管理工作負載。數據中心更高的數據吞吐量需要耗電量大的高速處理器,這將依靠典型 12V 電源軌的每臺服務器的電流電平提高至 250A 以上,還需要 20 至 30mF 的負載電容,以滿足系統的瞬態負載分布要求。

位于每臺服務器前端的熱插拔電路(結合使用熱插拔控制器和金屬氧化物半導體場效應晶體管 [MOSFET])可針對過載、輸出短路等系統故障提供浪涌電流限制和保護。在系統故障期間,熱插拔控制器可將MOSFET保持在飽和區域中,從而將故障電流限制在安全水平。但是,在設計可靠的熱插拔電路時,這些與較大輸出電容相關聯的不斷上升的系統電流卻帶來了巨大的挑戰,因為MOSFET處理功率應力的能力有限。

本文討論了設計高電流輸入電路保護具有哪些挑戰,以及將電子保險絲與常規熱插拔控制器并聯使用的混合熱插拔電路如何在任何故障情況下保護MOSFET。

傳統熱插拔電路

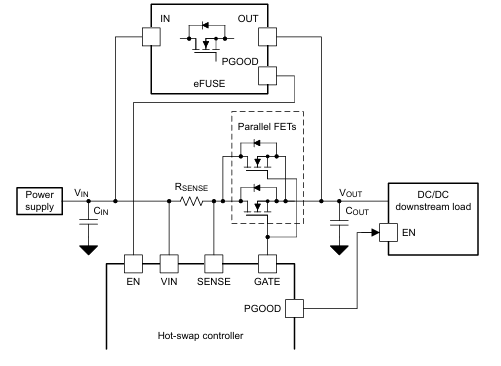

簡化的熱插拔電路包含一個熱插拔控制器、一個外部電流檢測電阻器和一個功率 MOSFET。在系統故障期間,熱插拔控制器會推動MOSFET在飽和區域中工作,以限制故障電流,導致MOSFET承受較大的漏源壓降和很高的功率應力。

熱插拔控制器通過可編程故障計時器 (TTIMER)實現功率限制方案 (PLIM),以提供 FET 安全工作區域 (SOA) 保護。選擇適當的 PLIM和 TTIMER值非常重要,可用于確保所選的MOSFET在發生應力事件的最大工作溫度下在其 SOA 限制內工作。如果所選的 FET 在設計中不可行,則您必須選擇具有更高 SOA 的 FET,這讓熱插拔電路設計變得高度迭代且復雜。

電子保險絲具有集成的過熱保護電路,可監測內部 FET 溫度,并在 FET 承受較長時間應力時將其關斷,從而確保 FET 在 SOA 限制內工作。目前電子保險絲器件只能在低電流下工作,因此,若要實現高電流電路保護,唯一的選擇便是使用基于FET的外部熱插拔解決方案。

設計大功率熱插拔解決方案的挑戰

為了確保 FET 一直處于其 SOA 范圍內,熱插拔控制器會實現一個功率限制方案,在 FET 的功率損耗達到 PLIM時觸發故障計時器;如果功率損耗未降至 PLIM以下,則將在 TTIMER之后關斷 FET。

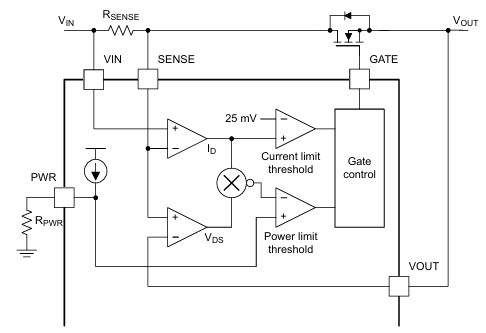

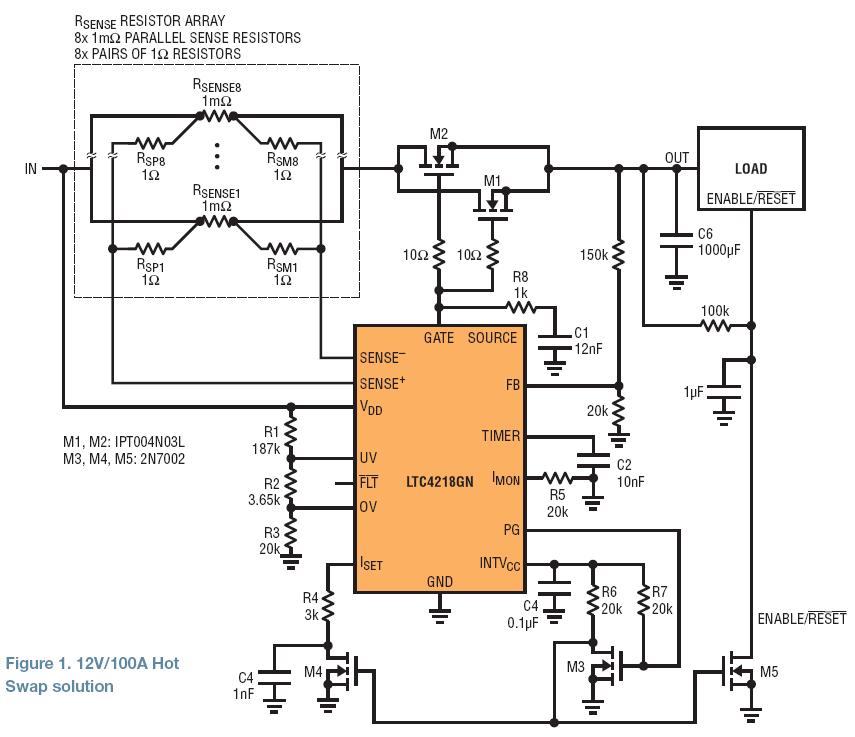

熱插拔控制器的功率限制控制環路(如圖 1 所示)包含一個電流檢測放大器,用于監測檢測電阻的電壓 (VSNS),以獲得電流信息,此外還包含一個電壓檢測電路,用于測量 FET 的電壓。將電流檢測放大器和電壓檢測電路的輸出相乘,可以得到 FET 中的功率損耗。將該損耗值與和 PLIM成比例的電壓進行比較后,您可以使用它來調節柵極電壓。熱插拔控制器可調節柵極電壓,確保MOSFET中的功率損耗始終低于 PLIM。

圖 1:熱插拔控制器中的功率限制環路

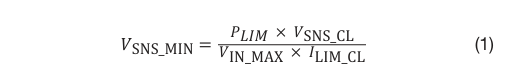

雖然較低的功率限制設置可降低 FET 上的應力,但它也會減少熱插拔控制器需要限制的電流量,因此電流檢測放大器可以檢測的 VSNS也會降低。VSNS較低會導致誤差較大,因為理論上,電流檢測放大器的失調電壓會限制最小可能功率限制的設置。方程式 1 針對大多數熱插拔控制器提供了建議最低檢測電壓 (VSNS-MIN):

方程式 1

其中,VSNS_CL是電流限制檢測電壓,VIN_MAX是最高輸入電壓,ILIM_CL是電流限制設置閾值。

高電流應用需要較高的電流限制閾值,因此必須設置更高的 PLIM,才能滿足方程式 1 定義的 VSNS_MIN標準。PLIM升高后,需要更高的MOSFET SOA,最終導致難以找到合適的MOSFET來實現大功率設計。例如,12V、250A 的設計要求 FET 能夠在 100°C 處理 560W 的功率應力,持續時間為 1ms,而現有的商用 FET 無法實現這一點。

驅動大容性負載的挑戰

對于具有較大輸出電容的設計,輸出 (dv/dt) 控制電路可在啟動期間處理 FET 功率應力。放置在柵極-GND 之間的電容器Cdv/dt可限制柵極和輸出電壓的壓擺率,從而限制浪涌電流。

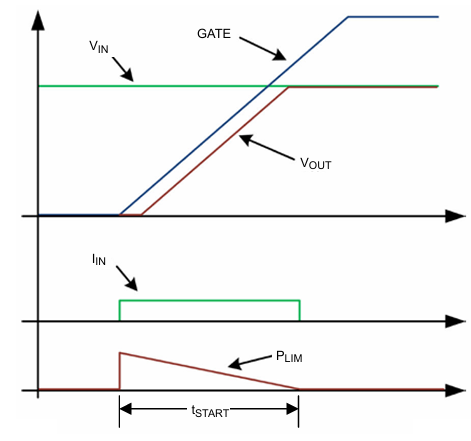

下圖顯示了帶有輸出 dv/dt 控制的典型啟動波形。您必須設置足夠低的壓擺率和適當的Cdv/dt值,確保 MOSFET 保持在其 SOA 范圍內。當 MOSFET 中的功率損耗降低且分布在較長的時間段內時,它們可以處理更多能量。因此,隨著輸出電容增加,您需要更高的Cdv/dt來降低 FET 在啟動期間的浪涌電流和功率損耗。例如,要在 SOA 范圍內運行特定 FET,10mF 的輸出電容可能需要 47nF 的 Cdv/dt,而 30mF 的輸出電容需要 330nF 的 Cdv/dt。

圖 2:帶有輸出 dv/dt 控制的啟動

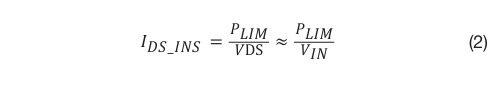

啟動至短路期間,熱插拔控制器要求路徑中流過一定量的電流(方程式 2 中的 IDS-INS),才能檢測并觸發功率限制故障。

方程式 2

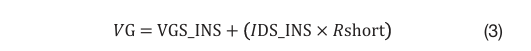

較大的 Cdv/dt會減慢柵極電壓斜升速率,導致延遲達到建立 IDS-INS所需的柵極電壓,從而增加故障檢測時間,并致使MOSFET承受很大的 SOA 應力,尤其是當短路阻抗 (Rshort) 升高時,該阻抗由方程式 3 所定義,如圖 3 所示:

方程式 3

圖 3:高阻抗短路下的柵極電路

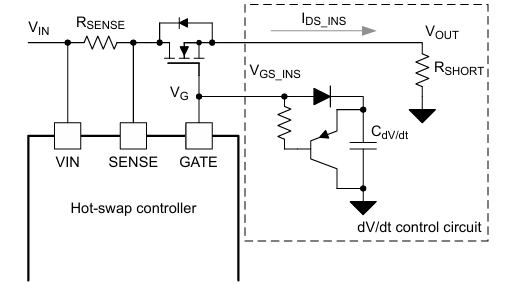

圖 4:5mΩ 阻抗短路時 FET 上的功率應力

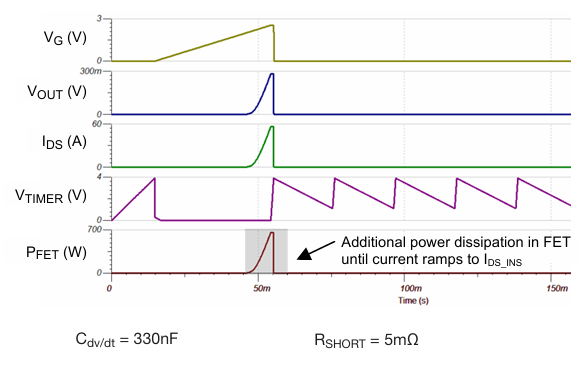

圖 5:50mΩ 阻抗短路時 FET 上的功率應力

考慮一個包含兩種不同阻抗的輸出短路:5m? 和 50m?。如果在啟動期間發生5m? 短路,隨著柵極電壓逐漸升高,短路電流會以更快的速度上升,短短 6ms 便會達到功率限制閾值(300W)。達到閾值后,將觸發TTIMER并關斷 FET。另一方面,50m? 短路阻抗會減慢短路電流的上升速度,熱插拔控制器需要花費大約 50ms 來檢測 300W 的功率限制閾值。該瓦數對應 15J 能量,這個巨大的能量可能會損壞FET,如圖 5 所示。

混合熱插拔解決方案

混合熱插拔解決方案包含一個與傳統熱插拔電路并聯的電子保險絲,如圖 6 所示。在該電路中,電子保險絲將利用其集成的過熱保護功能來應對高應力事件。

圖 6:混合熱插拔配置

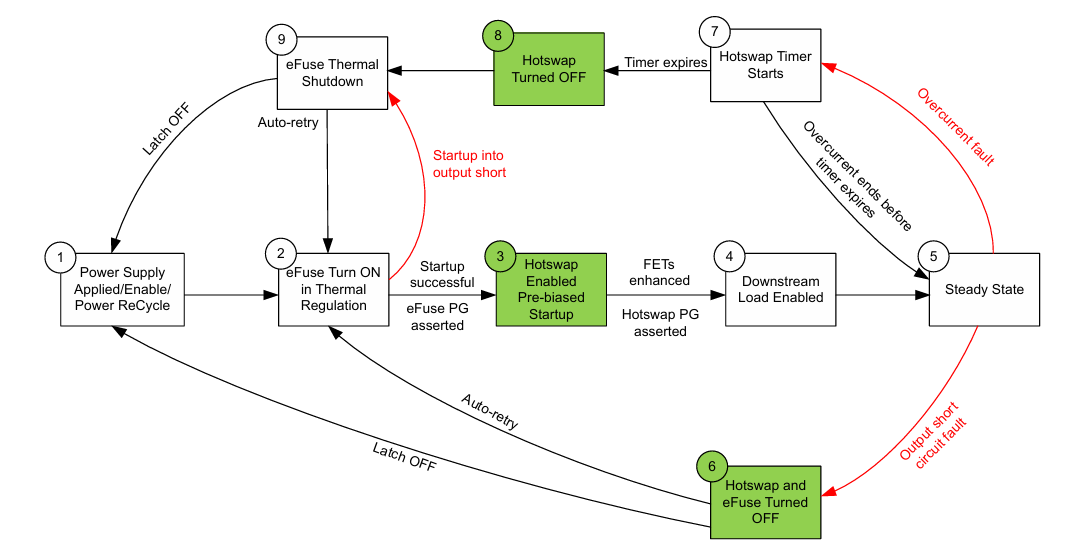

電子保險絲的 PGOOD 信號連接到熱插拔控制器的使能引腳,熱插拔控制器的 PGOOD 信號則連接到下游負載的使能引腳。這些連接可確保:

?熱插拔 FET僅在電子保險絲將大型輸出電容器充電到接近輸入電壓后導通。FET 啟動時兩端電壓幾乎為零,從而在啟動期間消除功率應力。

?下游負載僅在熱插拔 FET 得到完全增強后啟用,以便FET提供低阻抗路徑(與電子保險絲相比)并共享大部分負載電流。

? 電子保險絲在所有故障情況下均承受功率應力,而熱插拔 FET在任何情況下均不受應力影響。

圖 7 說明了啟動期間和不同故障情況下的電路功能。狀態 1 至 5 描述了啟動期間的事件順序,狀態 6 至 9 則是不同故障情況的中間狀態。

圖 7:混合熱插拔解決方案流程圖

混合熱插拔方案的主要優勢是,熱插拔 FET SOA 不再那么關鍵;您可以選擇超低漏源導通電阻 (RDS(ON)) FET,它們通常更便宜,并且能大幅減少FET的數量。

重要的設計注意事項

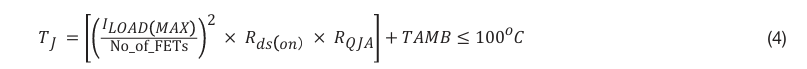

第一個設計注意事項是熱插拔路徑中并聯FET的數量。我們建議讓 FET 在穩定狀態下運行,以便使結溫低于 100°C。方程式 4 計算了給定負載電流下所需的并聯 FET 數量:

方程式 4

其中,TJ是 FET 結溫,ILOAD(MAX)是最大負載電流,Rds(on)是所選 FET 的最大 Rds(on),RQJA是 FET 的結至環境熱阻。

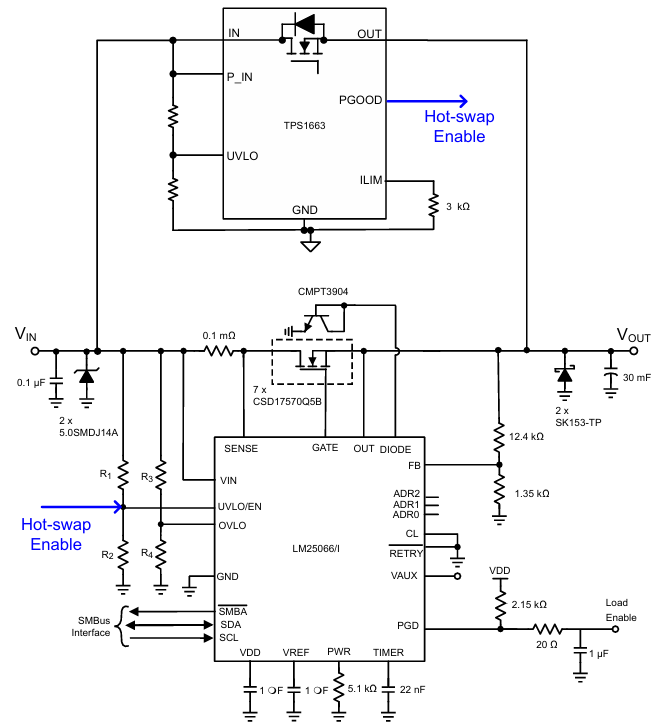

接下來,選擇電子保險絲。TPS1663 電子保險絲有集成的熱調節環路,可在大容性負載下實現零噪聲啟動。

在穩定狀態下,熱插拔路徑提供比電子保險絲路徑更低的阻抗,因此能共享大部分負載電流。熱插拔控制器還決定過流保護閾值,這與傳統熱插拔設計一樣。應將此閾值設置為剛好超過最大負載電流。

對于電子保險絲,將電流限制設置為其最大值(TPS1663為 6A),以便在系統啟動期間實現最快的輸出電容器充電速度。

TTIMER對FET SOA來說不再關鍵,因為在混合熱插拔架構中,熱插拔 FET 不受任何應力影響。您可以僅根據負載瞬態要求選擇故障計時器持續時間設置。

大功率設計使用多個并聯 FET,但熱插拔控制器的柵極驅動強度有限,這增加了 FET 的開通延遲時間。建議在開啟下游負載時添加額外的延遲(5ms 范圍內),以便為熱插拔控制器提供足夠的時間來完全增強FET。

圖 8 顯示了一個使用LM25066 熱插拔控制器和TPS1663 電子保險絲的示例混合熱插拔電路,具有 12V 輸入、250A 負載電流和 30mF 輸出電容。

圖 8:混合熱插拔電路

測試結果

面向應力事件的混合熱插拔解決方案使用LM25066 評估板和用于 TPS26633 和 TPS16630的評估模塊,具有 30mF 輸出電容器和 10A 熱插拔電流限制,而且已經過驗證。

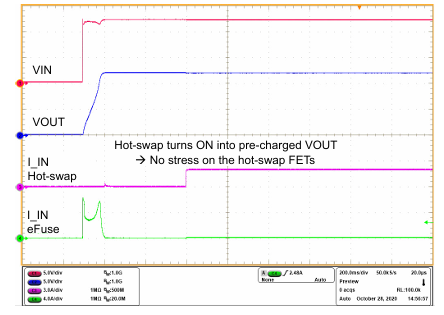

圖 9 顯示了該電路的啟動和穩定狀態行為。在啟動期間,為輸出電容器充電所需的整個電流會流經電子保險絲,此時熱插拔路徑尚未啟用。啟動階段過后,幾乎整個負載電流都會流經熱插拔路徑,因為它是低阻抗路徑。

圖 9:在 30mF 電容下啟動

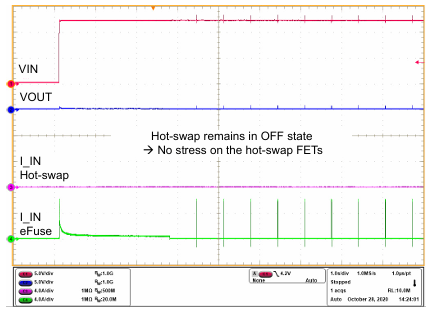

圖 10 顯示了輸出端短路的電路的啟動行為。電子保險絲在啟動時進入熱調節模式,并在熱調節超時后關閉;每隔 650ms 持續不斷地定期重試,直到輸出故障消除。由于熱插拔 FET 保持關閉,因此FET上沒有應力。

圖 10:啟動至短路

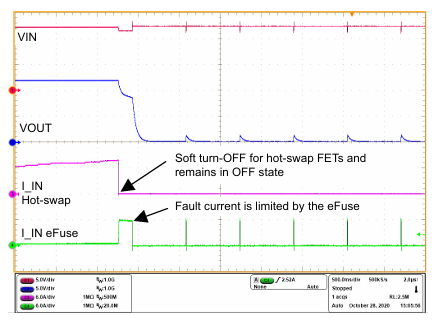

發生過載故障時,熱插拔電路在關斷FET前會產生過載電流,并持續計時器時間。圖 11 顯示了熱插拔 FET 關斷后,整個負載電流傳輸至電子保險絲路徑,從而觸發電流限制并最終觸發熱關斷。

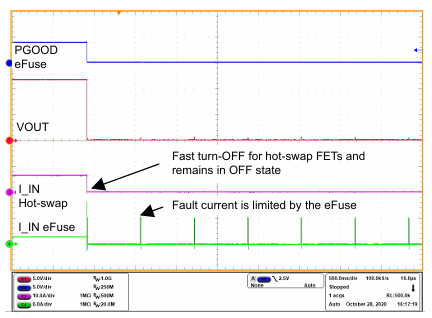

圖 12 顯示了在穩定狀態下發生輸出短路故障時的電路行為。熱插拔和電子保險絲都立即關閉,以保護輸入電源免受損壞。電子保險絲會持續不斷地定期重試,熱插拔 FET則保持關斷,直到電子保險絲成功啟動。

圖 11:過載故障期間的電路響應

圖 12:輸出短路期間的電路響應

結論

由于服務器系統的功率級別持續增長,促使輸入大容量電容提升到 20 至 30mF,以及 12V 電壓軌下的滿負載電流超過 200A。混合熱插拔解決方案使用一個額外的并聯電子保險絲,不僅解決了傳統保護電路在較高功率級別下的難題,還消除了熱插拔 FET SOA 方面的疑慮,從而簡化了熱插拔設計,并大幅降低了解決方案成本。混合熱插拔解決方案針對不同的故障情況進行了測試,證明該電路可消除熱插拔 FET上的應力。

-

MOSFET

+關注

關注

151文章

10200瀏覽量

234487 -

熱插拔

+關注

關注

2文章

274瀏覽量

41170 -

電流檢測

+關注

關注

14文章

701瀏覽量

42802 -

晶體管

+關注

關注

78文章

10423瀏覽量

148246

原文標題:模擬芯視界 | 使用混合熱插拔架構防止高電流故障

文章出處:【微信號:tisemi,微信公眾號:德州儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于IC的熱插拔保護電路應用

空間受限應用中的PMBus熱插拔電路基礎介紹

基于TPS2491的熱插拔保護電路設計

利用保證的SOA在高電流熱插拔集成型解決方案

具有浪涌電流限制的NCP45520熱插拔電路

使用NCP45521進行熱插拔開關的典型應用熱插拔電路

基于LTC4218的熱插拔設計解決方案

基于IC的熱插拔電路保護的優勢

基于混合熱插拔解決方案實現高電流輸入電路保護

基于混合熱插拔解決方案實現高電流輸入電路保護

評論