在嵌入式系統開發中,硬件電路設計是確保數據可靠性的關鍵環節。本期我們將重點探討硬件設計中的兩個重要方面:數據讀寫保護和掉電保護。

?硬件電路設計

?硬件電路設計

在嵌入式系統開發中,硬件電路設計對于確保數據的可靠性和系統的穩定性起著至關重要的作用。電源管理、信號完整性、電磁兼容性(EMC)、數據讀寫保護和掉電保護等都是硬件電路設計的關鍵方面。這些要素相互配合,共同構建了一個既可靠又高效的硬件平臺。今天,我們將重點深入探討數據讀寫保護和掉電保護這兩個至關重要的環節。 ?數據讀寫保護

?數據讀寫保護

在硬件電路設計中,數據讀寫保護是確保數據完整性和安全性的關鍵。NAND Flash芯片通常配備一個寫保護引腳(#WP),但在實際設計中,許多工程師往往會忽略這個引腳,導致芯片始終處于可寫狀態。這種設計存在潛在風險,可能會導致數據被意外寫入或覆蓋,從而影響數據的完整性和可靠性。

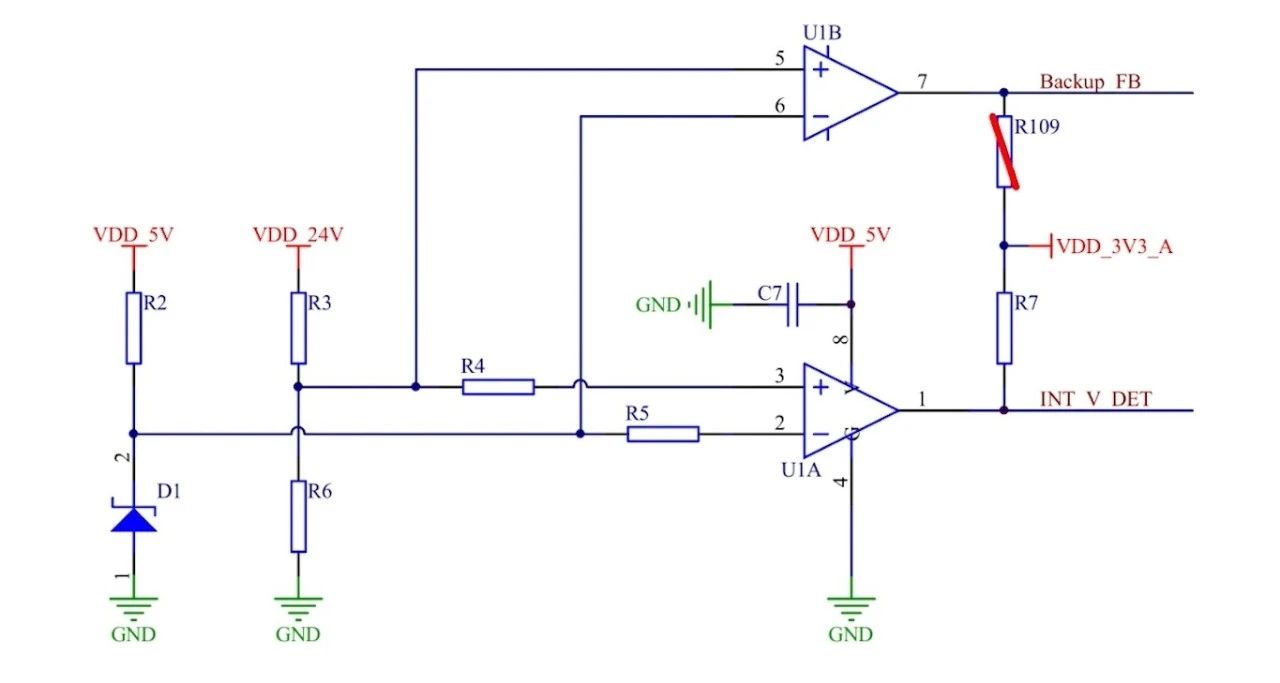

圖1 帶NAND寫保護的電路圖

1. 寫保護引腳(#WP)的作用

寫保護引腳(#WP)是NAND Flash芯片的一個重要特性,用于防止數據被意外寫入或覆蓋。當#WP引腳被設置為低電平時,芯片進入只讀模式,數據無法被寫入或修改。當#WP引腳被設置為高電平時,芯片進入可寫模式,可以進行數據寫入操作。

2. GPIO控制#WP引腳

建議在硬件設計時,使用一個GPIO引腳來控制#WP引腳。這樣可以確保芯片在大多數時間處于只讀狀態,僅在需要寫入數據時才切換到可寫模式。這種設計不僅提高了數據的安全性,還減少了因意外寫入導致的數據損壞風險。具體實現方法:

HAL_GPIO_WritePin(GPIOx, GPIO_PIN_x,GPIO_PIN_RESET);// 設置WP引腳為低電平,進入只讀模式HAL_GPIO_WritePin(GPIOx, GPIO_PIN_x,GPIO_PIN_SET); // 設置WP引腳為高電平,進入可寫模式

3. 數據完整性校驗

除了硬件保護,還可以通過軟件實現數據完整性校驗。例如,使用CRC校驗或ECC糾錯技術,確保數據在寫入和讀取過程中的完整性。這些技術可以有效檢測和糾正數據傳輸中的錯誤,進一步提高數據的可靠性。

?掉電保護

?掉電保護

掉電保護是硬件設計中另一個容易被忽視的環節。許多數據丟失或系統損壞問題都是由系統異常掉電引起的。通過增加掉電保護電路,可以有效規避這些問題。

1. 掉電檢測電路

掉電檢測電路可以檢測電源電壓的下降,并向處理器發送中斷信號。常見的實現方法是使用電壓比較器(如LM393)設計一個簡單的掉電檢測電路。當電源電壓下降到一定值時,電壓比較器輸出低電平,觸發處理器的中斷引腳。

圖2 掉電檢測電路參考具體實現方法:

- 硬件連接:將電壓比較器的輸出引腳連接到微控制器的一個中斷引腳。

- 軟件處理:在中斷處理函數中,執行數據保存和系統關閉流程。

voidHAL_GPIO_EXTI_Callback(uint16_t GPIO_Pin){ if(GPIO_Pin == GPIO_PIN_x) {// 檢測到掉電中斷 // 保存關鍵數據 SaveCriticalData(); // 關閉系統 ShutdownSystem(); }}

2. 后備電源

后備電源可以在主電源中斷時提供足夠的電力,確保系統能夠完成必要的善后工作。常見的后備電源包括超級電容和備用電池。超級電容具有快速充放電的特性,適合短時間的后備電源需求;備用電池則可以提供更長時間的電力支持。具體實現方法:

- 硬件連接:將超級電容或備用電池連接到系統的電源輸入端,并通過一個切換電路確保在主電源中斷時自動切換到后備電源。

- 軟件處理:在系統檢測到掉電中斷后,立即啟動數據保存和系統關閉流程,確保在后備電源耗盡之前完成所有關鍵操作。

3. 中斷處理

系統接收到中斷信號后,立即啟動數據保存和系統關閉流程。這包括保存關鍵數據、關閉外設、關閉文件系統等操作,確保數據的完整性和系統的穩定性。具體實現方法:

- 數據保存:將關鍵數據寫入非易失性存儲器(如EEPROM或Flash)。

- 關閉外設:關閉所有外設,確保它們處于安全狀態。

- 關閉文件系統:關閉文件系統,確保文件系統的完整性。

voidSaveCriticalData(){ // 將關鍵數據寫入非易失性存儲器 WriteDataToFlash(criticalData);}

voidShutdownSystem(){ // 關閉外設 ClosePeripherals(); // 關閉文件系統 CloseFileSystem(); // 關閉系統 HAL_PWR_EnterSLEEPMode(PWR_SLEEPENTRY_WFI);}

?ZLG致遠電子邊緣技術產品

?ZLG致遠電子邊緣技術產品

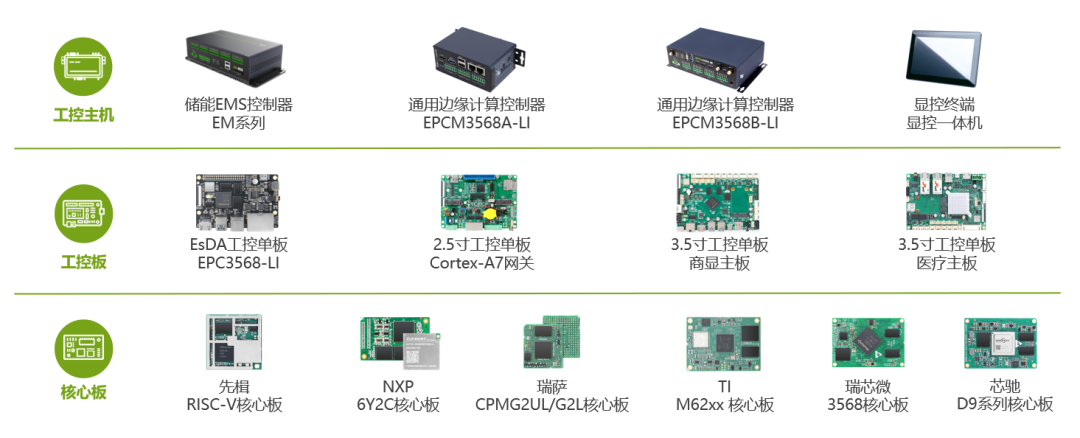

ZLG致遠電子在設計產品時,充分考慮了數據讀寫保護和掉電保護的需求。通過精心設計的硬件電路,確保了數據的可靠性和系統的穩定性。我們采用的GPIO控制WP引腳和掉電檢測電路,為數據可靠性提供了堅實的硬件基礎。

圖2 ZLG致遠電子邊緣技術產品

-

嵌入式

+關注

關注

5206文章

20575瀏覽量

336158 -

電路設計

+關注

關注

6745文章

2738瀏覽量

219990 -

硬件電路

+關注

關注

39文章

267瀏覽量

30355

發布評論請先 登錄

硬件電路的可靠性

嵌入式系統產品的可靠性

開發高可靠性嵌入式系統的技巧有哪些?

如何對嵌入式軟件進行可靠性測試

嵌入式系統的可靠性設計

軍用嵌入式系統的可靠性考慮因素

【干貨速遞】嵌入式數據可靠性,軟件設計的這些細節不能忽視!

【深度解析】硬件電路設計:如何確保嵌入式數據可靠性?

【深度解析】硬件電路設計:如何確保嵌入式數據可靠性?

評論