經(jīng)過(guò)這幾年的市場(chǎng)磨礪,Zynq-7000 FPGA SoC器件平臺(tái)在開發(fā)者中的認(rèn)知度和接受度越來(lái)越高,這種“ARM處理器+可編程邏輯”的創(chuàng)新架構(gòu),可以幫助開發(fā)者在設(shè)計(jì)中找到高性能與靈活性的完美平衡,對(duì)此大家也心知肚明。

但是在實(shí)際的應(yīng)用中,想要玩轉(zhuǎn)Zynq這種“異構(gòu)”平臺(tái),并非信手拈來(lái)這樣簡(jiǎn)單。其中很大的一個(gè)原因就是以往的開發(fā)工具都是彼此分立且松散連接的,設(shè)計(jì)和實(shí)現(xiàn)效率不高,因此需要一種全新的設(shè)計(jì)方法和開發(fā)工具來(lái)支持Zynq的應(yīng)用開發(fā)。

Xilinx推出的Vivado設(shè)計(jì)套件恰好能夠滿足這一需求。Vivado是一種以IP和系統(tǒng)為中心、支持7系列以及更新系列器件的(包括7系列FPGA、Zynq-7000 AP SoC、UltraScale / UltraScale Plus FPGA、Zynq US+ MPSoC等)全新集成開發(fā)環(huán)境,可解決用戶在系統(tǒng)級(jí)集成和實(shí)現(xiàn)過(guò)程中常見的生產(chǎn)力瓶頸問(wèn)題。Vivado目前最新的HLx版本可為設(shè)計(jì)團(tuán)隊(duì)提供實(shí)現(xiàn)基于C的設(shè)計(jì)、重用優(yōu)化、IP子系統(tǒng)復(fù)用、集成自動(dòng)化以及設(shè)計(jì)收斂加速所需的工具和方法,結(jié)合UltraFast高層次生產(chǎn)力設(shè)計(jì)方法,可幫助設(shè)計(jì)人員以高層次抽象形式開展工作,加速高層次設(shè)計(jì)、驗(yàn)證和實(shí)現(xiàn)。

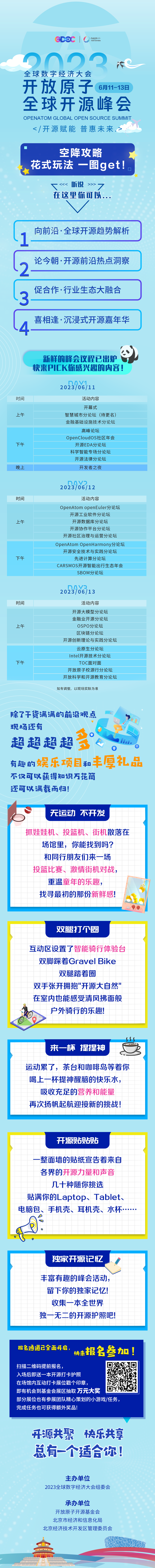

圖1,Zynq全可編程平臺(tái)設(shè)計(jì)開發(fā)流程

在近日舉辦的安富利MiniZed Speedway培訓(xùn)活動(dòng)中,一個(gè)重要的議程就是:如何幫助開發(fā)者使用Vivado設(shè)計(jì)套件創(chuàng)建一個(gè)符合用戶設(shè)計(jì)需求的Zynq-7000硬件平臺(tái)。

與傳統(tǒng)的處理器不同,Zynq平臺(tái)的處理器系統(tǒng)(PS)包含一系列常用的外設(shè)資源(如I2C、UART、CAN、GPIO、SPI、USB 2.0、Ethernet MAC、SDIO等)以及多端口DRAM Controller(可支持DDR2、DDR3/3L或LPDDR2顆粒組成一個(gè)16-bit或32-bit的存儲(chǔ)器系統(tǒng))。而且,PS通過(guò)專用的端口可以直接和可編程邏輯(PL)進(jìn)行通信和數(shù)據(jù)共享,使用PL可以創(chuàng)建用戶自定義IP,擴(kuò)展PS的外設(shè)和處理能力。雖然說(shuō)PS可以在沒(méi)有任何PL編程的情況下使用,但是為了充分利用PL中的軟IP資源,或者完成PS特定的外設(shè)與PL器件引腳間的連接布線,對(duì)PL的編程還是必要的。這也是Zynq平臺(tái)硬件設(shè)計(jì)不同于和優(yōu)于傳統(tǒng)處理器的重要特征。

在為期一天的MiniZed Speedway培訓(xùn)中,安富利講師詳細(xì)講解了Zynq-7000 SoC的系統(tǒng)架構(gòu),硬件開發(fā)的設(shè)計(jì)流程,核心的知識(shí)點(diǎn)包括:

Zynq-7000 SoC的架構(gòu)

Xilinx嵌入式設(shè)計(jì)工具和設(shè)計(jì)流程

如何使用Vivado IPI配置PS、外設(shè)以及PS和PL之間的接口

如何使用Vivado IP Package創(chuàng)建一個(gè)用戶自定義IP

如何使用ILA和硬件管理器(Hardware Manger)調(diào)試用戶自定義IP

與此同時(shí),安富利還為本次培訓(xùn)精心準(zhǔn)備了實(shí)操性的實(shí)驗(yàn)環(huán)節(jié),指導(dǎo)開發(fā)者完成硬件設(shè)計(jì)中的關(guān)鍵環(huán)節(jié)。例如:

創(chuàng)建一個(gè)基礎(chǔ)的Zynq設(shè)計(jì)項(xiàng)目

使用Vivado IP Integrator (IPI)配置PS

在Zynq設(shè)計(jì)中添加基于PL的外設(shè)

使用PS DMA優(yōu)化PS和PL之間的數(shù)據(jù)流程

使用Vivado IP Packager創(chuàng)建一個(gè)用戶自定義IP

使用Vivado Hardware Manager調(diào)試基于PL的用戶自定義IP

可以看到,培訓(xùn)中“手把手”地介紹了Zynq硬件平臺(tái)配置過(guò)程中Vivado的一些核心子工具的特性和使用方法,如Vivado IP集成器(IPI)。IPI可提供圖形化的基于Tcl、自動(dòng)連線、自動(dòng)檢查和糾正錯(cuò)誤(correct-by-construction)的開發(fā)流程,可提供具有器件和平臺(tái)意識(shí)的互動(dòng)環(huán)境,能支持關(guān)鍵IP接口的智能自動(dòng)連接、一鍵式IP子系統(tǒng)生成、實(shí)時(shí)DRC等功能,此外還提供強(qiáng)大的調(diào)試功能。在IP之間建立連接時(shí),設(shè)計(jì)人員工作在“接口(Interface)”而不是“信號(hào)(Signal)”的抽象層面上,能充分利用IP資源快速組裝復(fù)雜系統(tǒng),從而大幅提高了生產(chǎn)力。通過(guò)利用Vivado中IPI和HLS(高層次綜合)工具的完美組合,客戶的開發(fā)效率相對(duì)于傳統(tǒng)的RTL方式可提高數(shù)倍之多。

總之,按照MiniZed Speedway培訓(xùn)展示的“套路”,熟悉了Vivado這樣高效的設(shè)計(jì)工具,掌握了系統(tǒng)的設(shè)計(jì)方法,釋放出Zynq全可編程平臺(tái)的硬件潛能,并非難事!

-

FPGA

+關(guān)注

關(guān)注

1662文章

22469瀏覽量

638116 -

Zynq

+關(guān)注

關(guān)注

10文章

631瀏覽量

49528

發(fā)布評(píng)論請(qǐng)先 登錄

怎么集齊7個(gè)云平臺(tái)?本文教你!

【圖文教程】菜鳥教你如何一步一步免費(fèi)建一個(gè)網(wǎng)站!

玩轉(zhuǎn)Zynq連載19——[ex02]基于Zynq PL的歡快流水燈

玩轉(zhuǎn)Zynq連載28——[ex50] 第一個(gè)Zynq系統(tǒng)工程“Hello Zynq”

玩轉(zhuǎn)Zynq連載29——[ex51] 制作裸跑程序的啟動(dòng)文件BOOT.bin

玩轉(zhuǎn)Zynq連載30——[ex52]基于Zynq PS的GPIO控制

玩轉(zhuǎn)Zynq連載31——[ex53] 基于Zynq PS的EMIO控制

一篇小短文教你了解工字電感的各項(xiàng)參數(shù)

手把手教你keil+C51使用調(diào)試仿真中文教程

一文知道Zynq平臺(tái)運(yùn)行SDK程序錯(cuò)誤的解決辦法

一文教你怎么測(cè)量壓敏電阻的好壞

通過(guò)一個(gè)案例教你玩轉(zhuǎn)MCU代碼生成工具(基于STM32)

一文教你如何玩轉(zhuǎn)Zynq平臺(tái)

一文教你如何玩轉(zhuǎn)Zynq平臺(tái)

評(píng)論