?前一章詳解了DAC靜態(tài)參數(shù)計(jì)算,從偏移誤差、增益誤差到INL/DNL,再到未調(diào)整總誤差(TUE),一文掌握D/A轉(zhuǎn)換器的關(guān)鍵性能指標(biāo)。

【前文回顧】技術(shù)干貨 | DAC靜態(tài)參數(shù)計(jì)算全解析:從偏移誤差到總未調(diào)整誤差-CSDN博客

本章將介紹ATX7006上的線性計(jì)算和AD/DA的動(dòng)態(tài)分析:

ATX7006上的線性計(jì)算

可使用命令CALC_LIN在ATX7006上進(jìn)行線性度計(jì)算。線性度計(jì)算可針對從DIO模塊(A/D轉(zhuǎn)換器測試)或WFD(D/A轉(zhuǎn)換器測試)采集的數(shù)據(jù)進(jìn)行。

線性度計(jì)算可通過以下命令配置:

●CALCOPT_LIN_AD:最佳擬合/端點(diǎn)計(jì)算(ADC測試)、跳變點(diǎn)搜索方法、斜坡削波。

● CALCPARAM_LIN_AD:ADC參數(shù)、施加的輸入信號參數(shù)。

●CALCPARAM_LIN_AD_EXT:1/2LSB偏移量、接口偏移和增益參數(shù)。

●CALCOPT_LIN_DA:最佳擬合/端點(diǎn)計(jì)算(DAC測試)。

● CALCPARAM_LIN_DA:DAC位數(shù)、施加的輸入信號參數(shù)、接口偏移和增益參數(shù)。

可通過以下命令獲取結(jié)果:

● MR_LIN:積分非線性誤差(INLE)、差分非線性誤差(DNLE)、總未調(diào)整誤差(TUE)、偏移、增益等。

● MR_LIN_ERR_AD:ADC誤差繪圖數(shù)組結(jié)果。

● MR_LIN_MC:ADC缺失碼數(shù)組結(jié)果。

● MR_LIN_TRIP:ADC跳變點(diǎn)數(shù)組結(jié)果。

● MR_LIN_ERR_DA:DAC誤差繪圖數(shù)組結(jié)果。

當(dāng)系統(tǒng)處于“生產(chǎn)模式”時(shí),在測試(MX)后將進(jìn)行計(jì)算。使用命令PMODE將系統(tǒng)設(shè)置為生產(chǎn)模式。在斜坡測試、MT1(A/D測試)或MT11(D/A測試)后進(jìn)行線性度計(jì)算。可使用命令M查詢結(jié)果。

TS-ATX7006

ATView7006的WaveAnalyzer也可進(jìn)行線性度分析。按下相應(yīng)按鈕(如B.FIT、TUE、ENDP等)。可從菜單“Options選項(xiàng)”->“LinearityMeasurementSettings線性度測量設(shè)置”調(diào)整設(shè)置。

AD/DA的動(dòng)態(tài)分析

1、傅立葉變換

1.1簡介

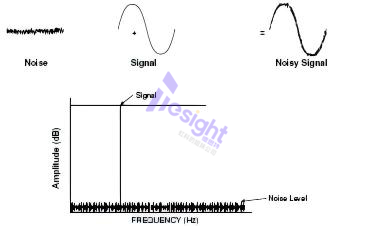

動(dòng)態(tài)測試是鑒定A/D和D/A轉(zhuǎn)換器的方法之一。將信號(主要是正弦波)施加到被測設(shè)備上,然后使用傅立葉變換算法分析捕獲的結(jié)果。本章將介紹有關(guān)傅立葉變換算法的一些背景信息。

1.2實(shí)驗(yàn)

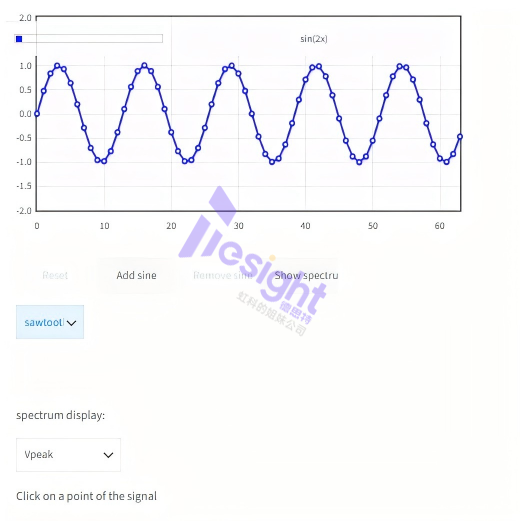

在現(xiàn)實(shí)生活中,每個(gè)信號都是正弦波之和。下圖將更清楚地說明這一點(diǎn)。例如,選擇鋸齒波信號并按下“添加正弦波”按鈕。添加的正弦波越多,信號就越像鋸齒波信號。數(shù)學(xué)公式顯示在圖表的右上角。要顯示信號的頻譜,請按“顯示頻譜”按鈕。方波和三角波也可重復(fù)此實(shí)驗(yàn)。

1.3原理

傅立葉變換基本上是將信號(分析)與不同頻率的正弦波和余弦波進(jìn)行比較。數(shù)學(xué)比較由乘積求和組成(例如,結(jié)果=信號*sin(x)+信號*sin(2x)+......等)。對采樣數(shù)據(jù)(N個(gè)樣本)進(jìn)行(離散)傅立葉變換(或DFT)需要N*N次運(yùn)算。不過,有一種將信號轉(zhuǎn)換為頻譜的更快方法。如果采樣個(gè)數(shù)是2的冪次,則可以執(zhí)行(弧度2)快速傅立葉變換(FFT)。運(yùn)算次數(shù)減少為N*log(N)。弧度為4的FFT算法甚至?xí)煲恍枰?次冪采樣。

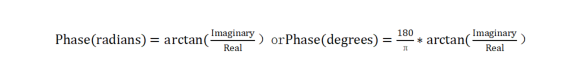

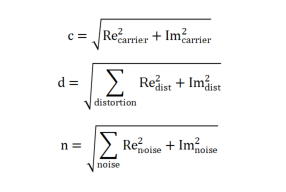

FFT或DFT的結(jié)果包括虛部和實(shí)部。虛部是正弦比較的結(jié)果,實(shí)部是余弦比較的結(jié)果。只進(jìn)行正弦比較也稱為離散正弦變換(DST)。只有余弦的比較也稱為離散余弦變換(DCT)。在上圖中可以看到虛部和實(shí)部。這些數(shù)據(jù)元素已歸一化,即除以N(樣本數(shù))。相位是虛部和實(shí)部之間的夾角=arctan(虛/實(shí))。

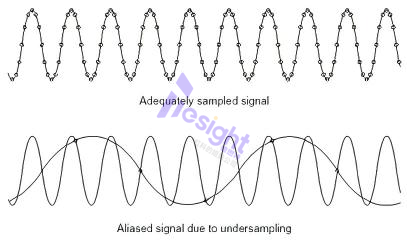

要檢測信號的實(shí)頻,采樣頻率必須至少為2*符號頻率。因此,如果每個(gè)正弦的采樣次數(shù)等于或小于2,傅立葉變換就無法檢測到信號的實(shí)際頻率。頻率高于采樣頻率的一半(或小于2個(gè)采樣/正弦)將在頻譜中顯示為鏡像信號。如圖所示:按下“顯示頻譜Showspectrum”按鈕并添加正弦信號。鋸齒波的第六個(gè)正弦波(或方波的第三個(gè)正弦波)將顯示為鏡像頻率。

頻譜輸出

傅立葉變換的結(jié)果將轉(zhuǎn)化為可讀數(shù)據(jù)。上圖可以以不同方式顯示傅立葉變換的結(jié)果:

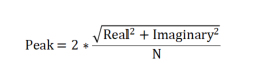

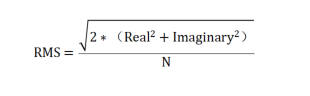

Vpeak:峰值電壓(或代碼)的計(jì)算公式為:

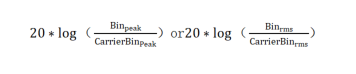

dBc:dBc表示相對于載波的分貝。因此載波始終為0dB。每個(gè)頻譜分區(qū)的dBc值由以下公式計(jì)算得出:

相位:每個(gè)頻譜分區(qū)的相位計(jì)算公式為:

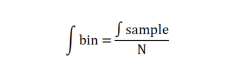

頻率分辨率:X軸的頻率分辨率或步長由采樣頻率和采樣數(shù)量決定:

2、動(dòng)態(tài)參數(shù)計(jì)算

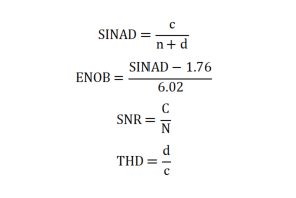

根據(jù)頻譜結(jié)果可以計(jì)算出以下參數(shù):

其中:

其中,c代表載波頻段的幅度(即“信號”),d代表所有失真頻段的總和,n代表所有噪聲頻段的總和。載波頻段的位置等于在采集窗口內(nèi)載波的周期數(shù)。在圖中,周期數(shù)為5,載波的頻段位置為5(分區(qū)0為直流分量)。

2.1信納比(SINAD)與有效位數(shù)(ENOB)

信納比(SINAD)指信號與噪聲及失真之比,是信號(或載波)與所有其他頻譜頻段的比值。有效位數(shù)(ENOB)由SINAD計(jì)算得出。對于輸入滿量程正弦波輸入的線性ADC,其理論最大信納比由量化噪聲(或DAC的分辨率)決定,約為6.02n+1.76dB。在一個(gè)完全線性但有噪聲的系統(tǒng)中,信納比(SINAD)和信噪比(SNR)可互換。

2.2信噪比(SNR)

信噪比(SNR)指信號(或載波)與所有噪聲頻段的比值。噪聲頻段是指除載波、諧波或直流以外的所有頻段。

隨著頻率升高,信噪比通常會降低,因?yàn)锳DC內(nèi)比較器在較高輸入轉(zhuǎn)換速率下精度會下降,這種精度損失在ADC輸出端表現(xiàn)為噪聲。在A/D轉(zhuǎn)換器中,噪聲主要來自四個(gè)方面:(1)量化噪聲;(2)轉(zhuǎn)換器自身產(chǎn)生的噪聲;(3)應(yīng)用電路噪聲;(4)抖動(dòng)。

量化噪聲源于量化過程,即給一系列輸入值分配輸出代碼的過程。量化噪聲的幅度隨分辨率提高而降低,因?yàn)樵诟叻直媛氏翷SB的大小更小,從而減小了最大量化誤差。對于輸入滿量程正弦波的線性ADC,其理論最大信噪比由量化噪聲(對于DAC則是分辨率)決定,定義為),約為6.02n+1.76dB。在完全線性但有噪聲的系統(tǒng)中,信納比(SINAD)和信噪比(SNR)可互換。

應(yīng)用電路噪聲是由于電路設(shè)計(jì)和布局方式,轉(zhuǎn)換器所感知到的噪聲。在輸入接近滿量程之前,信噪比隨輸入幅度增加而增大。在輸入信號接近滿量程之前,信噪比與輸入信號以相同速率增加,即輸入信號幅度增加1dB會使信噪比增加1dB。這是因?yàn)殡S著信號幅度增大,步長在總信號幅度中所占比例變小。然而,當(dāng)輸入幅度開始接近滿量程時(shí),信噪比相對于輸入信號的增加速率會下降。

在較高頻率下,由于抖動(dòng)的影響加劇,信噪比性能會降低。

2.3總諧波失真(THD)

總諧波失真(THD)是失真頻段與信號(或載波)的比值。諧波是載波的倍數(shù)。可通過命令CALCOPT_DYN的參數(shù)o配置被認(rèn)定為諧波的頻段數(shù)量,默認(rèn)諧波頻段數(shù)量為7。諧波可能是鏡像頻段。

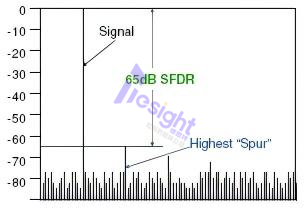

2.4無雜散動(dòng)態(tài)范圍(SFDR)

無雜散動(dòng)態(tài)范圍是指信號與頻譜中峰值最高的任何其他信號(雜散信號)之間的dB差值。

2.5峰值失真

指最高的失真頻段。

-

半導(dǎo)體測試

+關(guān)注

關(guān)注

4文章

133瀏覽量

20070

發(fā)布評論請先 登錄

ATX電源維修技術(shù)

臺式計(jì)算機(jī)ATX開關(guān)電源檢修技巧

邊緣計(jì)算 智能視頻分析技術(shù)

UART串口與LWIP以太網(wǎng)問題解析

ATX計(jì)算機(jī)電源的相關(guān)資料推薦

線性動(dòng)態(tài)電路的時(shí)域分析的詳細(xì)資料說明

UM-WI-030 DA16200 DA16600 DPM動(dòng)態(tài)周期設(shè)置

技術(shù)干貨-鳳凰動(dòng)力為你解析AGV各種驅(qū)動(dòng)配置的優(yōu)勢對比

高精度、低噪聲、快速采樣——虹科ADC/DAC芯片測試平臺

技術(shù)干貨 | ATX7006線性計(jì)算與AD/DA動(dòng)態(tài)分析解析

技術(shù)干貨 | ATX7006線性計(jì)算與AD/DA動(dòng)態(tài)分析解析

評論