一、簡要概述

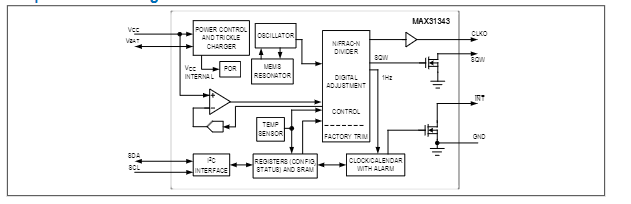

D8563時鐘芯片,是一款具有高精度時鐘與日歷功能的芯片,它能夠提供準確的時鐘和日歷信息,包括年、月、日、星期、小時、分鐘和秒等。這款芯片采用低功耗設計,使得在待機狀態下功耗極低,有助于延長電池壽命,特別適合用于便攜式設備或長時間運行的系統。此外,8563芯片還具備鬧鐘與定時器功能,通過I2C通信接口與外部設備進行通信,具有高速率的特點,使得數據交換更加高效。因此,它在智能家居系統中可用于控制設備的定時開關、報警提醒等功能,提高家居生活的便捷性和安全性。在嵌入式設備中,8563提供準確的時間戳和日歷信息,支持設備的時間同步和事件記錄。在便攜式儀器儀表中,由于其低功耗特性,能夠長時間穩定工作,為設備提供準確的時間基準。在工業控制系統中,用于記錄生產過程的時間信息,確保生產數據的準確性和可追溯性?。

此外,8563芯片還廣泛應用于電表、水表、氣表、電話、傳真機、便攜式儀器以及電池供電的儀器儀表等產品領域;

D8563采用DIP8、SOP8、TSSOP8、MSOP8、DFN8的封裝形式封裝;

二、應用領域

D8563實時時鐘芯片主要應用于需要顯示時間、或者需要記錄、計算時間的場合,日歷時鐘信號的場合,如手機(移動電話)、真機、空調開關(帶顯示屏)、點讀筆、復讀機;及其他使用電池作總電源的便攜式設備,如智能家居控制遙控器,家用醫療儀器、依表等;

三、硬件電路設計及調試

1、晶體選擇及負載電容匹配

RTC芯片主要起分頻和計時作用,時間的精度和頻率源依靠外部晶體提供,所以晶體對時鐘精度來說至關重要,必須選擇與RTC芯片相匹配的晶體才能保證時間的精度和穩定性。

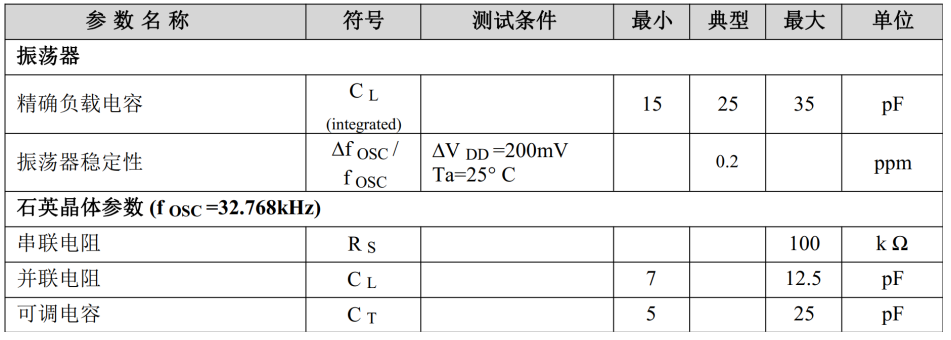

D8563內部振蕩器參數及對外部晶體參數的要求如下:

D8563內部兩引腳都集成了5pF的負載電容,如使用負載電容為6pF的32.768KHz晶體,則建議在OSCI、OSCO腳連接約6pF匹配電容(理論推薦值)開始調試,如使用負載電容為12.5pF的32.768KHz晶體,則建議在OSCI、OSCO腳連接約19pF開始調試;如無法判斷外部負載電容的相關參數,建議初始值為20pF+/-2pF,將示波器打至10X衰減檔進行測量,再增減電容值進行調試;

舉例:某客戶使用我司D8563,要求一天內只允許誤差0.5S;一天有86400S,那晶體要做到0.5/86400=5.78PPM,考慮到溫度等其他影響因素,客戶至少需要購買精度5%以下的晶體;

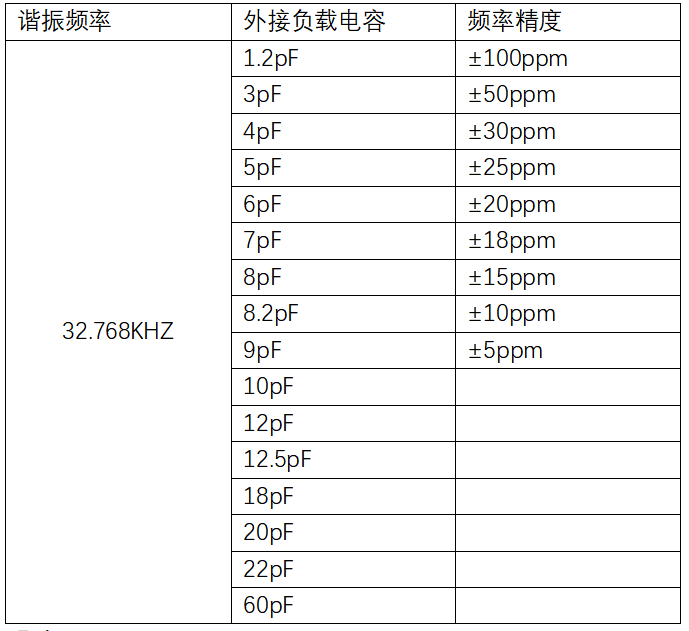

如下為電子商城常見的頻率為32.768KHZ的晶體相關參數

2、諧振頻率調試

由于D8563是低功耗時鐘芯片,其晶體的振蕩幅度非常小,大約只有0.3~0.5V左右,不建議使用示波器或萬用表直接在晶體的兩個引腳上測量頻率及電壓;

D8563有一個選項,將輸出設置寄存器地址0DH為80H,即可在CLKOUT引腳觀察到頻率來調整匹配電容,直到輸出精確的32.768KHz。

調試原則:時間走得太快,增大匹配電容值;時間走得太慢,減小匹配電容值;

四、PCB布局布線注意事項:

1.整體布局要緊湊不要太分散,晶振、匹配電容位于MCU同側;

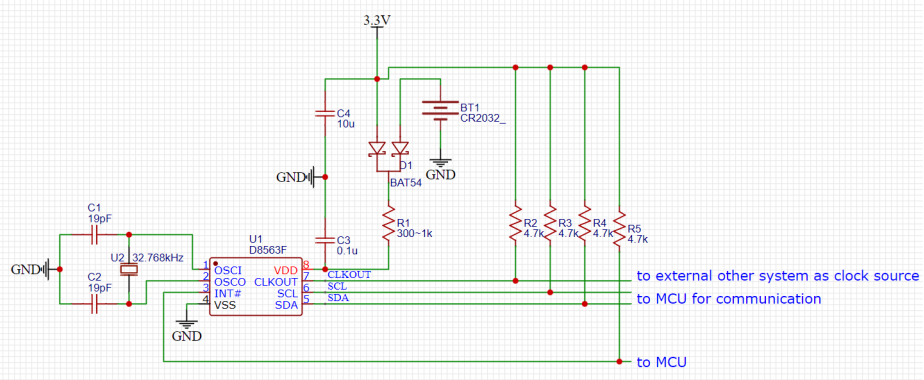

2.建議在繪制原理圖時添加0.1uF的退耗電容,并就近供電腳放置,以濾除電源線上不干凈的噪聲或干擾信號,如需進一步濾波,建議電源線上串上300~1K的電阻組成一階RC濾波;

3.晶體盡量靠近OSCI和OSCO腳,走線越短越好,走線寬度建議8~12mil,負載電容位于兩旁形成對稱,類似差分走線,將分布電容和干擾減小到最低;

4.晶體盡量包地,附近設一定面積的禁空區防止外部信號干擾,晶體下方所有層原則上不建議走線,防止相互干擾;

審核編輯 黃宇

-

I2C

+關注

關注

28文章

1547瀏覽量

130578 -

時鐘芯片

+關注

關注

2文章

284瀏覽量

41951

發布評論請先 登錄

芯伯樂PCF8563:0.25μA低功耗實時時鐘解決方案

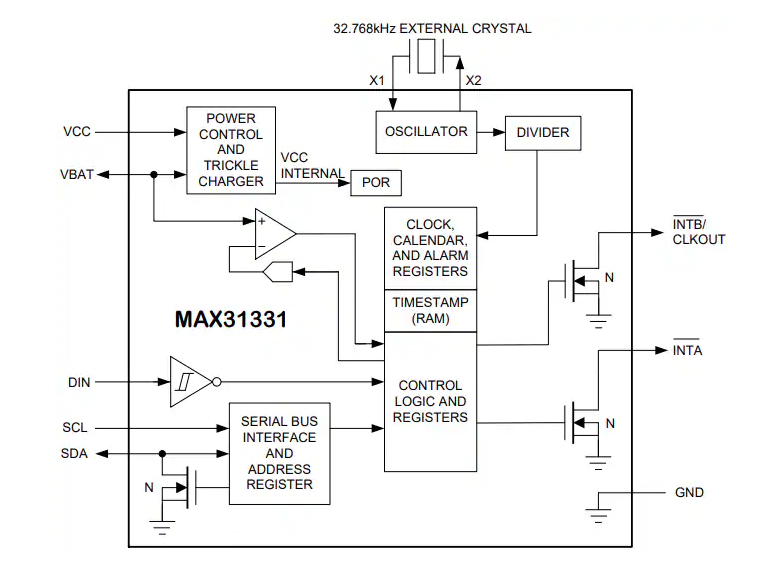

Analog Devices / Maxim Integrated MAX31331超低功耗I2C實時時鐘數據手冊

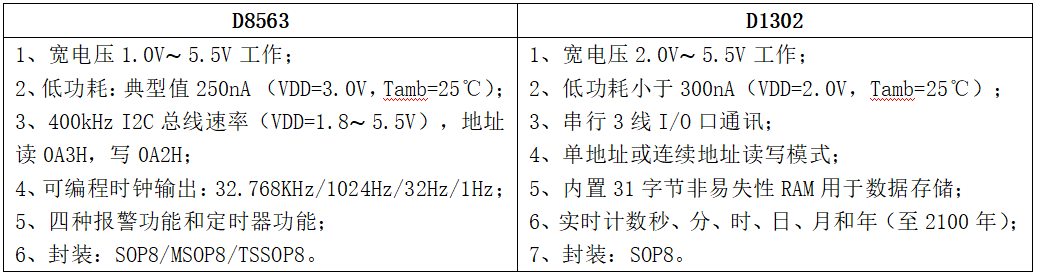

RTC實時時鐘芯片D8563和D1302簡介

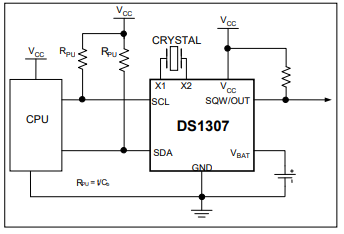

DS1307 64 x 8、串行、I2C實時時鐘技術手冊

DS3232M ±5ppm、內置SRAM的I2C實時時鐘技術手冊

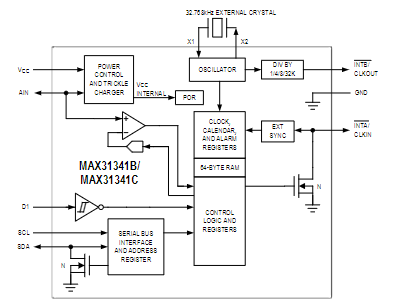

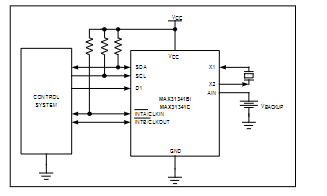

MAX31341C低電流、實時時鐘,具有I2C接口和電源管理技術手冊

MAX31341B低電流、實時時鐘,具有I2C接口和電源管理技術手冊

MAX31343集成MEMS振蕩器的±5ppm、I2C實時時鐘技術手冊

I2C總線通信原理 如何設計I2C總線電路

I2C總線與Arduino的接口示例

I2C總線的工作模式介紹

I2C總線協議詳細解析

I2C總線應用實例分析

RTC實時時鐘PCF8563T/5國產替代FTRC8563S

I2C通訊的實時時鐘芯片D8563

I2C通訊的實時時鐘芯片D8563

評論