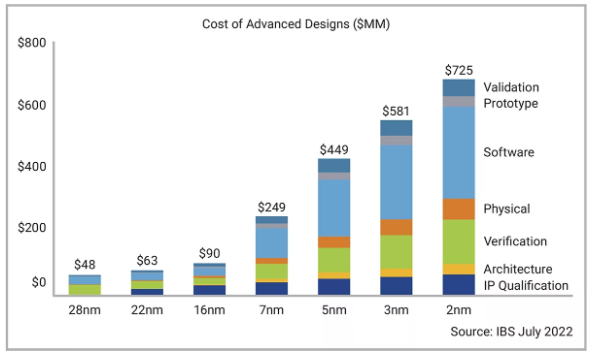

在高性能計算、邊緣物聯網、人工智能和云計算等應用領域,要確保先進SoC設計的安全性與正確配置,一次性可編程(OTP)非易失性內存(NVM)至關重要。隨著這些技術朝著先進FinFET節點發展,OTP NVM的重要性愈發顯著。OTP內存可安全存儲數據、敏感程序代碼、產品信息以及用于身份驗證的加密密鑰。先進FinFET節點的設計、掩模和晶圓成本急劇攀升(圖1),使得一次性流片成功比以往任何時候都更為重要,而IP可靠性正是實現該目標的關鍵所在。新思科技OTP NVM IP解決方案專為7nm及以下工藝打造,能在各種工藝、電壓和溫度(PVT)條件下安全可靠地運行,是確保一次性流片成功的關鍵因素。

▲先進工藝節點的掩模、晶圓和設計成本持續攀升

01

反熔絲OTP的基本工作原理

反熔絲OTP由大量OTP存儲單元組成陣列,每個存儲單元均由CMOS晶體管構成。在反熔絲OTP中,未編程的存儲單元代表邏輯0,已編程的存儲單元代表邏輯1。OTP剛生產出來時,所有存儲單元都處于未編程狀態,即邏輯0狀態。對反熔絲OTP進行編程時,需要向編程的位置(目標存儲單元)施加高電壓。高電壓會使氧化層擊穿,在其中形成微通道。事實上微通道目的在于構成OTP 存儲單元的晶體管在柵極與襯底之間形成短路。微通道允許電流能在晶體管的柵極和襯底之間導通,并且該電流可測量。讀取OTP時,需測量柵極漏電流,以確定存儲單元是已編程(邏輯1)還是未編程(邏輯0)。該過程需要使用高于核心供電電壓(core voltage)的穩定電壓,以便在位線上獲得足夠的電流,從而可靠地讀取數據。

02

先進節點OTP的可靠性挑

工作電壓下的可靠讀取

在氧化層更薄的先進節點中,以高于核心供電電壓的穩定電壓讀取OTP,會增加錯誤讀取的概率,即使未編程的位也可能被誤讀為邏輯1。較薄的氧化層還會使讀取的字節內未編程存儲單元承受更高的器件應力。

確保高編程良率

先進節點工藝的器件漏電流更高,需要更高的電壓來驅動足夠的電流以便對OTP進行編程。但高電壓可能損壞器件,導致編程失敗。由于氧化層較薄,先進節點OTP更易受高電壓影響,可能出現過度編程。OTP過度編程會導致編程質量不佳,還會使存儲單元不必要地過度暴露于高電壓之下。另外,高電壓可能引發編程干擾,導致相鄰的存儲單元被意外編程,從而造成錯誤。

PPA挑戰

較大的漏電流會極大地增加OTP保持面積競爭力的難度,可能限制其能夠可靠支持的最大容量。編程時間也是影響制造總成本的一個因素。對OTP進行編程需要大幅提高電壓,而先進節點供電電壓較低,因此需要更長的時間才能將電壓提升到所需的電壓值,以驅動編程電流并成功對OTP進行編程。

03

適用于先進節點設計的

可靠反熔絲OTP解決方案

優化存儲單元設計

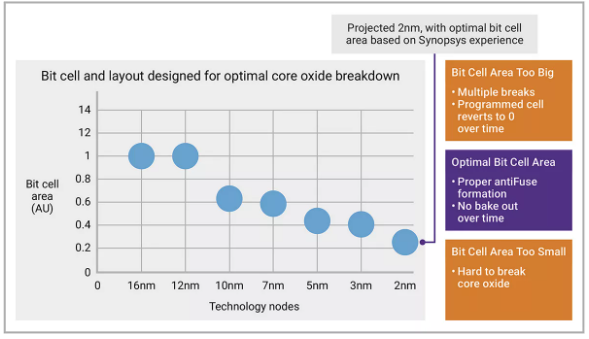

存儲單元設計是可靠性的基礎。編程時形成的微通道質量取決于氧化層的擊穿程度,而這又與存儲單元面積相關。如果面積過小,擊穿氧化層、形成微通道就會非常困難,進而導致編程失敗。面積過大的話,編程時氧化層可能多處斷裂。弱擊穿(擊穿不足)會導致微通道形成不完全,強擊穿則會產生多條能傳導電流的微通道。弱擊穿形成的微通道不完全,可能無法傳導足夠大的電流。隨著時間推移,這些存儲單元可能會像未編程的存儲單元一樣,這種現象被稱為“烘烤失效”。在存儲單元較大的OTP中,未編程位置因尺寸問題可能會出現較高漏電流,影響存儲陣列的“空白良率”,也就是生產后首次測試時處于邏輯0狀態的位數占比。因此,必須仔細選擇存儲單元面積,以便優化編程時微通道的形成,防止“烘烤失效”,確保編程性能可靠。

OTP讀取和編程都需要高電壓,該電壓由集成電源(IPS)產生和調節,而IPS本質上是純模擬電路。IPS設計對于OTP的正常運行至關重要。如果用于實現可靠讀取和編程的電壓出現波動,會導致數據保存問題或編程干擾。

模擬設計針對編程和讀取路徑進行了優化,以實現氧化層強擊穿。通過對模擬元件進行精細設計,可確保在各種PVT條件下實現可靠讀取。

數據完整性信號

讀取時OTP輸出的數據必須始終可靠。確保讀取數據的完整性對于確定OTP存儲的整體可靠性至關重要。在讀取過程中,必須有信號指示OTP輸出是否有效,以防電壓不穩定造成數據意外損壞。

04

先進節點中的PPA優化

存儲陣列和模擬電路外設設計

在先進節點工藝中,高器件漏電流是常見問題。為確保OTP的可靠性,并達到期望的性能和功耗目標,必須采取干預措施。需要精心設計位線長度和存儲陣列寬度,避免OTP存儲工作時出現過大的IR壓降。此外,管理漏電功耗也非常重要。通過精心設計存儲陣列和模擬電路外設,可以滿足SoC要求。

優化模擬設計

感測放大器用于感測和確定所訪問OTP位置的值。與之前的FinFET節點相比,先進節點下從這些存儲單元流出的電流更低,因此感測放大器必須對常見的低電壓特別敏感。編程速度影響制造成本,需要通過專業的高壓電路設計來優化。但由于要同時滿足以下兩個相互沖突的要求,實現起來頗具挑戰性:一個是盡量減小OTP總面積,另一個是保證IPS中電荷泵提供足夠的電流,從而成功對內存進行編程。

05

針對先進節點開發的新思科技OTP NVM IP

可靠性設計

為滿足先進節點OTP的需求,新思科技OTP NVM IP從穩健性設計、反熔絲存儲單元優化入手(圖2)。高溫工作壽命(HTOL)測試表明,不同讀取點的存儲單元電流沒有變化,證明其在各種PVT條件下穩定可靠。新思科技優化了存儲單元面積,以實現正確的氧化層擊穿,從而確保了成功的可編程性、高編程性能和優異的陣列空白良率。

▲新思科技OTP NVM存儲單元針對反熔絲形成進行了優化

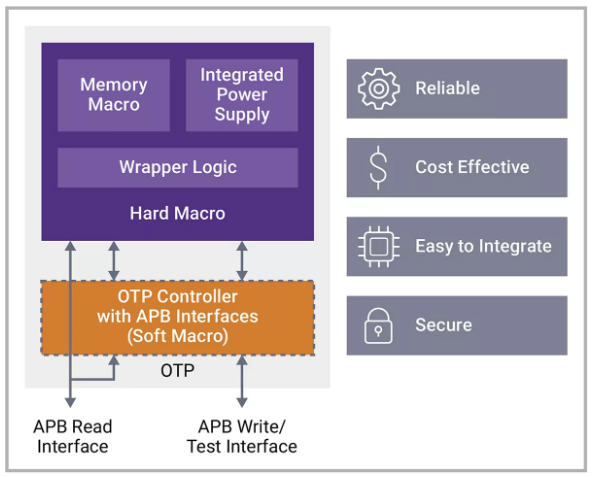

新思科技OTP NVM IP解決方案(圖3)包含由平鋪式存儲單元組成的存儲陣列、解碼器、模擬元件(如感測放大器),以及生成讀取和編程所需電壓的IPS。新思科技在設計OTP陣列時,降低了先進節點的漏電流。其選定的讀取電壓既能確保存儲單元可靠讀取,又能保證數據至少保存10年。編程電壓和編程的算法設計能夠防止意外的編程干擾。OTP上的輸出引腳有助于確保數據不會被提前讀取,從而確保數據的完整性。

▲針對先進節點開發的新思科技OTP NVM IP

新思科技OTP NVM IP通過附加位,進一步增強了應對隨機性制造缺陷和現場故障的能力。在初始測試期間,每個字節都能糾正漏電位和/或編程失敗錯誤。如果一個字節內出現多個錯誤,可使用額外的修復資源,必要時可替換整個字節。OTP存儲陣列還包含用于存儲糾錯碼(ECC)的附加位。

成本效益

新思科技OTP NVM IP提供多種容量選擇,開發者可以根據SoC的要求選擇最合適的OTP容量。該IP經過面積優化,降低了芯片成本,并且具備快速編程能力,從而降低生產成本。

易于集成

完整的OTP解決方案有一個控制器與新思科技OTP NVM交互,從而管理讀寫、測試、修復以及ECC編碼和解碼。該控制器以RTL形式作為軟IP交付,OTP存儲陣列和IPS集成在單個硬核中。為了進一步簡化SoC集成,OTP解決方案還支持標準APB接口。此外,OTP支持標準JTAG 1149.1接口,以便進行測試。交付項包含必要的綜合腳本和約束文件,以幫助最終用戶實現其設計中的OTP控制器。

高級安全架構

鑒于OTP在保障先進節點安全性方面發揮著關鍵作用,新思科技推出了一些穩固特性以用于增強安全性保護。每個字節都有讀取鎖、編程鎖,以及核級鎖和區塊級鎖。OTP編程和測試通過安全的APB接口進行,完成后可鎖定該接口,阻止非期望用戶訪問。

OTP支持低功耗模式,不使用時關閉存儲陣列和IPS,讓存儲的數據或代碼難以被電子竊取和逆向工程。在檢測到黑客攻擊時,它可對所有未編程的位置進行編程,實現數據混淆,從而有效阻擋嵌入式OTP的操作。

控制器實現的安全啟動功能確保OTP在鎖定狀態下喚醒,需要用戶明確操作才能改為可讀狀態。此外,OTP可配置為差分式讀取模式,使黑客難以根據功耗特征確定OTP存儲的值。

06

結語

在先進FinFET節點中,OTP對于配置和保護SoC至關重要。若選擇市場上欠可靠性的OTP IP,可能導致芯片失效,嚴重影響產品上市和市場份額。新思科技的OTP NVM IP從設計之初就追求高可靠性、PPA優化和高安全性。該IP提供了一套完整的解決方案,并包含一個數字控制器,方便開發者將其集成到目標設計中。新思科技OTP NVM IP已經過驗證,適用于7nm及更小的工藝節點。

-

soc

+關注

關注

38文章

4525瀏覽量

227809 -

IP

+關注

關注

5文章

1850瀏覽量

155037 -

OTP

+關注

關注

4文章

237瀏覽量

49239 -

新思科技

+關注

關注

5文章

930瀏覽量

52698 -

芯片架構

+關注

關注

1文章

32瀏覽量

14850

原文標題:先進 OTP IP 賦能高安全性 SoC 設計:構建抗篡改的可靠芯片架構

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

車規級與消費級芯片的可靠性、安全性與成本差異

芯源半導體安全芯片技術原理

抗輻照CANFD通信芯片在高安全領域國產化替代的研究

ESP32-P4—具備豐富IO連接、HMI和出色安全特性的高性能SoC

紫光同芯抗量子算法賦能電子證件

國產高安全芯片在供應鏈自主可控中的綜合優勢與案例分析

新思科技先進OTP IP賦能高安全性SoC設計:構建抗篡改的可靠芯片架構

新思科技先進OTP IP賦能高安全性SoC設計:構建抗篡改的可靠芯片架構

評論