單芯片解決方案,開啟全新體驗——W55MH32 高性能以太網(wǎng)單片機

W55MH32是WIZnet重磅推出的高性能以太網(wǎng)單片機,它為用戶帶來前所未有的集成化體驗。這顆芯片將強大的組件集于一身,具體來說,一顆W55MH32內(nèi)置高性能Arm? Cortex-M3核心,其主頻最高可達216MHz;配備1024KB FLASH與96KB SRAM,滿足存儲與數(shù)據(jù)處理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP協(xié)議棧、內(nèi)置MAC以及PHY,擁有獨立的32KB以太網(wǎng)收發(fā)緩存,可供8個獨立硬件socket使用。如此配置,真正實現(xiàn)了All-in-One解決方案,為開發(fā)者提供極大便利。

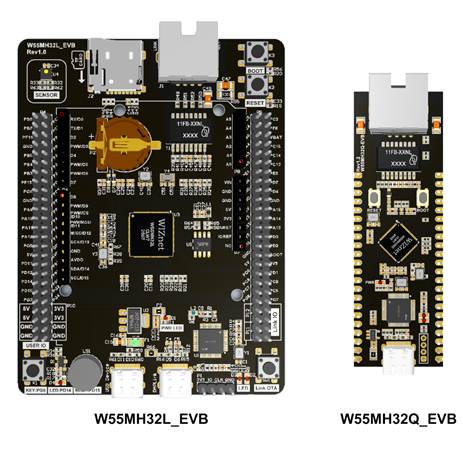

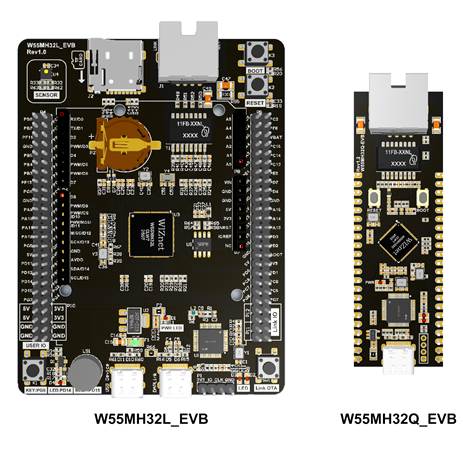

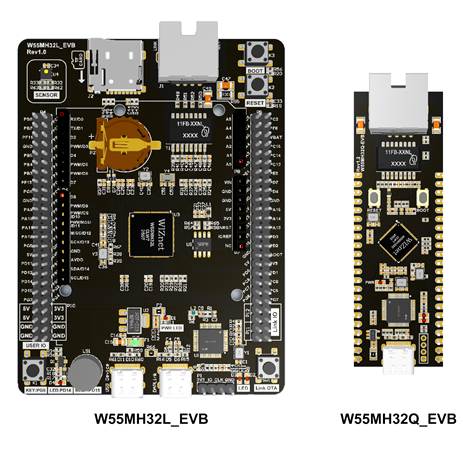

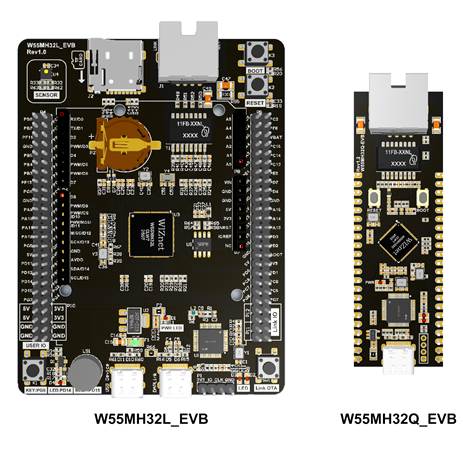

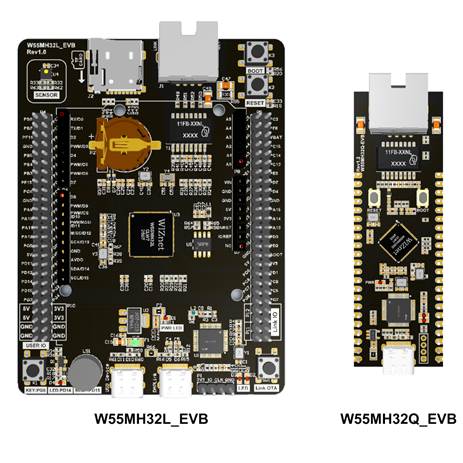

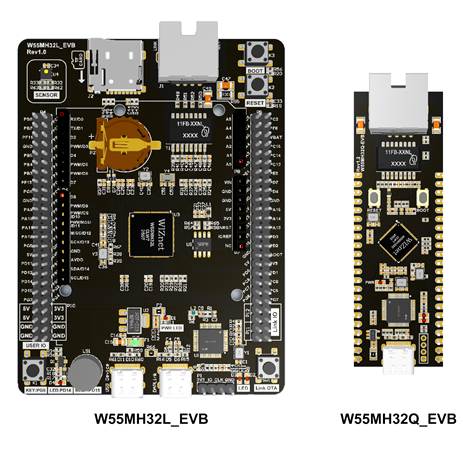

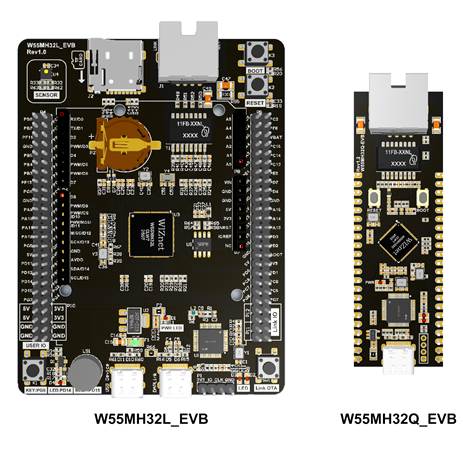

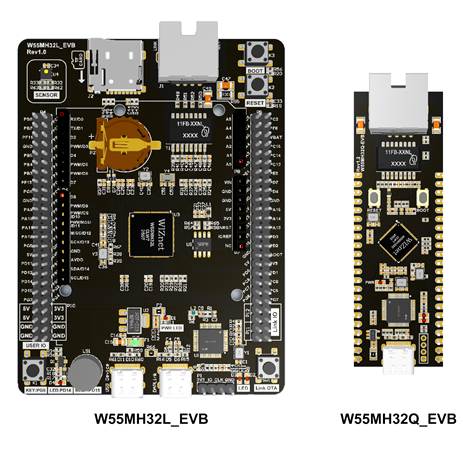

在封裝規(guī)格上,W55MH32 提供了兩種選擇:QFN68和QFN100。

W55MH32Q采用QFN68封裝版本,尺寸為8x8mm,它擁有36個GPIO、3個ADC、12通道DMA、17個定時器、2個I2C、3個串口、2個SPI接口(其中1個帶I2S接口復(fù)用)、1個CAN以及1個USB2.0。在保持與同系列其他版本一致的核心性能基礎(chǔ)上,僅減少了部分GPIO以及SDIO接口,其他參數(shù)保持一致,性價比優(yōu)勢顯著,尤其適合網(wǎng)關(guān)模組等對空間布局要求較高的場景。緊湊的尺寸和精簡化外設(shè)配置,使其能夠在有限空間內(nèi)實現(xiàn)高效的網(wǎng)絡(luò)連接與數(shù)據(jù)交互,成為物聯(lián)網(wǎng)網(wǎng)關(guān)、邊緣計算節(jié)點等緊湊型設(shè)備的理想選擇。 同系列還有QFN100封裝的W55MH32L版本,該版本擁有更豐富的外設(shè)資源,適用于需要多接口擴展的復(fù)雜工控場景,軟件使用方法一致。更多信息和資料請進入http://www.w5500.com/網(wǎng)站或者私信獲取。

此外,本W(wǎng)55MH32支持硬件加密算法單元,WIZnet還推出TOE+SSL應(yīng)用,涵蓋TCP SSL、HTTP SSL以及MQTT SSL等,為網(wǎng)絡(luò)通信安全再添保障。

為助力開發(fā)者快速上手與深入開發(fā),基于W55MH32Q這顆芯片,WIZnet精心打造了配套開發(fā)板。開發(fā)板集成WIZ-Link芯片,借助一根USB C口數(shù)據(jù)線,就能輕松實現(xiàn)調(diào)試、下載以及串口打印日志等功能。開發(fā)板將所有外設(shè)全部引出,拓展功能也大幅提升,便于開發(fā)者全面評估芯片性能。

若您想獲取芯片和開發(fā)板的更多詳細信息,包括產(chǎn)品特性、技術(shù)參數(shù)以及價格等,歡迎訪問官方網(wǎng)頁:http://www.w5500.com/,我們期待與您共同探索W55MH32的無限可能。

第十九章 PWR

本章介紹了W55MH32的電源控制(PWR)功能,其工作電壓2.0~3.6V,含電源管理器,有POR/PDR、PVD等。低功耗模式包括睡眠、停止、待機,介紹了相關(guān)例程,用于測試低功耗模式及喚醒功能。

1 電源介紹

W55MH32 的工作電壓(VDD)為 2.0~3.6V。通過內(nèi)置的電壓調(diào)節(jié)器提供所需的 1.8V 電源。當主電源 VDD 掉電后,通過 VBAT 腳為實時時鐘(RTC)和備份寄存器提供電源。

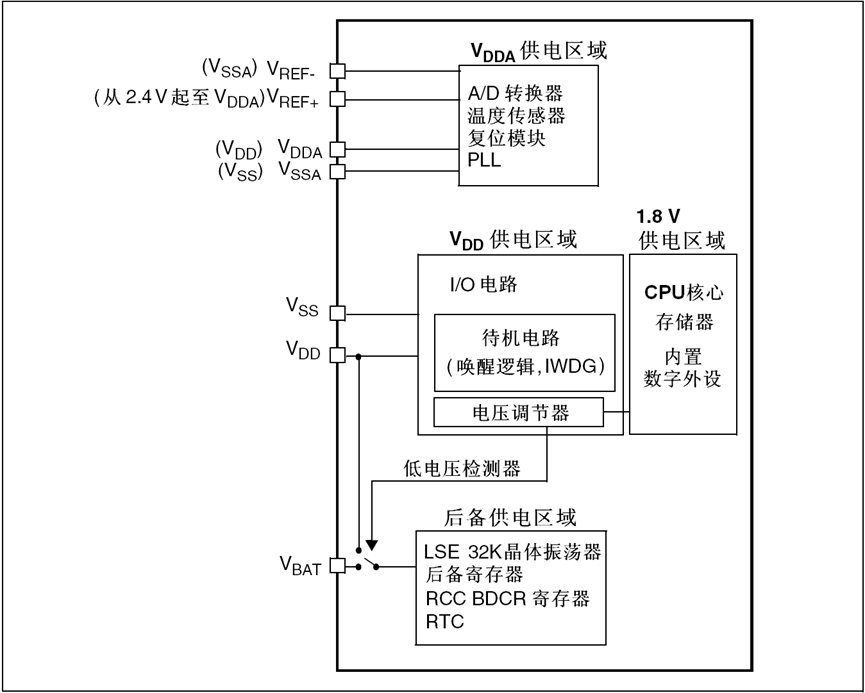

電源框圖

注:VDDA 和 VSSA 必須分別聯(lián)到 VDD 和 VSS。

1.1 獨立的 A/D 轉(zhuǎn)換器供電和參考電壓

為了提高轉(zhuǎn)換的精確度,ADC 使用一個獨立的電源供電,過濾和屏蔽來自印刷電路板上的毛刺干擾。

?ADC 的電源引腳為 VDDA

?獨立的電源地 VSSA

如果有 VREF-引腳(根據(jù)封裝而定),它必須連接到 VSSA。為了確保輸入為低壓時獲得更好精度,用戶可以連接一個獨立的外部參考電壓 ADC 到 VREF+和VREF-腳上。在 VREF+的電壓范圍為 2.4V~VDDA。

1.2 電池備份區(qū)域

使用電池或其他電源連接到 VBAT 腳上,當 VDD 斷電時,可以保存?zhèn)浞菁拇嫫鞯膬?nèi)容和維持 RTC的功能。

VBAT 腳為 RTC、LSE 振蕩器和 PC13 至 PC15 端口供電,可以保證當主電源被切斷時 RTC 能繼續(xù)工作。切換到 VBAT 供電的開關(guān),由復(fù)位模塊中的掉電復(fù)位功能控制。

警告:在 VDD 上升階段(tRSTTEMPO)或者探測到 PDR(掉電復(fù)位)之后,VBAT 和 VDD 之間的電源開關(guān)仍會保持連接在 VBAT。

在 VDD 上升階段,如果 VDD 在小于 tRSTTEMPO 的時間內(nèi)達到穩(wěn)定狀態(tài)(關(guān)于 tRSTTEMPO 數(shù)值可參考數(shù)據(jù)手冊中的相關(guān)部分),且 VDD>VBAT+0.6V 時,電流可能通過 VDD 和 VBAT 之間的內(nèi)部二極管注入到 VBAT。

如果與 VBAT 連接的電源或者電池不能承受這樣的注入電流,強烈建議在外部 VBAT 和電源之間連接一個低壓降二極管。如果在應(yīng)用中沒有外部電池,建議 VBAT 在外部連接到 VDD 并連接一個 100nF 的陶瓷濾波電容。

當備份區(qū)域由 VDD(內(nèi)部模擬開關(guān)連到 VDD)供電時,下述功能可用:

?PC14 和 PC15 可以用于 GPIO 或 LSE 引腳

?PC13 可以作為通用 I/O 口、TAMPER 引腳、RTC 校準時鐘、RTC 鬧鐘或秒輸出

注: 因為模擬開關(guān)只能通過少量的電流(3mA),在輸出模式下使用 PC13 至 PC15 的 I/O 口功能是有限制的:速度必須限制在 2MHz 以下,最大負載為 30pF,而且這些 I/O 口絕對不能當作電流源(如驅(qū)動 LED)。

當后備區(qū)域由 VBAT 供電時(VDD 消失后模擬開關(guān)連到 VBAT),可以使用下述功能:

?PC14 和 PC15 只能用于 LSE 引腳

?PC13 可以作為 TAMPER 引腳、RTC 鬧鐘或秒輸出

1.3 電壓調(diào)節(jié)器

復(fù)位后調(diào)節(jié)器總是使能的。根據(jù)應(yīng)用方式它以 3 種不同的模式工作。

?運轉(zhuǎn)模式:調(diào)節(jié)器以正常功耗模式提供 1.8V 電源(內(nèi)核,內(nèi)存和外設(shè))。

?停止模式:調(diào)節(jié)器以低功耗模式提供 1.8V 電源,以保存寄存器和 SRAM 的內(nèi)容。

?待機模式:調(diào)節(jié)器停止供電。除了備用電路和備份域外,寄存器和 SRAM 的內(nèi)容全部丟失。

2 電源管理器

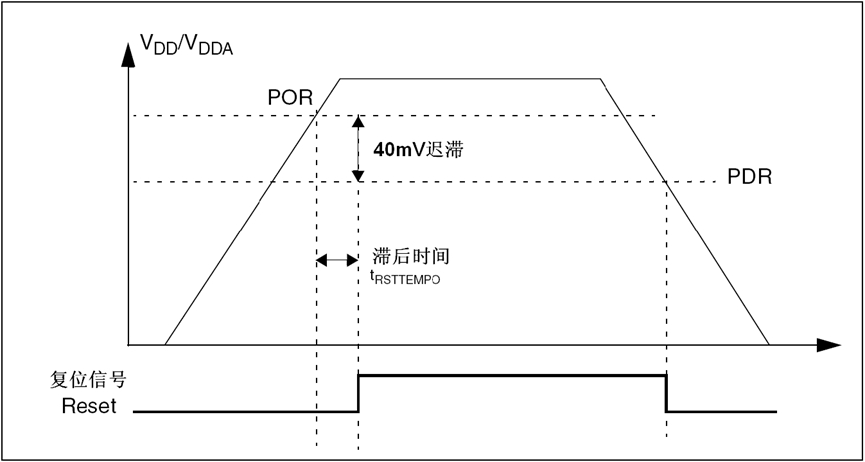

2.1 上電復(fù)位(POR)和掉電復(fù)位(PDR)

W55MH32 內(nèi)部有一個完整的上電復(fù)位(POR)和掉電復(fù)位(PDR)電路,當供電電壓達到 2V 時系統(tǒng)既能正常工作。

當VDD/VDDA低于指定的限位電壓VPOR/VPDR時,系統(tǒng)保持為復(fù)位狀態(tài),而無需外部復(fù)位電路。關(guān)于上電復(fù)位和掉電復(fù)位的細節(jié)請參考數(shù)據(jù)手冊的電氣特性部分。

上電復(fù)位和掉電復(fù)位的波形圖

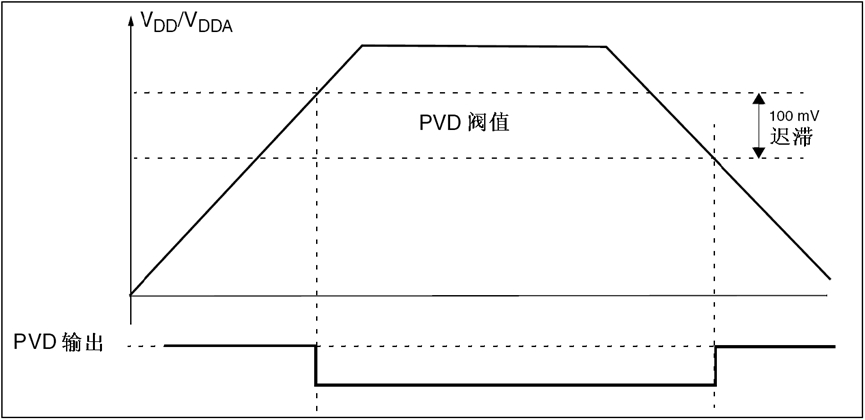

2.2 可編程電壓監(jiān)測器(PVD)

用戶可以利用 PVD對 VDD電壓與電源控制寄存器(PWR_CR)中的 PLS[2:0]位進行比較來監(jiān)控電源,這幾位選擇監(jiān)控電壓的閥值。通過設(shè)置 PVDE 位來使能 PVD。

電源控制/狀態(tài)寄存器(PWR_CSR)中的 PVDO 標志用來表明 VDD 是高于還是低于 PVD 的電壓閥值。該事件在內(nèi)部連接到外部中斷的第 16 線,如果該中斷在外部中斷寄存器中是使能的,該事件就會產(chǎn)生中斷。當 VDD 下降到 PVD 閥值以下和(或)當 VDD 上升到 PVD 閥值之上時,根據(jù)外部中斷第16 線的上升/下降邊沿觸發(fā)設(shè)置,就會產(chǎn)生 PVD 中斷。例如,這一特性可用于用于執(zhí)行緊急關(guān)閉任務(wù)。

PVD的門限

3 低功耗模式

在系統(tǒng)或電源復(fù)位以后,微控制器處于運行狀態(tài)。當 CPU 不需繼續(xù)運行時,可以利用多種低功耗模式來節(jié)省功耗,例如等待某個外部事件時。用戶需要根據(jù)最低電源消耗、最快速啟動時間和可用的喚醒源等條件,選定一個最佳的低功耗模式。

三種低功耗模式:

?睡眠模式(Cortex?-M3 內(nèi)核停止,所有外設(shè)包括 Cortex-M3 核心的外設(shè),如 NVIC、系統(tǒng)時鐘(SysTick)等仍在運行)

?停止模式(所有的時鐘都已停止)

?待機模式(1.8V 電源關(guān)閉)

此外,在運行模式下,可以通過以下方式中的一種降低功耗:

?降低系統(tǒng)時鐘

?關(guān)閉 APB 和 AHB 總線上未被使用的外設(shè)時鐘。

低功耗模式一覽

| 模式 | 進入 | 喚醒 | 對 1.8V 區(qū)域時鐘的影響 | 對 VDD區(qū)域時鐘的影響 | 電壓調(diào)節(jié)器 |

| 睡眠 (SLEEP - NOW 或 SLEEP - ON - EXIT) |

WFI WFE |

任一中斷 喚醒事件 |

CPU 時鐘關(guān),對其他時鐘和 ADC 時鐘無影響 | 無 | 開 |

| 停機 | PDDS 和 LPDS 位 + SLEEPDEEP 位 + WFI 或 WFE | 任一外部中斷 (在外部中斷寄存器中設(shè)置) | 關(guān)閉所有 1.8V 區(qū)域的時鐘 | HSI 和 HSE 的振蕩器關(guān)閉 | 開啟或處于低功耗模式 (依據(jù)電源控制寄存器 (PWR_CR) 的設(shè)定) |

| 待機 | PDDS 位 + SLEEPDEEP 位 + WFI 或 WFE | WKUP 引腳上的上升沿、RTC 鬧鐘事件、NRST 引腳上的外部復(fù)位、IWDG 復(fù)位 | - | - | 關(guān) |

3.1 降低系統(tǒng)時鐘

在運行模式下,通過對預(yù)分頻寄存器進行編程,可以降低任意一個系統(tǒng)時鐘(SYSCLK、HCLK、PCLK1、PCLK2)的速度。進入睡眠模式前,也可以利用預(yù)分頻器來降低外設(shè)的時鐘。

3.2 外部時鐘的控制

在運行模式下,任何時候都可以通過停止為外設(shè)和內(nèi)存提供時鐘(HCLK 和 PCLKx)來減少功耗。為了在睡眠模式下更多地減少功耗,可在執(zhí)行 WFI 或 WFE 指令前關(guān)閉所有外設(shè)的時鐘。

通過設(shè)置 AHB 外設(shè)時鐘使能寄存器(RCC_AHBENR)、APB2 外設(shè)時鐘使能寄存器(RCC_APB2ENR)和APB1 外設(shè)時鐘使能寄存器(RCC_APB1ENR)來開關(guān)各個外設(shè)模塊的時鐘。

3.3 睡眠模式

進入睡眠模式通過執(zhí)行 WFI 或 WFE 指令進入睡眠狀態(tài)。根據(jù) Cortex?-M3 系統(tǒng)控制寄存器中的 SLEEPONEXIT 位的值,有兩種選項可用于選擇睡眠模式進入機制:

?SLEEP-NOW:如果 SLEEPONEXIT 位被清除,當 WRI 或 WFE 被執(zhí)行時,微控制器立即進入睡眠模式。

?SLEEP-ON-EXIT:如果 SLEEPONEXIT 位被置位,系統(tǒng)從最低優(yōu)先級的中斷處理程序中退出時,微控制器就立即進入睡眠模式。

在睡眠模式下,所有的 I/O 引腳都保持它們在運行模式時的狀態(tài)。

退出睡眠模式如果執(zhí)行 WFI 指令進入睡眠模式,任意一個被嵌套向量中斷控制器響應(yīng)的外設(shè)中斷都能將系統(tǒng)從睡眠模式喚醒。如果執(zhí)行 WFE 指令進入睡眠模式,則一旦發(fā)生喚醒事件時,微處理器都將從睡眠模式退出。喚醒事件可以通過下述方式產(chǎn)生:

?在外設(shè)控制寄存器中使能一個中斷,而不是在 NVIC(嵌套向量中斷控制器)中使能,并且在Cortex-M3 系統(tǒng)控制寄存器中使能 SEVONPEND 位。當 MCU 從 WFE 中喚醒后,外設(shè)的中斷掛起位和外設(shè)的 NVIC 中斷通道掛起位(在 NVIC 中斷清除掛起寄存器中)必須被清除。

配置一個外部或內(nèi)部的 EXIT 線為事件模式。當 MCU 從 WFE 中喚醒后,因為與事件線對應(yīng)的掛起位未被設(shè)置,不必清除外設(shè)的中斷掛起位或外設(shè)的 NVIC 中斷通道掛起位。該模式喚醒所需的時間最短,因為沒有時間損失在中斷的進入或退出上。

SLEEP-NOW 模式

| SLEEP-NOW 模式 | 說明 |

| 進入 |

在以下條件下執(zhí)行 WFI (等待中斷) 或 WFE (等待事件) 指令: - SLEEPDEEP=0 和 - SLEEPONEXIT=0 參考 Cortex-M3 系統(tǒng)控制寄存器。 |

| 退出 |

如果執(zhí)行 WFI 進入睡眠模式: 中斷:參考中斷向量表 (表 51) 如果執(zhí)行 WFE 進入睡眠模式: 喚醒事件:參考喚醒事件管理 (第 8.2.3 節(jié)) |

SLEEP-ON-EXIT 模式

| SLEEP-ON_EXIT 模式 | 說明 |

| 進入 |

在以下條件下執(zhí)行 WFI 指令: - SLEEPDEEP=0 和 - SLEEPONEXIT=1 參考 Cortex?-M3 系統(tǒng)控制寄存器 |

| 退出 | 中斷:參考中斷向量表 (表 51) |

| 喚醒延時 | 無 |

3.4 停止模式

停止模式是在 Cortex?-M3 的深睡眠模式基礎(chǔ)上結(jié)合了外設(shè)的時鐘控制機制,在停止模式下電壓調(diào)節(jié)器可運行在正常或低功耗模式。此時在 1.8V 供電區(qū)域的的所有時鐘都被停止,PLL、HSI 和HSERC 振蕩器的功能被禁止,SRAM 和寄存器內(nèi)容被保留下來。

在停止模式下,所有的 I/O 引腳都保持它們在運行模式時的狀態(tài)。

進入停止模式

在停止模式下,通過設(shè)置電源控制寄存器(PWR_CR)的 LPDS 位使內(nèi)部調(diào)節(jié)器進入低功耗模式,能夠降低更多的功耗。如果正在進行閃存編程,直到對內(nèi)存訪問完成,系統(tǒng)才進入停止模式。如果正在進行對 APB 的訪問,直到對 APB 訪問完成,系統(tǒng)才進入停止模式。可以通過對獨立的控制位進行編程,可選擇以下功能:

?獨立看門狗(IWDG):可通過寫入看門狗的鍵寄存器或硬件選擇來啟動 IWDG。一旦啟動了獨立看門狗,除了系統(tǒng)復(fù)位,它不能再被停止。

?實時時鐘(RTC):通過備份域控制寄存器(RCC_BDCR)的 RTCEN 位來設(shè)置。

?內(nèi)部 RC 振蕩器(LSIRC):通過控制/狀態(tài)寄存器(RCC_CSR)的 LSION 位來設(shè)置。

?外部 32.768kHz 振蕩器(LSE):通過備份域控制寄存器(RCC_BDCR)的 LSEON 位設(shè)置。

在停止模式下,如果在進入該模式前 ADC 和 DAC 沒有被關(guān)閉,那么這些外設(shè)仍然消耗電流。通過設(shè)置寄存器 ADC_CR2 的 ADON 位和寄存器 DAC_CR 的 ENx 位為 0 可關(guān)閉這 2 個外設(shè)。

退出停止模式

關(guān)于如何退出停止模式,詳見下表。

當一個中斷或喚醒事件導(dǎo)致退出停止模式時,HSIRC 振蕩器被選為系統(tǒng)時鐘。

當電壓調(diào)節(jié)器處于低功耗模式下,當系統(tǒng)從停止模式退出時,將會有一段額外的啟動延時。如果在停止模式期間保持內(nèi)部調(diào)節(jié)器開啟,則退出啟動時間會縮短,但相應(yīng)的功耗會增加。

停止模式

| 停止模式 | 說明 |

| 進入 |

在以下條件下執(zhí)行 WFI (等待中斷) 或 WFE (等待事件) 指令: - 設(shè)置 Cortex-M3 系統(tǒng)控制寄存器中的 SLEEPDEEP 位 - 不清除電源控制寄存器 (PWR_CR) 中的 PDDS 位 - 通過設(shè)置 PWR_CR 中 LPDS 位選擇電壓調(diào)節(jié)器的模式 注:為了進入停止模式,所有的外部中斷的請求位 (掛起寄存器 (EXTI_PR)) 和 RTC 的鬧鐘標志都必須被清除,否則停止模式的進入流程將會被跳過,程序繼續(xù)運行。 |

| 退出 |

如果執(zhí)行 WFI 進入停止模式: 設(shè)置任一外部中斷線為中斷模式 (在 NVIC 中必須使能相應(yīng)的外部中斷向量)。參見中斷向量表 (表 51)。 如果執(zhí)行 WFE 進入停止模式: 設(shè)置任一外部中斷線為事件模式。參見喚醒事件管理 (第 8.2.3 節(jié))。 |

| 喚醒延時 | HSIRC 喚醒時間 + 電壓調(diào)節(jié)器從低功耗喚醒的時間。 |

3.5 待機模式

待機模式可實現(xiàn)系統(tǒng)的最低功耗。該模式是在 Cortex-M3 深睡眠模式時關(guān)閉電壓調(diào)節(jié)器。整個1.8V 供電區(qū)域被斷電。PLL、HSI 和 HSE 振蕩器也被斷電。SRAM 和寄存器內(nèi)容丟失。只有備份的寄存器和待機電路維持供電。

進入待機模式

可以通過設(shè)置獨立的控制位,選擇以下待機模式的功能:

?獨立看門狗(IWDG):可通過寫入看門狗的鍵寄存器或硬件選擇來啟動 IWDG。一旦啟動了獨立看門狗,除了系統(tǒng)復(fù)位,它不能再被停止。

?實時時鐘(RTC):通過備用區(qū)域控制寄存器(RCC_BDCR)的 RTCEN 位來設(shè)置。

?內(nèi)部 RC 振蕩器(LSIRC):通過控制/狀態(tài)寄存器(RCC_CSR)的 LSION 位來設(shè)置。

?外部 32.768kHz 振蕩器(LSE):通過備用區(qū)域控制寄存器(RCC_BDCR)的 LSEON 位設(shè)置。

退出待機模式

當一個外部復(fù)位(NRST 引腳)、IWDG 復(fù)位、WKUP 引腳上的上升沿或 RTC 鬧鐘事件的上升沿發(fā)生時,微控制器從待機模式退出。從待機喚醒后,除了電源控制/狀態(tài)寄存器(PWR_CSR),所有寄存器被復(fù)位。從待機模式喚醒后的代碼執(zhí)行等同于復(fù)位后的執(zhí)行(采樣啟動模式引腳、讀取復(fù)位向量等)。電源控制/狀態(tài)寄存器(PWR_CSR)(見第 4.4.2 節(jié))將會指示內(nèi)核由待機狀態(tài)退出。

關(guān)于如何退出待機模式,詳見下表:

待機模式

| 待機模式 | 說明 |

| 進入 |

在以下條件下執(zhí)行 WFI (等待中斷) 或 WFE (等待事件) 指令: - 設(shè)置 Cortex?-M3 系統(tǒng)控制寄存器中的 SLEEPDEEP 位 - 設(shè)置電源控制寄存器 (PWR_CR) 中的 PDDS 位 - 清除電源控制 / 狀態(tài)寄存器 (PWR_CSR) 中的 WUF 位 |

| 退出 | WKUP 引腳的上升沿、RTC 鬧鐘事件的上升沿、NRST 引腳上外部復(fù)位、IWDG 復(fù)位。 |

| 喚醒延時 | 復(fù)位階段時電壓調(diào)節(jié)器的啟動。 |

待機模式下的輸入/輸出端口狀態(tài)

在待機模式下,所有的 I/O 引腳處于高阻態(tài),除了以下的引腳:

?復(fù)位引腳(始終有效)

?當被設(shè)置為防侵入或校準輸出時的 TAMPER 引腳

?被使能的喚醒引腳

調(diào)試模式

默認情況下,如果在進行調(diào)試微處理器時,使微處理器進入停止或待機模式,將失去調(diào)試連接。這是因為 Cortex?-M3 的內(nèi)核失去了時鐘。然而,通過設(shè)置 DBGMCU_CR 寄存器中的某些配置位,可以在使用低功耗模式下調(diào)試軟件。

3.6 低功耗模式下的自動喚醒(AWU)

RTC可以在不需要依賴外部中斷的情況下喚醒低功耗模式下的微控制器(自動喚醒模式)。RTC提供一個可編程的時間基數(shù),用于周期性從停止或待機模式下喚醒。通過對備份區(qū)域控制寄存器(RCC_BDCR)的RTCSEL[1:0]位的編程,三個 RTC 時鐘源中的二個時鐘源可以選作實現(xiàn)此功能。

?低功耗 32.768kHz 外部晶振(LSE)該時鐘源提供了一個低功耗且精確的時間基準。(在典型情形下消耗小于 1μA)

?低功耗內(nèi)部 RC 振蕩器(LSIRC)

使用該時鐘源,節(jié)省了一個 32.768kHz 晶振的成本。但是 RC 振蕩器將少許增加電源消耗。為了用 RTC 鬧鐘事件將系統(tǒng)從停止模式下喚醒,必須進行如下操作:

?配置外部中斷線 17 為上升沿觸發(fā)。

?配置 RTC 使其可產(chǎn)生 RTC 鬧鐘事件。

如果要從待機模式中喚醒,不必配置外部中斷線 17。

4 例程設(shè)計

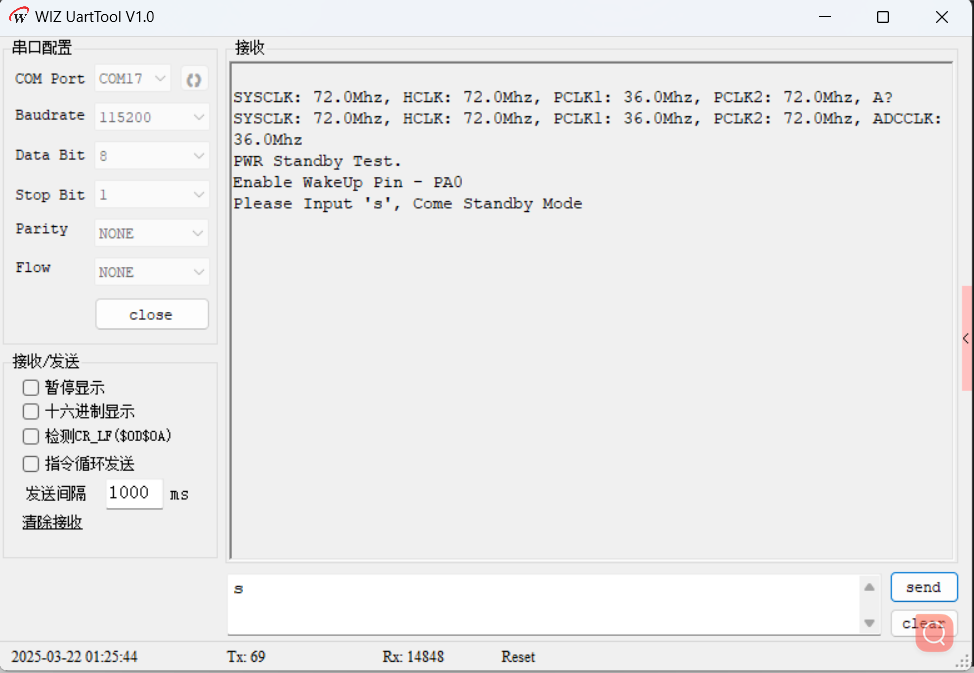

4.1 PWR_Standby

1. 初始化階段

(1)使能電源和備份域時鐘

RCC_APB1PeriphClockCmd(RCC_APB1Periph_PWR | RCC_APB1Periph_BKP, ENABLE);

開啟電源控制(PWR)和備份域(BKP)的時鐘,為后續(xù)的電源管理操作做準備。

(2)延時函數(shù)和串口初始化

delay_init(); UART_Configuration(115200);

?delay_init():初始化延時函數(shù),方便后續(xù)使用延時操作。

?UART_Configuration(115200):配置串口 1,波特率為 115200,用于后續(xù)的信息輸出和命令接收。

(3)獲取并打印時鐘信息

RCC_GetClocksFreq(&clocks);

printf("n");

printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn",

(float)clocks.SYSCLK_Frequency / 1000000, (float)clocks.HCLK_Frequency / 1000000,

(float)clocks.PCLK1_Frequency / 1000000, (float)clocks.PCLK2_Frequency / 1000000, (float)clocks.ADCCLK_Frequency / 1000000);

獲取系統(tǒng)各時鐘頻率,并通過串口打印出來,方便調(diào)試和查看系統(tǒng)時鐘配置情況。

(4)打印提示信息并使能喚醒引腳

printf("PWR Standby Test.n");

printf("Enable WakeUp Pin - PA0n");

printf("Please Input 's', Come Standby Moden");

PWR_WakeUpPinCmd(ENABLE);

?打印測試信息和提示用戶輸入's' 以進入待機模式。

?使能喚醒引腳 PA0,用于后續(xù)從待機模式喚醒系統(tǒng)。

2. 等待用戶輸入

while (GetCmd() != 's');

?通過GetCmd()函數(shù)不斷檢查串口接收的數(shù)據(jù),當接收到字符's' 時,跳出循環(huán),準備進入待機模式。

3. GPIO 配置

GPIO_Configuration();

?對所有 GPIO 端口(GPIOA - GPIOG)進行配置,將所有引腳設(shè)置為模擬輸入模式,以降低功耗。

4. 進入待機模式

PWR_EnterSTANDBYMode();

?調(diào)用該函數(shù)使系統(tǒng)進入待機模式,此時系統(tǒng)大部分功能停止工作,功耗極低。綜上所述,該程序的主要流程是初始化系統(tǒng),提示用戶輸入's',接收到指定字符后配GPIO,然后使系統(tǒng)進入待機模式,等待喚醒信號。

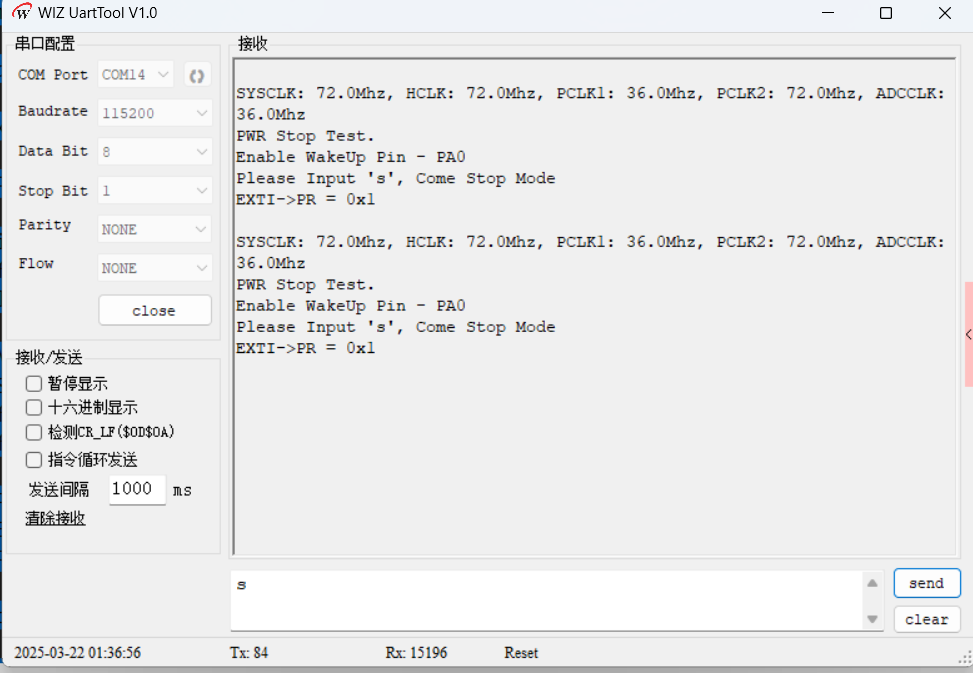

4.2 PWR_Stop

該程序是一個基于 W55MH32 的低功耗停止模式(STOP Mode)測試程序,主要用于驗證系統(tǒng)進入停止模式以及通過外部中斷喚醒的功能。以下是程序的主要工作流程總結(jié):

1. 初始化階段

(1)使能電源和備份域時鐘

RCC_APB1PeriphClockCmd(RCC_APB1Periph_PWR | RCC_APB1Periph_BKP, ENABLE);

開啟電源控制(PWR)和備份域(BKP)的時鐘,為后續(xù)的電源管理操作做準備。

(2)延時函數(shù)和串口初始化

delay_init(); UART_Configuration(115200);

?delay_init():初始化延時函數(shù)。

?UART_Configuration(115200):配置串口 1,波特率為 115200,用于調(diào)試信息輸出和命令接收。

(3)獲取并打印時鐘信息

RCC_GetClocksFreq(&clocks);

printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn", ...);

獲取并打印系統(tǒng)各總線時鐘頻率,便于調(diào)試。

(4)打印提示信息并配置喚醒引腳

printf("PWR Stop Test.n");

printf("Enable WakeUp Pin - PA0n");

printf("Please Input 's', Come Stop Moden");

WAKEUP_Configuration();

?提示用戶輸入字符's' 觸發(fā)進入停止模式。

?調(diào)用WAKEUP_Configuration() 配置喚醒引腳 PA0 為外部中斷觸發(fā)(上升沿)。

2. 等待用戶輸入

while (GetCmd() != 's');

通過GetCmd() 函數(shù)持續(xù)檢測串口輸入,直到接收到字符's'。

3. GPIO 配置

GPIO_Configuration();

?將所有 GPIO 引腳(除 PA0 外)設(shè)置為模擬輸入模式(GPIO_Mode_AIN),以降低功耗。

?PA0 保持上拉輸入,用于喚醒中斷。

4. 進入停止模式

PWR_EnterSTOPMode(PWR_Regulator_LowPower, PWR_STOPEntry_WFI);

?選擇低功耗調(diào)節(jié)器(PWR_Regulator_LowPower)以進一步降低功耗。

?通過 **WFI(Wait For Interrupt)** 指令進入停止模式。

5. 喚醒后處理

(1)系統(tǒng)復(fù)位與重新初始化

SystemInit(); // 復(fù)位系統(tǒng)時鐘到默認配置

UART_Configuration(115200); // 重新初始化串口

printf("WakeUp Successn");

?喚醒后,系統(tǒng)從復(fù)位向量啟動,需重新初始化串口才能繼續(xù)輸出。

(2)無限循環(huán)

while (1);

程序保持運行狀態(tài),等待其他操作。

6. 喚醒中斷處理(EXTI0_IRQHandler)

?當 PA0 檢測到上升沿時觸發(fā)中斷。

?清除中斷標志位并打印調(diào)試信息(示例中僅打印EXTI->PR寄存器值)。

5 下載驗證

5.1 PWR_Standby

5.2 PWR_Stop

WIZnet 是一家無晶圓廠半導(dǎo)體公司,成立于 1998 年。產(chǎn)品包括互聯(lián)網(wǎng)處理器 iMCU?,它采用 TOE(TCP/IP 卸載引擎)技術(shù),基于獨特的專利全硬連線 TCP/IP。iMCU? 面向各種應(yīng)用中的嵌入式互聯(lián)網(wǎng)設(shè)備。

WIZnet 在全球擁有 70 多家分銷商,在香港、韓國、美國設(shè)有辦事處,提供技術(shù)支持和產(chǎn)品營銷。

香港辦事處管理的區(qū)域包括:澳大利亞、印度、土耳其、亞洲(韓國和日本除外)。

審核編輯 黃宇

-

電源控制

+關(guān)注

關(guān)注

2文章

150瀏覽量

27249 -

PWR

+關(guān)注

關(guān)注

0文章

29瀏覽量

10431

發(fā)布評論請先 登錄

第十章 W55MH32中斷應(yīng)用概覽

第十九章 ADC——電壓采集

即刻啟程,踏上W55MH32高性能以太網(wǎng)單片機學習之路!

WIZnet W55MH32以太網(wǎng)單片機開發(fā)教程 第十一章 通用定時器(上篇)

第九章 W55MH32 HTTP Server示例

第十章 W55MH32 SNTP示例

第十一章 W55MH32 SMTP示例

第十二章 W55MH32 NetBIOS示例

第十四章 W55MH32 TFTP示例

第十五章 W55MH32 SNMP示例

第十六章 W55MH32 PING示例

第十八章 W55MH32 FTP_Server示例

第十九章 W55MH32 FTP_Client示例

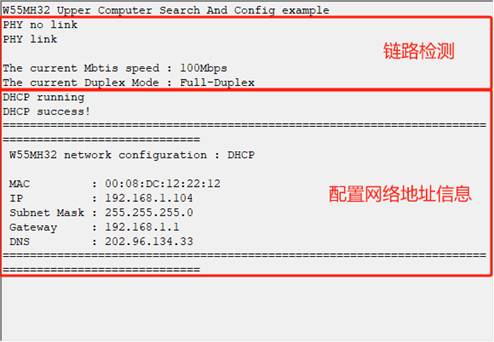

第二十六章 W55MH32?上位機搜索和配置示例

第二十九章 W55MH32 Modbus_TCP_Server示例

第十九章 W55MH32的電源控制(PWR)功能

第十九章 W55MH32的電源控制(PWR)功能

評論