即使是5nm制程,已經(jīng)令人難以確定能否從中找到任何優(yōu)勢了,3nm很可能成為半導(dǎo)體終極先進(jìn)制程,而2nm似乎太遙遠(yuǎn)…

在邁向5nm、3nm或甚至2nm半導(dǎo)體制程技術(shù)之路,業(yè)界工程師可能有多種選擇,但有些人并不確定他們是否仍能從中找到任何商業(yè)利益,甚至是5nm制程。

為了打造尺寸日益縮小的晶片,所需的復(fù)雜度與成本越來越高,但卻導(dǎo)致收益遞減。日前于新思科技(Synopsys)用戶大會(SNUG)的一場座談會上,高通公司(Qualcomm)的一位工程師指出,行動處理器的資料速率將在3GHz達(dá)到峰值,而功耗和面積增益則從7nm開始縮減。

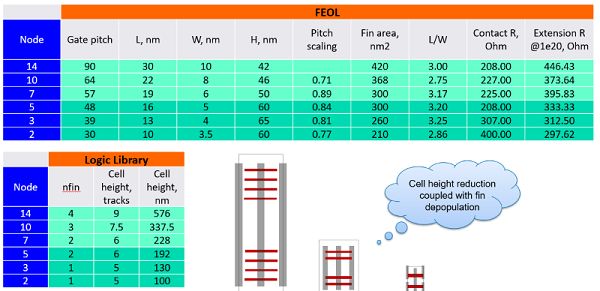

高通設(shè)計(jì)技術(shù)團(tuán)隊(duì)資深工程總監(jiān)Paul Penzes指出,由于金屬導(dǎo)線中存在電阻性,使得10nm時(shí)速度提升的16%到了7nm時(shí)耗盡。此外,從10nm進(jìn)展到7nm,功耗節(jié)省的幅度將從30%縮減到10-25%,面積微縮的幅度也會從37%減少到20-30%。

數(shù)十年來,電子產(chǎn)業(yè)一直循“摩爾定律”(Moore’s law)所設(shè)定的開發(fā)藍(lán)圖——晶片上可容納的電晶體數(shù)量大約每隔兩年增加1倍。其結(jié)果是從個人電腦(PC)到智能手機(jī)等產(chǎn)品的尺寸越來越小、速度越來越快,價(jià)格也越來越便宜。

Penzes說:“目前的晶片面積仍然以很高的兩位數(shù)持續(xù)微縮,但在光罩背后所隱藏的成本增加,意味著實(shí)際的成本優(yōu)勢以及其他進(jìn)展正開始放緩......目前尚不清楚到了5nm時(shí)還能保有什么。”這表示5nm節(jié)點(diǎn)很可能只是7nm的延伸。

來自Synopsys和三星(Samsung)的技術(shù)專家表示,當(dāng)今的FinFET電晶體版本應(yīng)該還能用于5nm節(jié)點(diǎn)。而當(dāng)進(jìn)展到低于3.5nm的寬度時(shí),F(xiàn)inFET將會達(dá)到極限。

新思科技研究人員兼電晶體專家Victor Moroz說,設(shè)計(jì)人員可能必須過渡到采用大約三層的橫向納米線堆疊,或稱為“納米矽板”(nano-slabs)。三星則宣布計(jì)劃使用閘極全環(huán)(GAA)電晶體以實(shí)現(xiàn)4nm制程,目標(biāo)是在2020年投入生產(chǎn)。

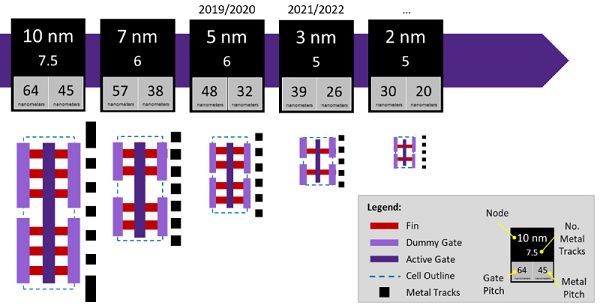

新思科技的Munoz表示,到了未來的技術(shù)節(jié)點(diǎn),間距微縮將減緩至每世代約0.8倍左右。這將迫使設(shè)計(jì)人員將7nm時(shí)雙鰭、6軌的228nm單元高度結(jié)構(gòu),在3nm和2nm時(shí)縮減到單鰭、5軌的130-100nm結(jié)構(gòu)。

他總結(jié)說,使用這種技術(shù),“矽晶似乎就能讓我們安全地微縮至2nm,而在那之后,我們可能就會開始使用石墨烯。”

然而,在最后的問答環(huán)節(jié)中,一位與會者對于這種單鰭5軌單元的結(jié)構(gòu)表示震驚。

新思科技描繪邁向2nm的通用開發(fā)藍(lán)圖(來源:Synopsys)

新思科技部門研發(fā)總監(jiān)Henry Sheng表示,更精細(xì)制程的復(fù)雜度迫使晶片設(shè)計(jì)師面對日益嚴(yán)苛的設(shè)計(jì)規(guī)則。例如,F(xiàn)inFET對于工程師必須追蹤的波形傳播、電遷移和元件變異帶來了新的效應(yīng)。但他也樂觀地認(rèn)為,“這些效應(yīng)最終都將得到解決”。

在這場座談會上的專家們認(rèn)為,成功最終將取決于代工廠、EDA和設(shè)計(jì)工程師之間越來越密切的合作。在邁向目標(biāo)進(jìn)行時(shí),高通公司認(rèn)為,為了獲得最佳產(chǎn)能,必須在生產(chǎn)開始之前對其先進(jìn)設(shè)計(jì)進(jìn)行調(diào)整,以及更清楚地定義制程節(jié)點(diǎn)。

“由于行動處理器的競爭非常激烈,代工廠導(dǎo)入的節(jié)點(diǎn)越來越不成熟,”Penzes說:“如果超出了利潤,那么平均單位成本就會上漲,而變得缺乏競爭力。”

“現(xiàn)在,在了解單元的電氣特性之前,必須先掌握其環(huán)境,”他補(bǔ)充說。“即使是10%的變異也可能讓一個新節(jié)點(diǎn)的所有優(yōu)勢盡失,因此,以前存在的所有雜訊都必須克服。”

Penzes指出最近的一些開發(fā)工作為此帶來了希望。晶圓代工廠正在尋找以不同速率微縮各種單元的方法,而EDA供應(yīng)商也承諾改善布線,其方式可能是采用極紫外光微影(EUV)技術(shù)。

Moroz表示,工程師們也開始探索其他許多技術(shù),以降低金屬導(dǎo)線上的電阻率,從而為加速取得優(yōu)勢開啟大門。其方式包括新的結(jié)構(gòu),例如跨越多個金屬層的梯度和超導(dǎo)孔(super-vias),以及使用鈷(Co)和釕(Ru)等新材料。

為了說明未來即將面對的挑戰(zhàn),Moroz詳細(xì)闡述開發(fā)藍(lán)圖。

成功的恒久不變因素仍然是工程師有信心找到解決棘手問題的方法。

例如,三星承諾為搭配EUV的7nm制程制訂規(guī)范,并計(jì)劃在今年制造晶圓,不過它仍然在等待步進(jìn)器。Samsung Foundry設(shè)計(jì)支援副總裁Jongwook Kye在座談會上表示,“只要ASML能夠提供這些工具,我們就會開始投入大量制造。”。

同時(shí),三星也正在試圖為2020年的4nm生產(chǎn)定義新的電晶體。Kyle說:“這是我們在未來幾年內(nèi)必須克服的挑戰(zhàn);只要能與工具供應(yīng)商和其他公司密切合作,我相信我們最終能實(shí)現(xiàn)目標(biāo)。”

-

高通

+關(guān)注

關(guān)注

78文章

7731瀏覽量

199806 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30737瀏覽量

264135 -

晶片

+關(guān)注

關(guān)注

1文章

413瀏覽量

32910

原文標(biāo)題:投入2納米制程值得嗎?

文章出處:【微信號:Imgtec,微信公眾號:Imagination Tech】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

2nm“諸神之戰(zhàn)”打響!性能飆升+功耗驟降,臺積電攜聯(lián)發(fā)科領(lǐng)跑

臺積電擬投資170億,在日本建設(shè)3nm芯片工廠

三星發(fā)布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

國產(chǎn)芯片真的 “穩(wěn)” 了?這家企業(yè)的 14nm 制程,已經(jīng)悄悄滲透到這些行業(yè)…

三星公布首批2納米芯片性能數(shù)據(jù)

臺積電2納米制程試產(chǎn)成功,AI、5G、汽車芯片

看點(diǎn):臺積電2納米N2制程吸引超15家客戶 英偉達(dá)擬向OpenAI投資1000億美元

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+半導(dǎo)體芯片產(chǎn)業(yè)的前沿技術(shù)

今日看點(diǎn)丨三星美國廠2nm產(chǎn)線運(yùn)作;《人工智能生成合成內(nèi)容標(biāo)識辦法》正式生效

三星代工大變革:2nm全力沖刺,1.4nm量產(chǎn)延遲至2029年

臺積電2nm良率超 90%!蘋果等巨頭搶單

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

邁向5nm、3nm或甚至2nm半導(dǎo)體制程技術(shù)之路

邁向5nm、3nm或甚至2nm半導(dǎo)體制程技術(shù)之路

評論