來源:信號完整性之旅,作者:方亞德

1. 高速信號鏈路損耗分析

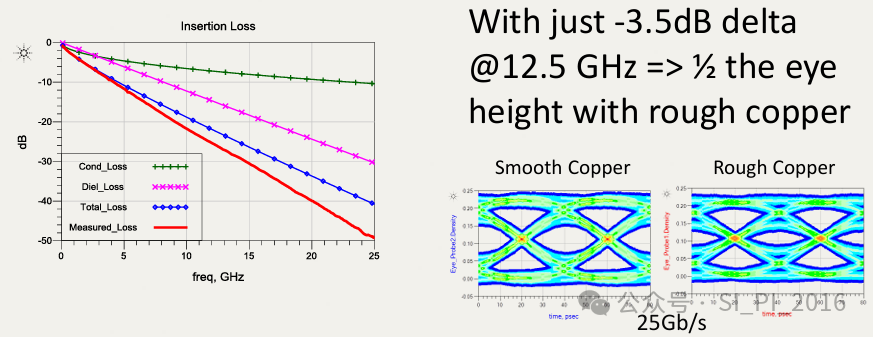

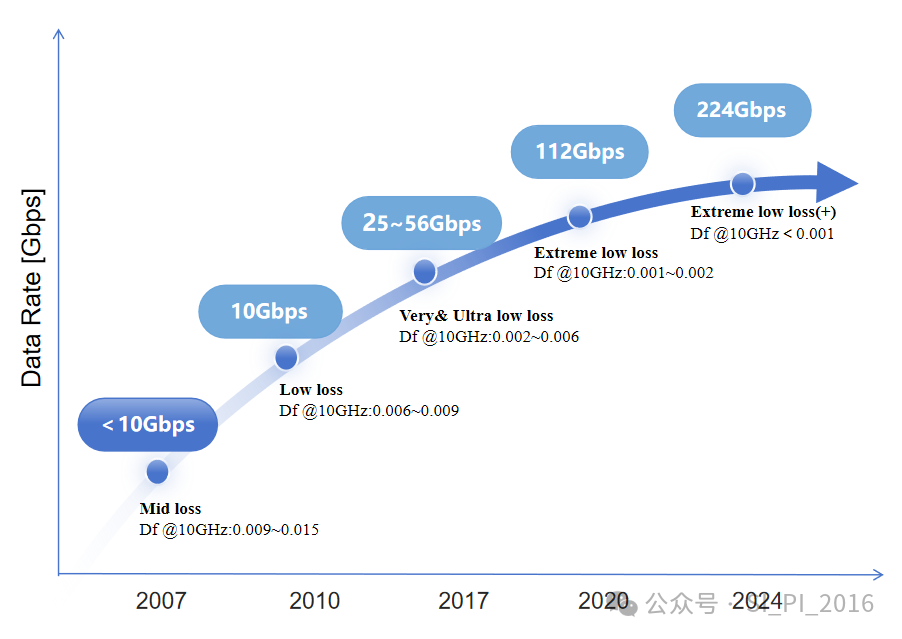

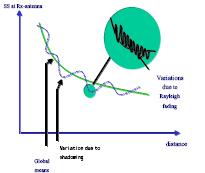

隨著集成電路及其相關應用的發展,信號速率越來越高,大概每3~4年高速信號的速率就會翻一番,隨著信號速率的上升,損耗已經成為影響信號質量的最主要的因素之一。

整個高速鏈路的總體損耗=導體損耗+介質損耗+輻射損耗。

從SI的角度一般不太關注輻射損耗,因為只要系統的阻抗設計不是特別離譜,輻射能量通常會被控制在非常小的范圍,對整體性能的影響可以忽略不計。

介質損耗指信號通過PCB 傳輸線時,介質材料造成的能量損耗,一般用損耗正切角(Loss Tangent)或者Df(Dissipation Factor)來表示。

目前高速信號像serdes已經達到了112G/224G速率節點,PCB材料所帶來的介質損耗的提升空間越來越小,同時更好的PCB材料,也就意味著更高昂的成本。

因此很多工程師的關注點聚焦到了對導體損耗進行優化。

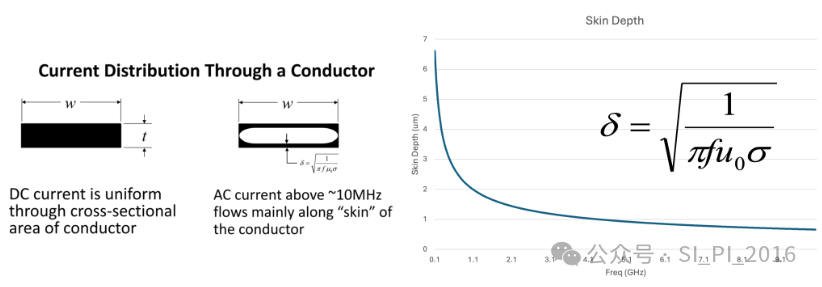

導體損耗主要由金屬的電阻效應和散射損耗造成。電阻效應主要是指金屬本身的電阻,低頻時電流較為平均分布在銅箔內部,損耗較小,而高頻時電流會分布在銅箔表面(電流流動主要會集中在趨膚深度內,如下圖左),電流截面積下降,導致高頻電阻升高,從而使損耗上升,也就是常常說的趨膚效應。

趨膚效應相關的趨膚深度由頻率來決定,而傳輸線的銅厚,跟PCB工藝相關,在設計之初就已經確定。因此,趨膚效應帶來的損耗目前幾乎沒有很好的辦法來避免,所以如何降低導體損耗,工業界的著眼點基本在表面粗糙度的研究上。

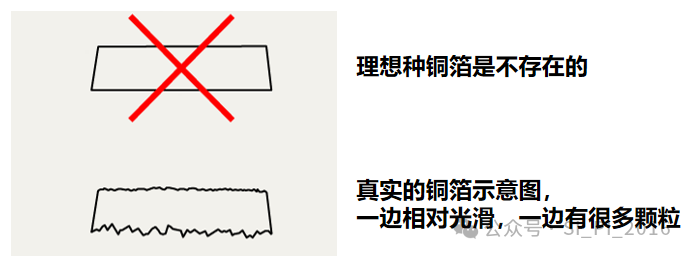

2. 表面粗糙度

PCB銅箔表面不是一個完整的平面,微觀來講可以看到些許的顆粒,這些顆粒會增加銅箔與樹脂的接觸面積,使其粘合度更高,銅皮不容易脫落,但是這些顆粒會使導體損耗在高頻時急劇增加,稱之為銅箔的表面粗糙度。

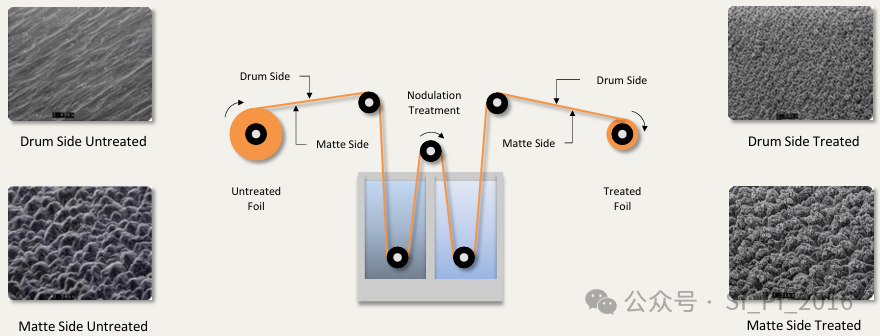

銅箔表面粗糙是源于材料加工過程[3]p.11,其目的是增加銅箔與介質間的黏合力。銅箔會有一面相對平坦(drum side),而另一面比較粗糙(matte side)。[2]p.22

為了讓銅箔能與介電材料(FR4, 玻璃纖維編織版)熱壓黏合,通常在銅箔與FR4的接面較粗糙。 [3]p.10,12

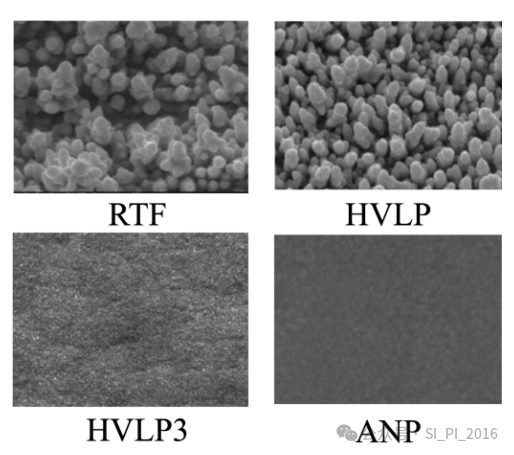

工程上常用Ra與Rz來表示銅皮表面粗糙度。而依不同銅皮的表現又分成不同等級,其中有RTF(Reverse Treated Foil)、VLP(Very Low-Profile)、HVLP(Highly Very Low-Profile)、ANP(Any No-Profile)等等。

目前產業界最高檔的銅箔是HVLP5,幾乎已經是沒有任何的Rz,可以將表面粗糙度降低許多!不過CCL與PCB廠還在努力克服沒有顆粒的銅箔對于材料拉力(Peeling)的影響。

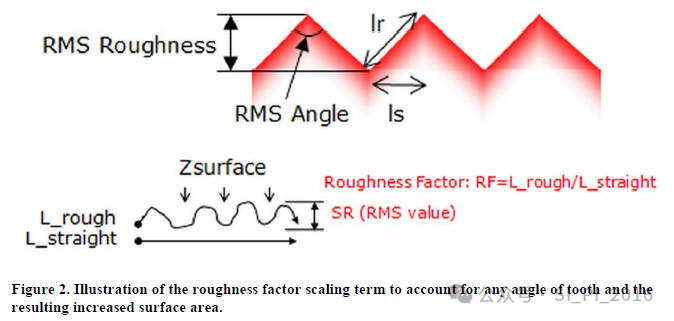

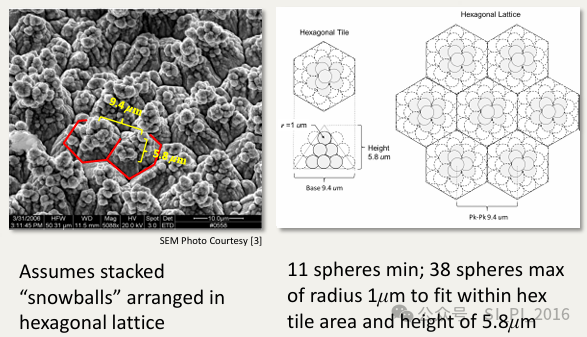

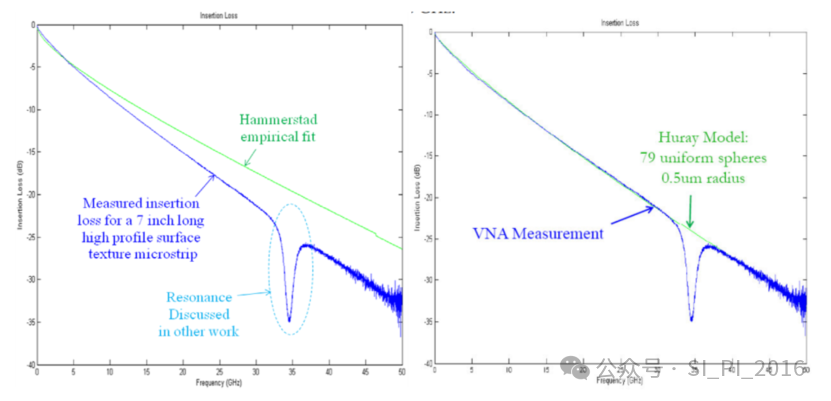

業界一般用2種模型來表征銅箔粗糙度,首先是Hammerstad模型,如下圖所示。這種模型用銅箔的銅牙高度表征粗糙度。

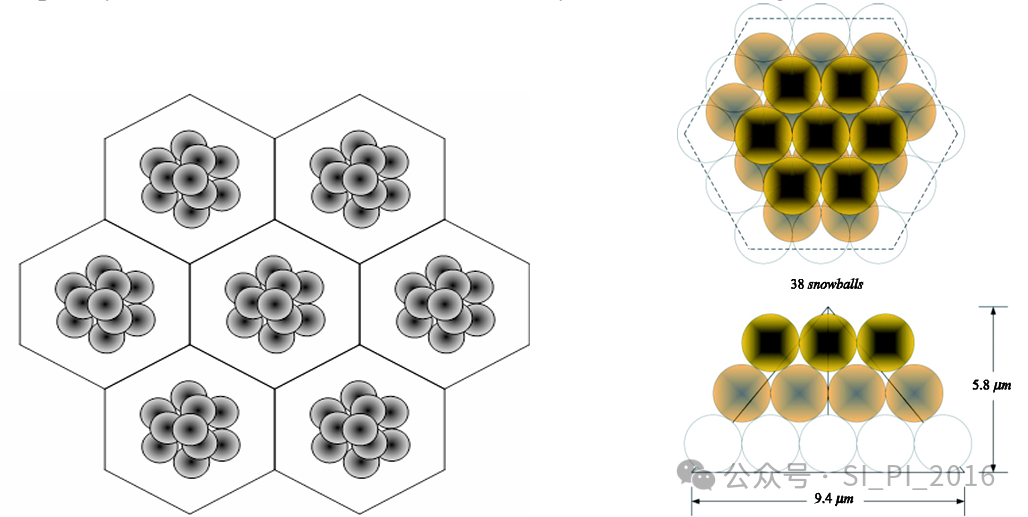

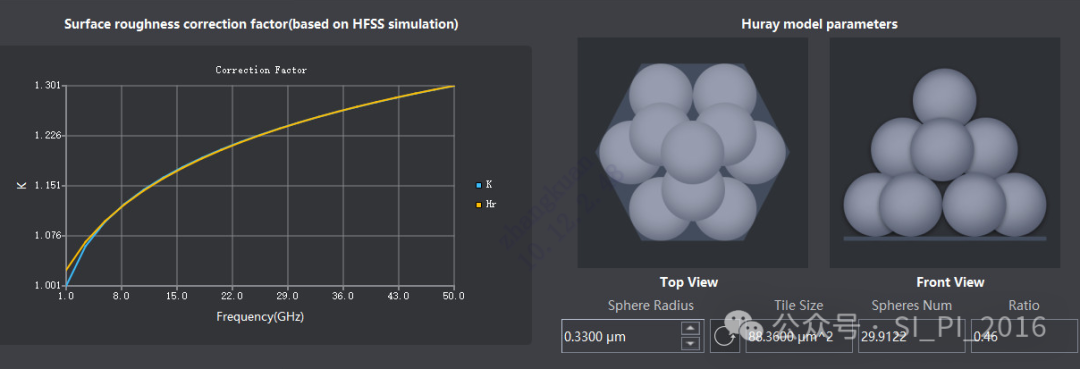

Hammerstad模型雖然只需要鋸齒紋理剖面的RMS參數,但其并不具有物理意義,而是根據擬合插損曲線得到的函數。而Huray模型從銅箔的真實物理結構出發,將銅箔表面的粗糙顆粒用如下圖的均勻球體來等效,根據通過球體后的吸收功率和散射功率計算功率損耗,推導粗糙度公式,與實際情況擬合得更好且具備物理意義。

現在主流EDA商軟主要是使用Huray模型來表征銅箔的粗糙度大小,其參數主要包含雪球半徑和雪球表面積與堆底面積之比(表面比)。

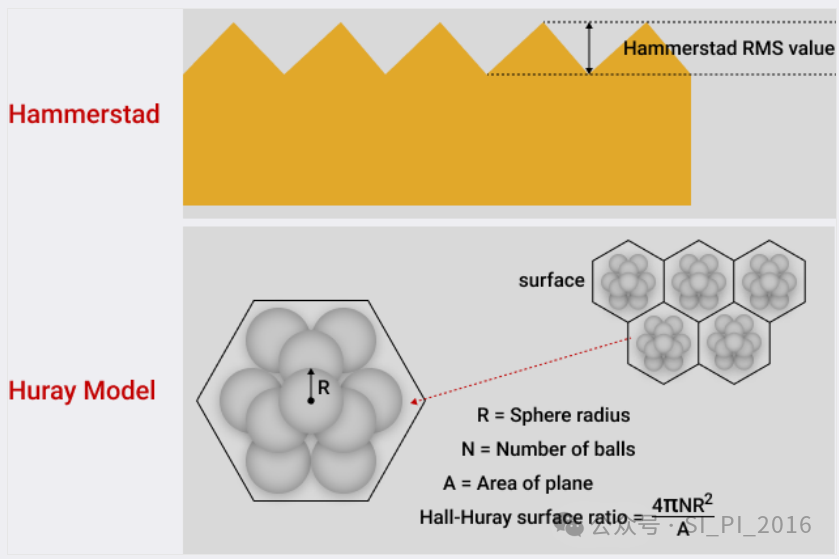

經常有人咨詢那種模型比較好,一般來說,對于低粗糙度,Hammerstad模型與Huray模型的效果差不多[4]p.10,15。但是,Hammerstad模型的函數漸進最大值為2,然而在實際中,表面粗糙度所影響的功率損耗可以超過2倍,因此Hammerstad模型適用于低粗糙度(HRMS<2um)和低頻場景,而Huray模型,適用于一般制程與寬帶場景的應用。下圖是分別用Hammerstad模型和Huray模型擬合一段7inch的表面較粗糙的傳輸線的結果。在低頻處兩者與實測擬合較好,而在高頻處,Hammerstad模型的精度明顯不如Huray模型[3]。

3. 德圖銅箔表面粗糙度解決方案

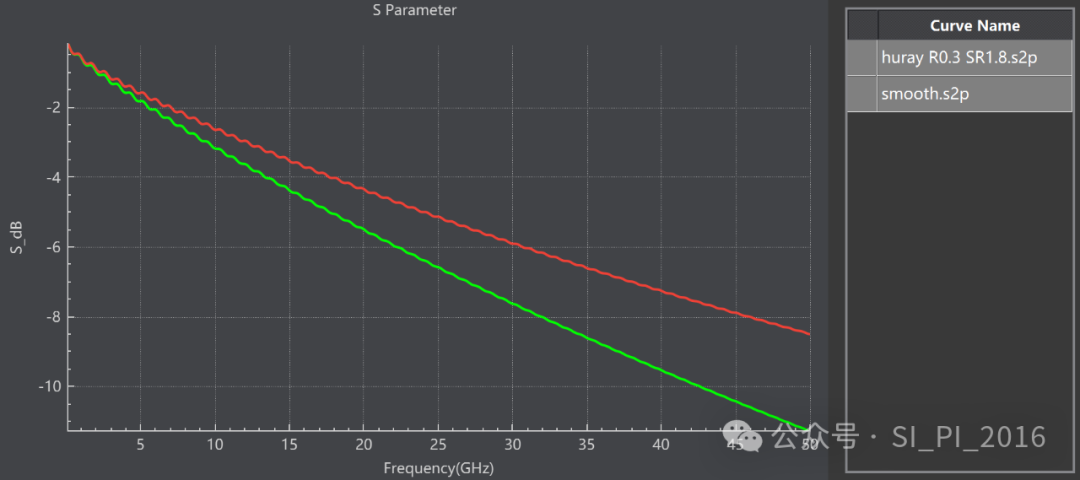

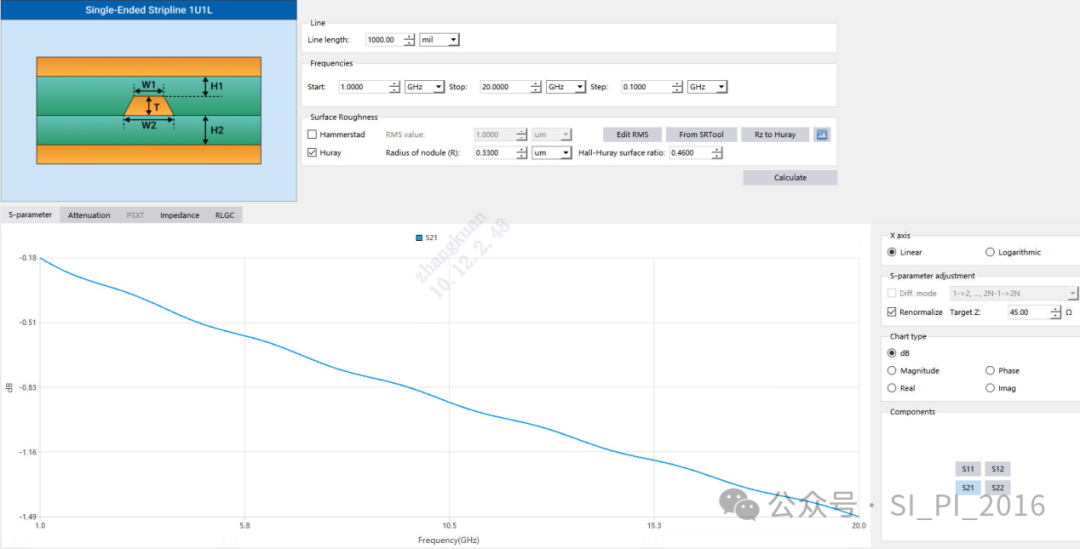

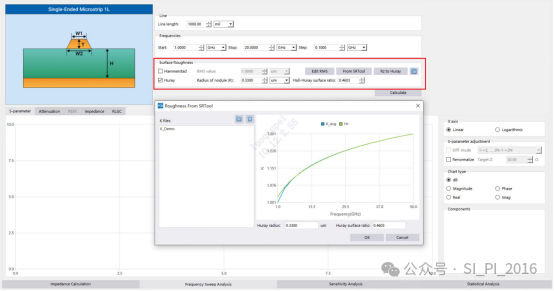

銅箔表面粗糙度對高速信號的損耗有著較大的影響。下圖是使用德圖科技的前仿工具SonicPCB仿真一段4英寸微帶線的插入損耗。綠色曲線為光滑條件的結果,紅色曲線為設置雪球半徑為0.3um,表面比為1.8的Huray模型的結果。分析圖像可知,粗糙度對傳輸線插損影響較大,在50GHz處,兩者的差異接近3dB。隨著信號傳輸速率和頻率的升高,粗糙度帶來損耗影響會愈發明顯,因此業界迫切期待一種簡單有效的粗糙度提取方案。

目前,市面上還沒有可靠的工具能夠進行粗糙度的精確提取,更為常見的是用儀器測量出粗糙表面的Rz與Ra來表征粗糙度。但是在分析傳輸線損耗時,Rz與Ra僅能應用于Hammerstad模型,不能應用于更加精確的Huray模型。同時Rz與Ra的準確度也會受測量設備影響,高精度的設備往往價格昂貴。

針對這一問題和需求,寧波德圖科技的技術團隊聯合Intel以及多家銅箔廠商共同研發了銅箔表面粗糙度提取工具SRTool。該工具通過圖像算法讀取銅箔切片圖,生成對應的表面輪廓線。再利用概率分布方法建立粗糙3D模型進行仿真,分析粗糙對傳輸線損耗的影響并生成用以表征銅箔粗糙的Huray模型。

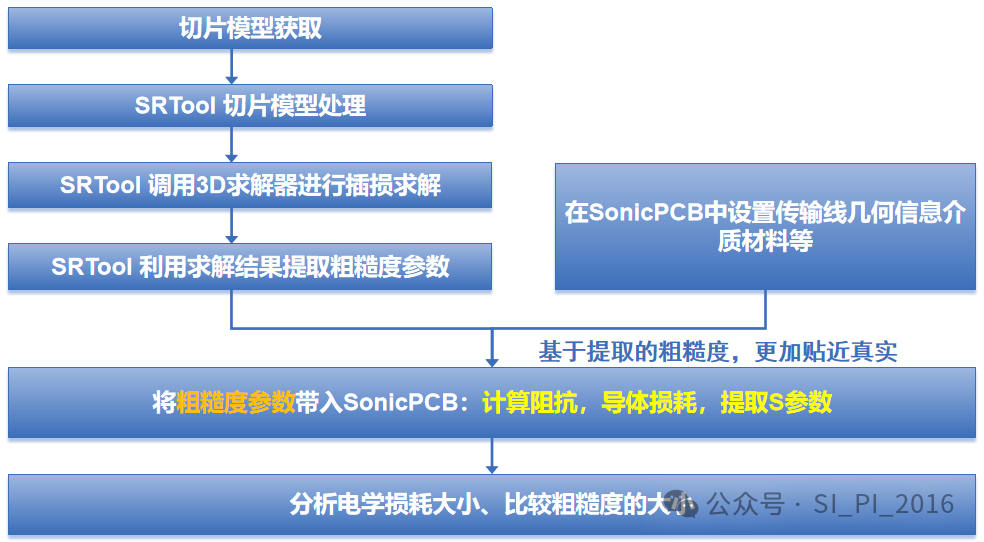

3.1 操作流程:

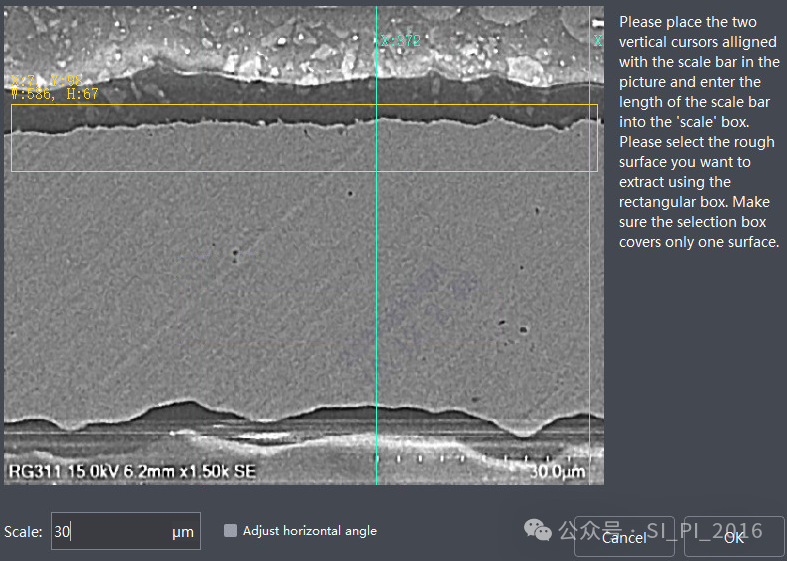

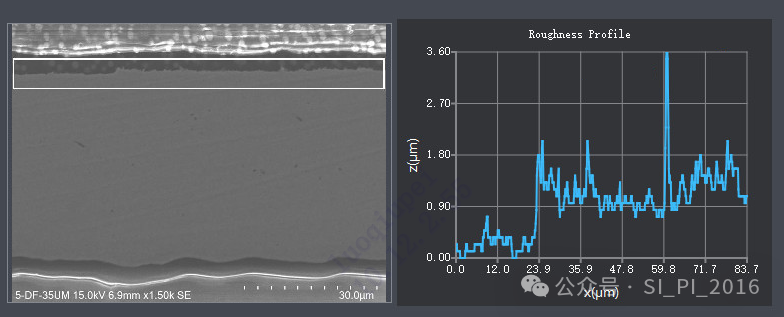

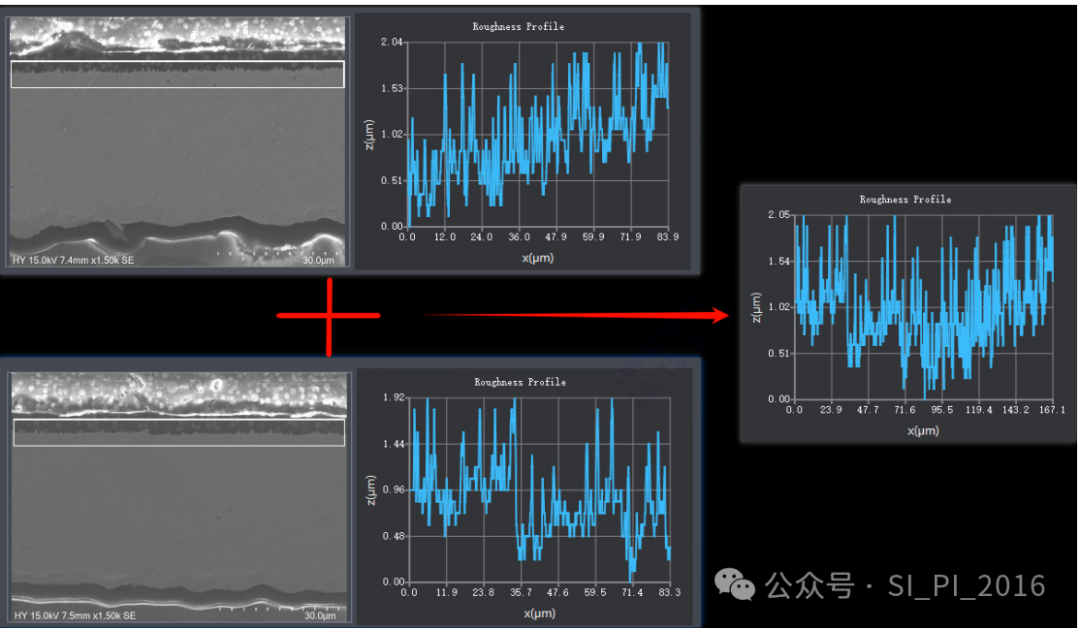

(1)導入銅箔切片圖,讀取粗糙表面并生成輪廓(Profile)。SRTool支持材料庫用以管理不同的粗糙數據。

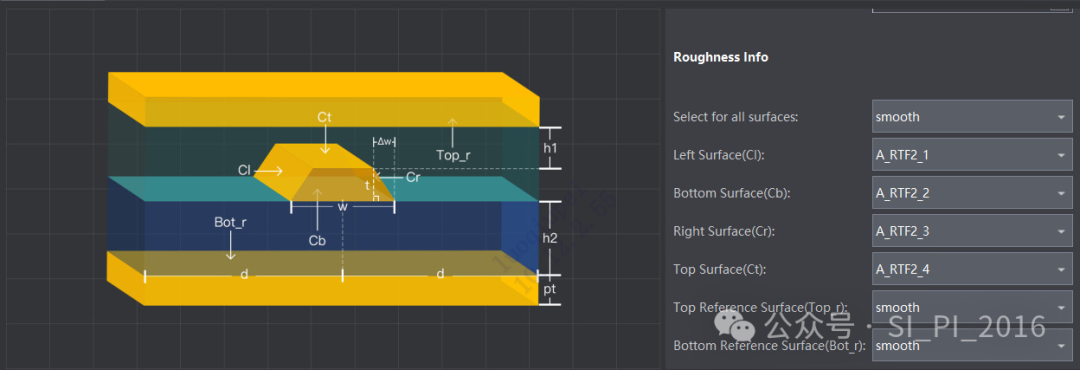

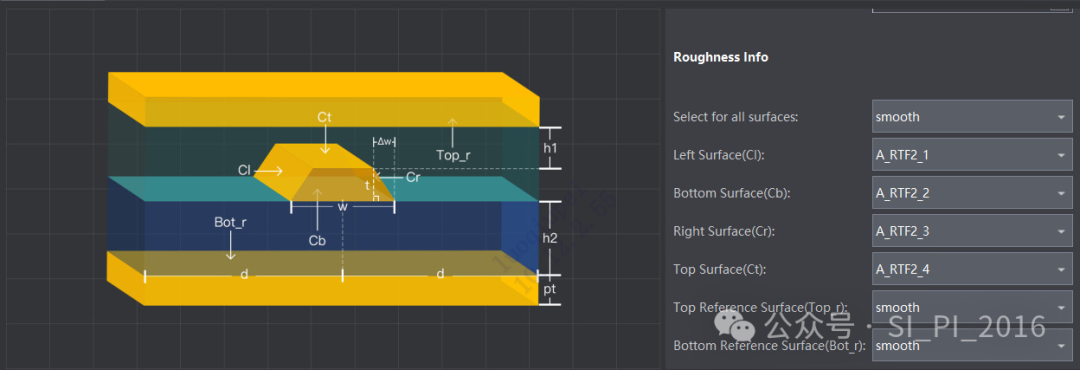

(2)將粗糙數據應用于傳輸線模型的各個表面,包括傳輸線上下左右以及上下參考地。

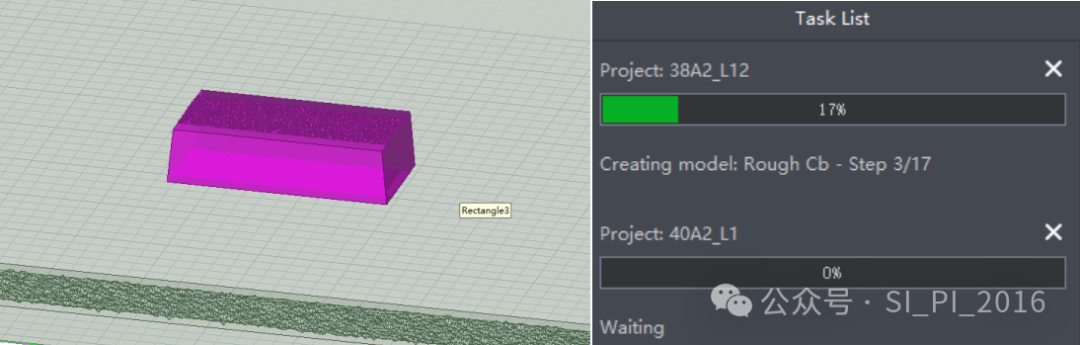

(3)SRTool自動跑3D建模仿真腳本,僅需等待仿真完成。

(4)仿真完成后,SRTool自動讀取仿真結果,分析并生成Huray模型。

(5)將SRTool的結果(Huray模型參數)放入傳輸線仿真軟件中,例如SonicPCB,進一步對傳輸線進行阻抗和S參數分析。

這套流程可以一站式從PCB切片中獲取真實的銅箔表面粗糙度,并在傳輸線S參數求解中直接應用。能夠讓終端客戶的SI/PI工程師快速準確地判斷銅箔粗糙度對損耗的影響,辨別銅箔供應商的粗糙度等級,評估銅箔的選材是否合理。

簡明流程圖如下:

3.2 軟件優勢

(1)模型的原始輸入數據來源于切片圖,更加符合實際

右邊的高度分布圖準確地表達了切片的起伏情況。

(2)提供同一銅箔不同切片的Merge功能,減小切片一致性問題帶來的誤差

下圖兩張切片原本分別是上升趨勢和下降趨勢,在Merge之后,高度分布趨于水平,但是很好地保留了原始合成數據的高度趨勢。

(3)使用3D傳輸線模型仿真,分別設置不同面的粗糙度,貼近應用場景

可以通過右邊的下拉框選擇已導入的切片數據,然后分別設置傳輸線的不同面,最后再送入3D仿真求解器中求解。

(4)獲取業界認可的粗糙度模型參數,方便應用于仿真軟件中

可以獲取Huray模型的參數,并且導出為CSV數據。然后在我司的前仿工具SonicPCB中輸入Huray模型參數或導入CSV并仿真。

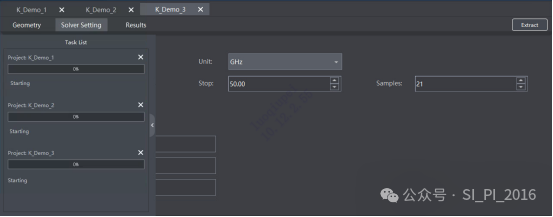

(5)操作簡單,自動化生成3D模型,可以提交多個粗糙度的提取任務,順序執行。

求解支持多任務,點擊導出后,軟件會按照任務隊列依次求解。

3.3 應用案例

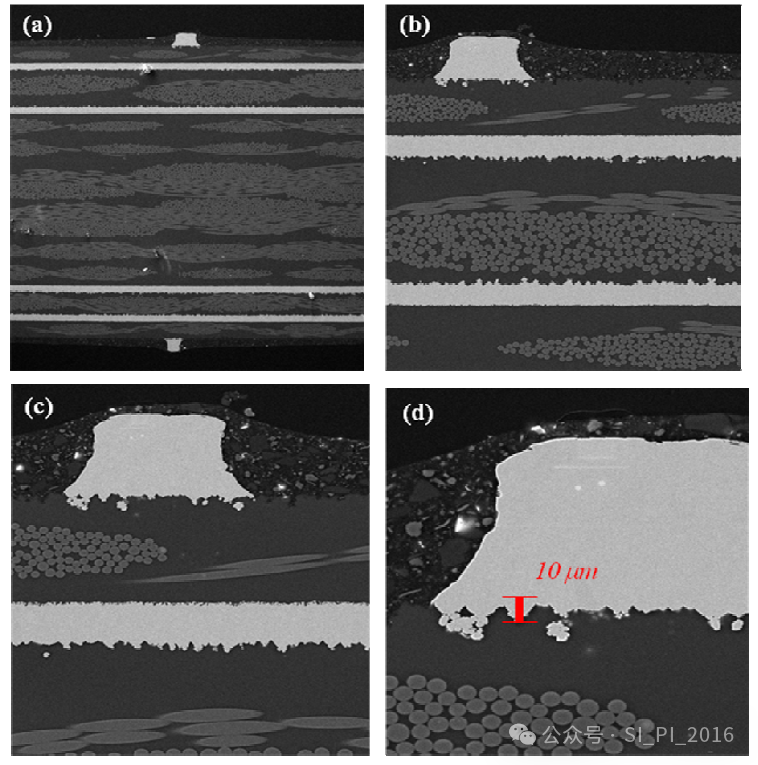

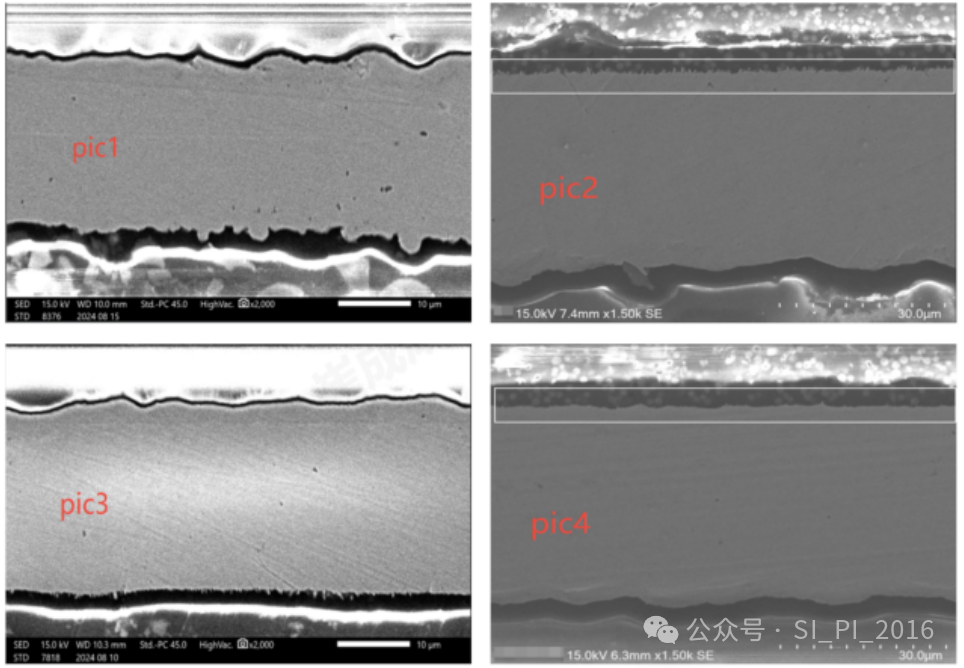

SRTool的這套粗糙度提取流程,已有多個成功案例。以下是客戶的真實案例,有四張銅箔的切片,如下圖所示。

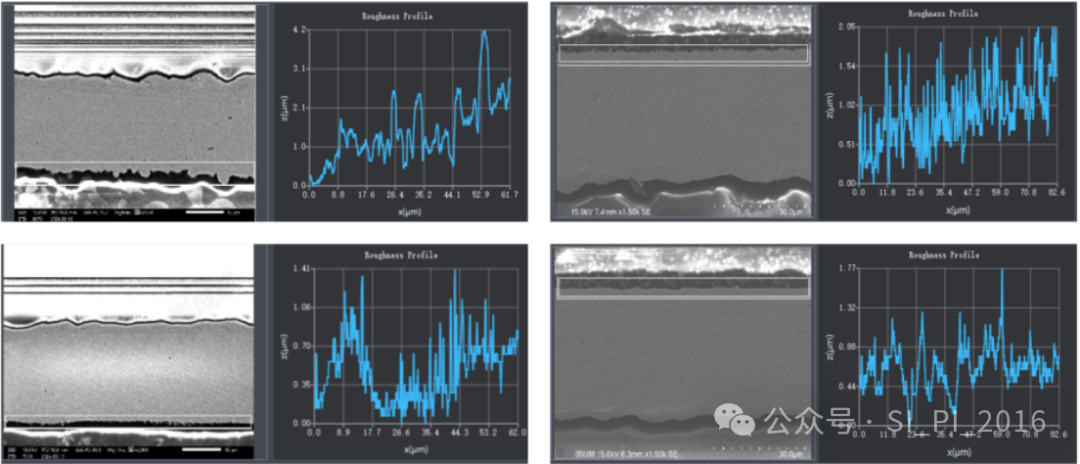

使用SRTool提取以上四張切片的Profile,如下圖所示。

從以上圖像可以發現pic1中輪廓的Rz Ra較大,而pic2中的峰峰間距較小,因此可以粗略判斷這兩個銅箔的粗糙度相對較大。

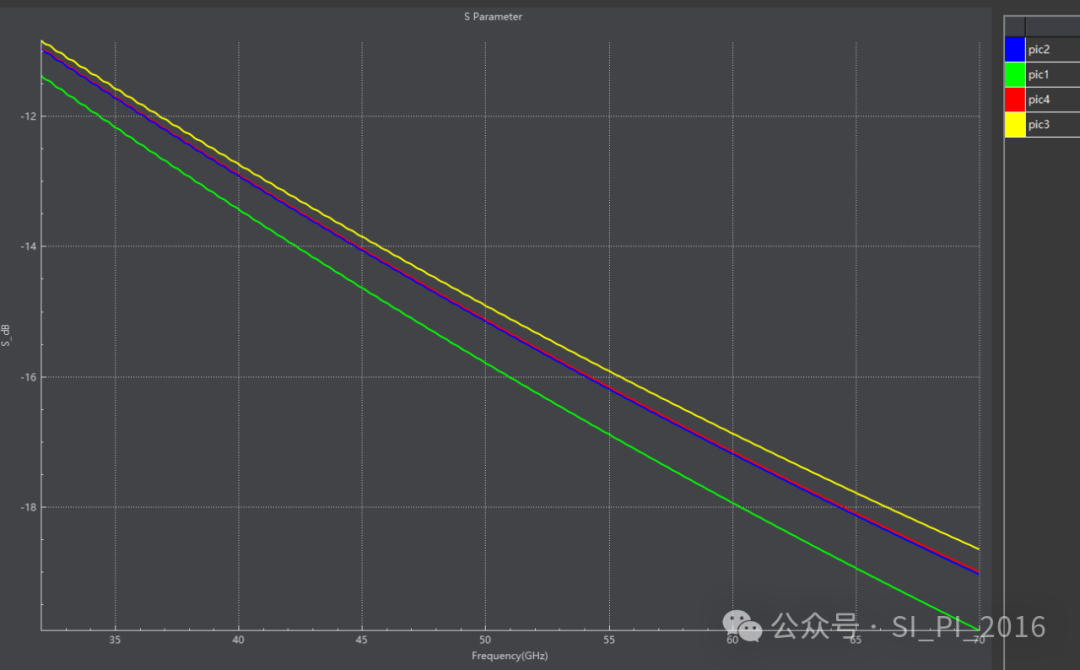

按照上文提到的流程,提取粗糙度,并在SonicPCB中對一段8inch的傳輸線分別施加四個案例的粗糙度,獲取插損曲線,如下圖所示。

根據圖像,可以很直觀地判斷出哪種銅箔所帶來的損耗更小,這也和之前根據profile粗略判斷的結果一致。

并且由圖像可知,在較高頻處,不同粗糙度造成的插入損耗差異已經大于1dB。因此,在高速高頻場景中,粗糙度因素不可以忽視,對于相同的傳輸線結構,不同粗糙度的銅箔也可能會帶來很大的損耗差異。

目前,這套流程的分析結果已完成多組實驗數據,并聯合多家銅箔廠商進行了大量打板測試并取得合理且多位專家認可的結果,SRTool和SonicPCB也都已經投入商業應用并獲得多家大廠測試認可,感興趣的伙伴們可以試用評估。

-

pcb

+關注

關注

4411文章

23916瀏覽量

425403 -

鏈路

+關注

關注

1文章

77瀏覽量

14487 -

高速信號

+關注

關注

1文章

271瀏覽量

18520 -

損耗分析

+關注

關注

0文章

9瀏覽量

7058

原文標題:T66 高速信號鏈路損耗分析以及德圖銅箔表面粗糙度解決方案

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

JNEye鏈路分析工具支持迅速評估高速Altera FPGA和SoC中的高速串行鏈路性能

高速鏈路建模及信號完整性分析系列裝備介紹

高速信號傳輸鏈路的損耗和均衡

高速信號鏈路損耗分析

高速信號鏈路損耗分析

評論