一年一度的ISSCC(International Solid State Circuits Conference的簡(jiǎn)稱,中文名固態(tài)電路年會(huì))正式拉開帷幕,在這個(gè)被稱為“集成電路奧利匹克”的會(huì)議上,來自全球各地的專家齊聚一堂,探討集成電路的未來。計(jì)算機(jī)體系專家David Paterson也在會(huì)議上發(fā)表了題為《50 Years of Computer Architecture:from Mainframe CPUs to DNN TPUs and Open RISC-V》的演講,讓我們看一下體系結(jié)構(gòu)專家眼里的處理器未來。

對(duì)過去處理器發(fā)展的回顧

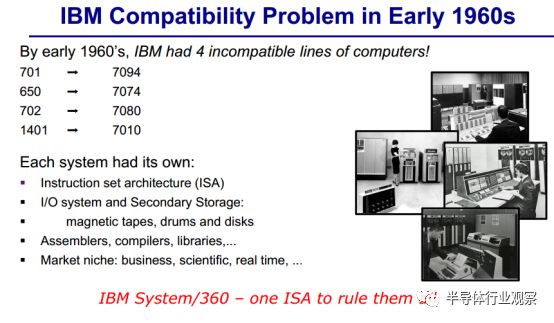

他表示,在20世紀(jì)60年代初,當(dāng)時(shí)IBM同時(shí)擁有4條完全不兼容的產(chǎn)品線(701 ? 7094、650 ? 7074、702 ? 7080和1401 ? 7010),IBM面臨著非常嚴(yán)重的兼容性問題。其中每一條產(chǎn)品線都擁有各自完全獨(dú)立的指令集體系結(jié)構(gòu)(ISA),I/O系統(tǒng)和二次存儲(chǔ),磁盤存儲(chǔ)系統(tǒng),匯編程序,編譯器,庫(kù)以及市場(chǎng)利基。

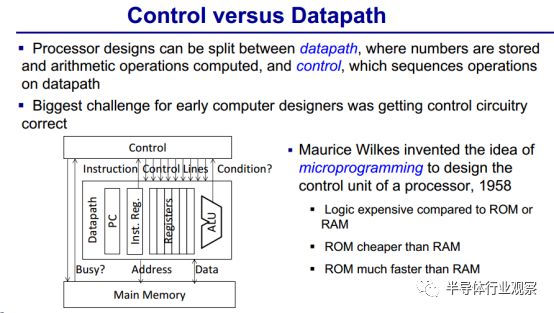

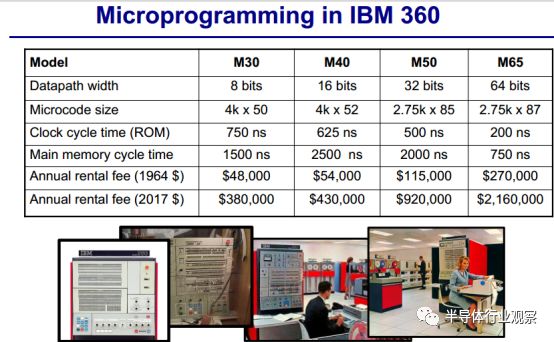

這幾條完全不兼容的產(chǎn)品線也使得當(dāng)時(shí)的處理器設(shè)計(jì)變得異常復(fù)雜,設(shè)計(jì)者必須在數(shù)據(jù)存儲(chǔ)路徑和控制單元之間進(jìn)行非常詳細(xì)的區(qū)分。可以說,早期的計(jì)算機(jī)設(shè)計(jì)者所面臨的最大問題就是控制單元的指令控制線是否正確,能夠起到作用。

此前,Maurice Wilkes在1958年提出了用微程序設(shè)計(jì)的思想來設(shè)計(jì)控制單元,簡(jiǎn)化我們?cè)谠O(shè)計(jì)過程中所遇到的問題,這種情況之下,我們只需要考慮一下幾個(gè)問題:ROM和RAM的價(jià)格問題,ROM比RAM便宜,而且ROM比RAM速度更快。

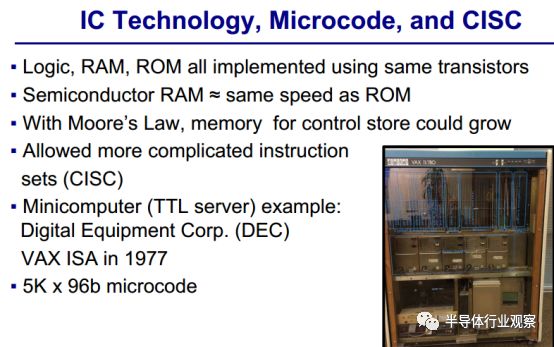

隨著IC技術(shù)、微指令和CISC的發(fā)展,Logic、RAM和ROM都應(yīng)用了相同的晶體管;半導(dǎo)體RAM和ROM的速度也差不多;隨著摩爾定律的發(fā)展,控制指令的存儲(chǔ)空間也逐漸增加;允許更多的CISC;類似TTL 服務(wù)器這樣的小型計(jì)算機(jī)的出現(xiàn),推動(dòng)處理器產(chǎn)業(yè)進(jìn)入了新階段。

伴隨而來的是微處理器技術(shù)的革新。

David Paterson表示,上世紀(jì)70年代,在MOS技術(shù)和主流ISA的推動(dòng)下,計(jì)算機(jī)經(jīng)歷了快速的發(fā)展,出現(xiàn)了以Intel i432為代表的產(chǎn)品。

之后也推出了Intel 8086等劃時(shí)代的產(chǎn)品。

之后就到了微指令機(jī)器的二十世紀(jì)八十年代。

從CISC到RISC,架構(gòu)面臨瓶頸

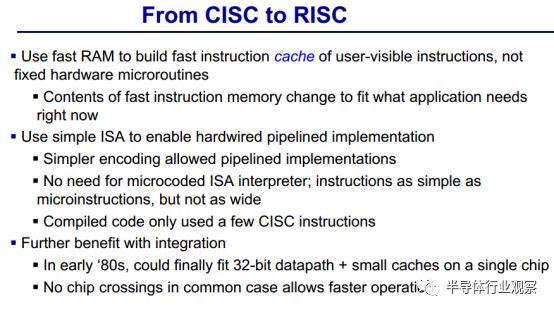

計(jì)算機(jī)發(fā)展之初,ROM比起RAM來說更便宜而且更快,所以并不存在片上緩存(cache)這個(gè)東西。在那個(gè)時(shí)候,復(fù)雜指令集(CISC)是主流的指令集架構(gòu)。然而,隨著RAM技術(shù)的發(fā)展,RAM速度越來越快,成本越來越低,因此在處理器上集成指令緩存成為可能。

同時(shí),由于當(dāng)時(shí)編譯器的技術(shù)并不純熟,程序都會(huì)直接以機(jī)器碼或是匯編語言寫成,為了減少程序設(shè)計(jì)師的設(shè)計(jì)時(shí)間,逐漸開發(fā)出單一指令,復(fù)雜操作的程序碼,設(shè)計(jì)師只需寫下簡(jiǎn)單的指令,再交由CPU去執(zhí)行。

但是后來有人發(fā)現(xiàn),整個(gè)指令集中,只有約20%的指令常常會(huì)被使用到,約占整個(gè)程序的80%;剩余80%的指令,只占整個(gè)程序的20%。

于是1979年,David Paterson教授提出了RISC的想法,主張硬件應(yīng)該專心加速常用的指令,較為復(fù)雜的指令則利用常用的指令去組合。使用精簡(jiǎn)指令集(RISC)可以大大簡(jiǎn)化硬件的設(shè)計(jì),從而使流水線設(shè)計(jì)變得簡(jiǎn)化,同時(shí)也讓流水線可以運(yùn)行更快。

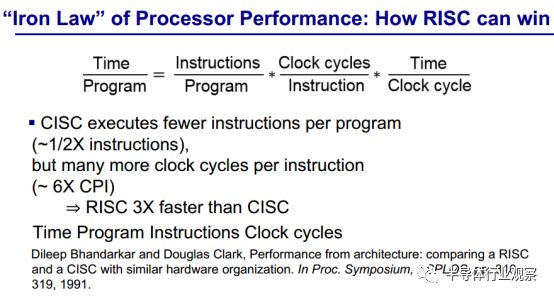

Paterson教授重申了評(píng)估處理器性能的指標(biāo),即程序運(yùn)行時(shí)間。程序運(yùn)行時(shí)間由幾個(gè)因素決定,即程序指令數(shù),平均指令執(zhí)行周期數(shù)(CPI)以及時(shí)鐘周期。程序指令數(shù)由程序代碼,編譯器以及ISA決定,CPI由ISA以及微架構(gòu)決定,時(shí)鐘周期由微架構(gòu)以及半導(dǎo)體制造工藝決定。對(duì)于RISC,程序指令數(shù)較多,但是CPI遠(yuǎn)好于CISC,因此RISC比CISC更快。

據(jù)介紹,RISC有以下多個(gè)優(yōu)點(diǎn):

指令長(zhǎng)度固定,方便CPU譯碼,簡(jiǎn)化譯碼器設(shè)計(jì)。

盡量在CPU的暫存器(最快的存儲(chǔ)器元件)里操作,避免額外的讀取與載入時(shí)間。

由于指令長(zhǎng)度固定,更能受益于執(zhí)行線路管線化(pipeline)后所帶來的效能提升。

處理器簡(jiǎn)化,晶體管數(shù)量少,易于提升運(yùn)作時(shí)脈。比起同時(shí)脈的CISC處理器,耗電量較低。

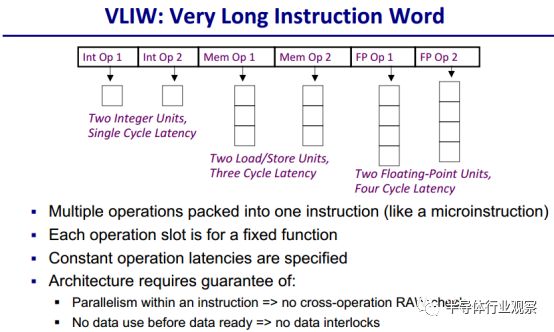

除了CISC和RISC之外,另一種流行(過)的ISA是超長(zhǎng)指令字(VLIW)。

VLIW是美國(guó)Multiflow和Cydrome公司于20世紀(jì)80年代設(shè)計(jì)的體系結(jié)構(gòu),主要應(yīng)用于Trimedia(全美達(dá))公司的Crusoe和Efficeon系列處理器中。AMD的Athlon64處理器系列也是采用這一指令系統(tǒng),包括其服務(wù)器處理器版本Operon。

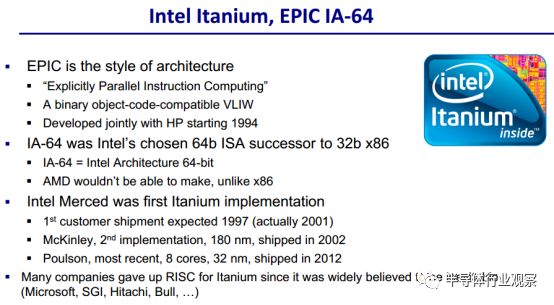

同樣Intel最新的IA-64架構(gòu)中的EPIC也是從VLIW指令系統(tǒng)中分離出來的。VLIW架構(gòu)采用了先進(jìn)的EPIC(清晰并行指令)設(shè)計(jì),我們也把這種構(gòu)架叫做“IA-64架構(gòu)”。每時(shí)鐘周期例如IA-64可運(yùn)行20條指令,而CISC通常只能運(yùn)行1-3條指令,RISC能運(yùn)行4條指令,可見VLIW要比CISC和RISC強(qiáng)大的多。

之后David Paterson還談到了Intel 的安騰處理器和EPIC IA-64。

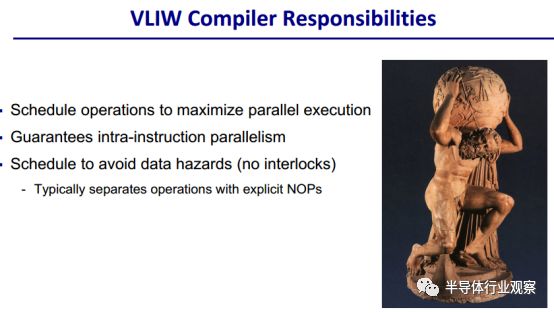

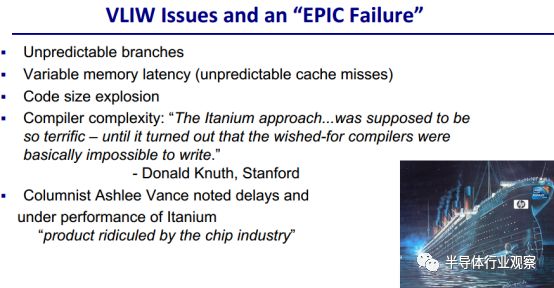

然而,VLIW架構(gòu)遇到了巨大的失敗。VLIW的問題,包括分支預(yù)測(cè)困難,Cache miss無法解決,代碼爆炸以及最關(guān)鍵的,編譯器過于復(fù)雜以至于無法實(shí)現(xiàn)。

此外,基于VLIW指令集字的CPU芯片使得程式變得很大,需要更多的內(nèi)存。更重要的是編譯器必須更聰明,一個(gè)低劣的VLIW編譯器對(duì)性能造成的負(fù)面影響遠(yuǎn)比一個(gè)低劣的RISC或CISC編譯器造成的影響要大。

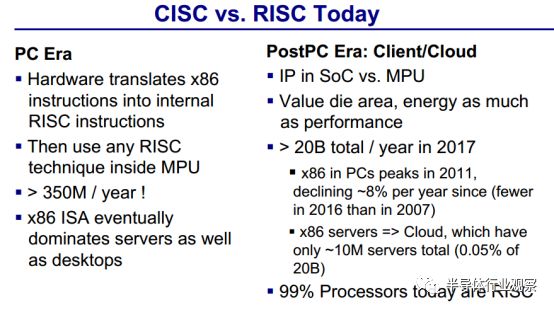

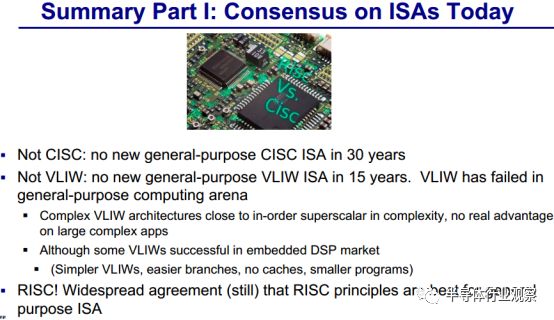

David Paterson還對(duì)今天的ISA做了一個(gè)總結(jié)。他指出,目前處理器的ISA,已經(jīng)30多年沒有新的CISC ISA出現(xiàn)(Intel x86表面用的是CISC但是內(nèi)部有硬件把CISC轉(zhuǎn)換成RISC再真正執(zhí)行)。VLIW在一些嵌入式DSP市場(chǎng)獲得應(yīng)用,但是在其他的市場(chǎng)都沒有獲得成功。考慮到處理器的數(shù)量,目前最主流的通用ISA還是RISC。

IT領(lǐng)域面臨新挑戰(zhàn),TPU橫空出世

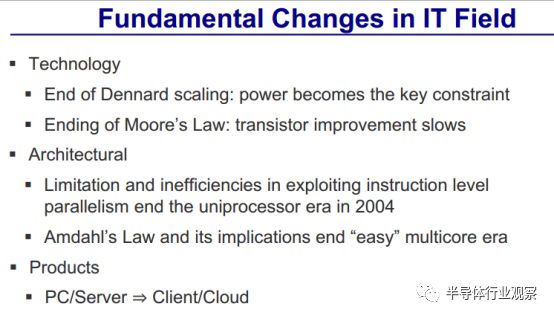

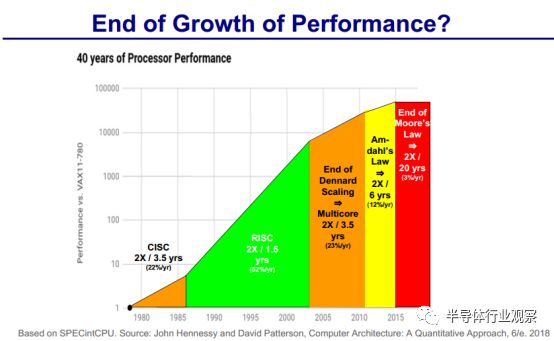

按照David Paterson的觀點(diǎn),現(xiàn)在的IT技術(shù)面臨新的挑戰(zhàn)。例如登納德縮放定律的失效,功耗成為了關(guān)鍵的約束;摩爾定律也面臨困難,晶體管的提升變慢。另外,在架構(gòu)上也有新的問題出現(xiàn)。

同時(shí),處理器性能增長(zhǎng)也面臨性能增長(zhǎng)瓶頸。

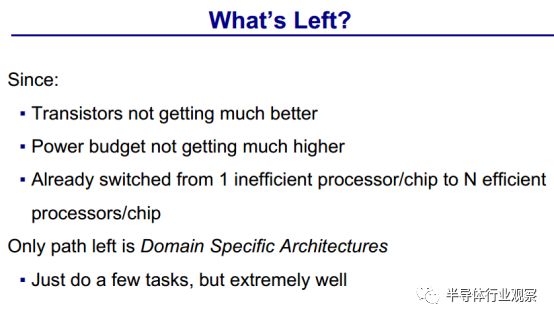

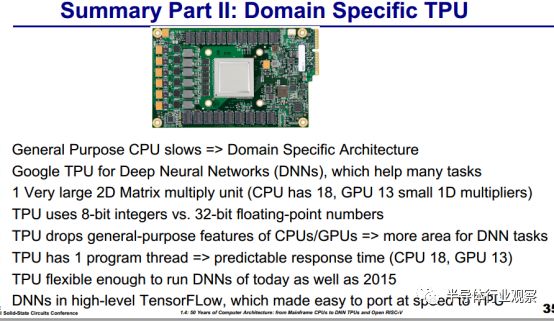

在David Paterson看來,對(duì)于任何運(yùn)算來說,更換新硬件無非是為了兩個(gè)目的:更快的速度和更低的能耗。但由于面臨晶體管并沒有變得更好、功率預(yù)算也不高等問題。許多架構(gòu)師認(rèn)為,現(xiàn)在只有領(lǐng)域定制硬件(domain-specific hardware)能帶來成本、能耗、性能上的重大改進(jìn)。

緊接著,David Paterson介紹了谷歌的TPU。

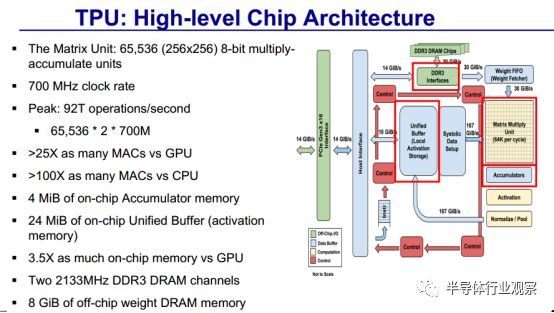

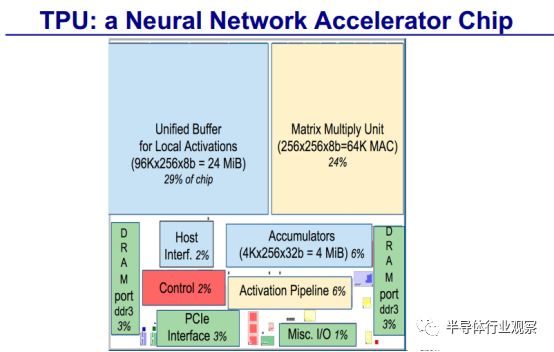

TPU 的核心是一個(gè)65,536的8位矩陣乘單元陣列(matrix multiply unit)和片上28MB的軟件管理存儲(chǔ)器,峰值計(jì)算能力為92 TeraOp/s(TOPS)。

與CPU和GPU由于引入了Cache、亂序執(zhí)行、多線程和預(yù)取等造成的執(zhí)行時(shí)間不確定相比,TPU 的確定性執(zhí)行模塊能夠滿足 Google 神經(jīng)網(wǎng)絡(luò)應(yīng)用上 99% 相應(yīng)時(shí)間需求。

CPU/GPU的結(jié)構(gòu)特性對(duì)平均吞吐率更有效,而TPU針對(duì)響應(yīng)延遲設(shè)計(jì)。正是由于缺乏主流的CPU/GPU硬件特性,盡管擁有數(shù)量巨大的矩陣乘單元 MAC 和極大的偏上存儲(chǔ),TPU 的芯片相對(duì)面積更小,耗能更低。

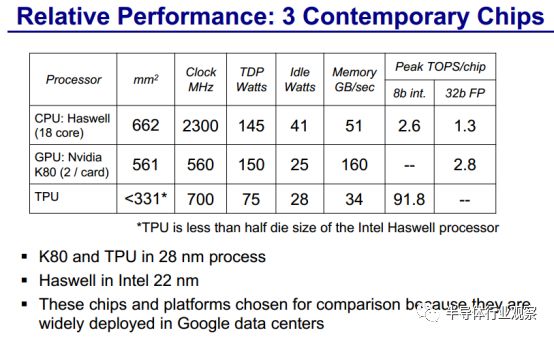

根據(jù)David Paterson的介紹,TPU是一個(gè)神經(jīng)網(wǎng)絡(luò)加速器芯片,將 TPU 與服務(wù)器級(jí)的 Intel Haswell CPU 和 Nvidia K80 GPU 進(jìn)行比較,這些硬件都在同一時(shí)期部署在同個(gè)數(shù)據(jù)中心。測(cè)試負(fù)載為基于 TensorFlow 框架的高級(jí)描述,應(yīng)用于實(shí)際產(chǎn)品的 NN 應(yīng)用程序(MLP,CNN 和 LSTM),這些應(yīng)用代表了我們數(shù)據(jù)中心承載的95%的 NN 推理需求。

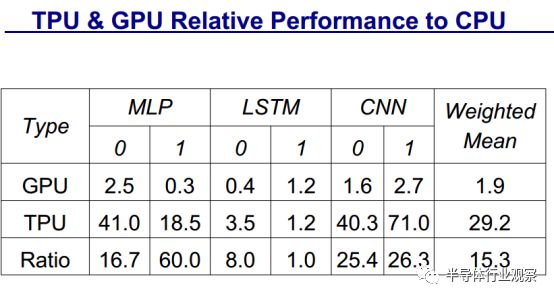

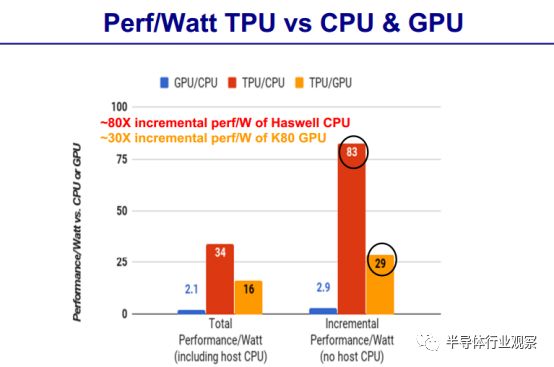

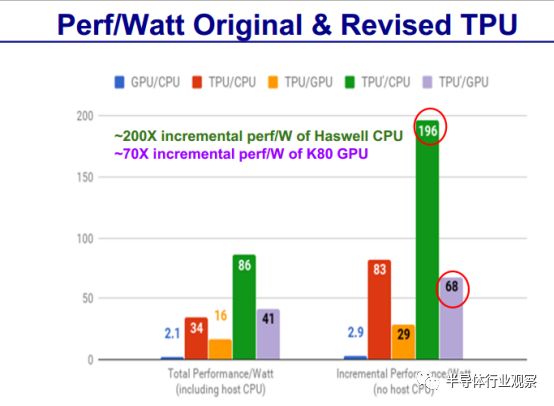

盡管在一些應(yīng)用上利用率很低,但 TPU 平均比當(dāng)前的 GPU 或 CPU 快15~30倍,性能功耗比(TOPS/Watt)高出約 30~80 倍。此外,在 TPU 中采用 GPU 常用的 GDDR5 存儲(chǔ)器能使性能TPOS指標(biāo)再高 3 倍,并將能效比指標(biāo) TOPS/Watt 提高到 GPU 的 70 倍,CPU 的 200 倍。

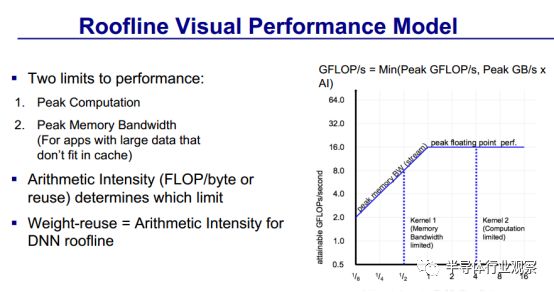

David Paterson還做了一個(gè)可視的性能模型。

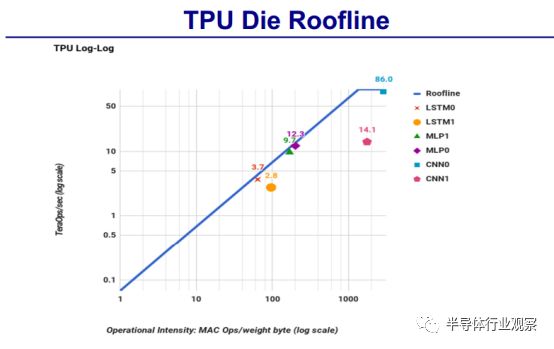

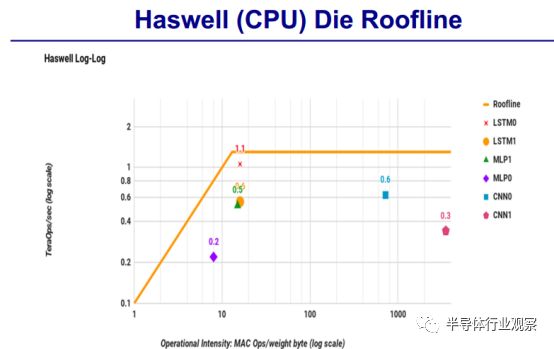

還對(duì)TPU /CPU/GPU 的Die Roofline做了對(duì)比。

TPU:

CPU:

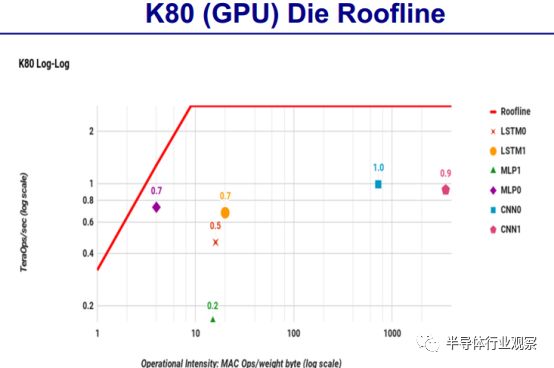

GPU:

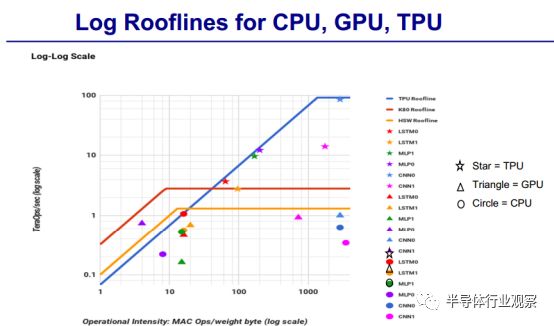

之后David Paterson還對(duì)CPU、GPU和TPU的Log Rooflines做了對(duì)比。

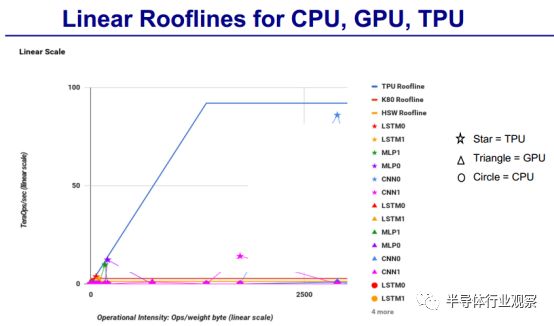

另外還有Linear Rooflines

他還將TPU & GPU的相關(guān)性能與CPU對(duì)比

在性能方面,David Paterson也做了對(duì)比。

還對(duì)TPU做了數(shù)據(jù)對(duì)比

按照David Paterson的總結(jié)了通用CPU開始變慢,特定架構(gòu)的處理器將會(huì)流行與谷歌的TPU在DNN中發(fā)生重要作用,能夠幫助完成不少任務(wù)等問題:

RISC V也是未來的一個(gè)機(jī)遇

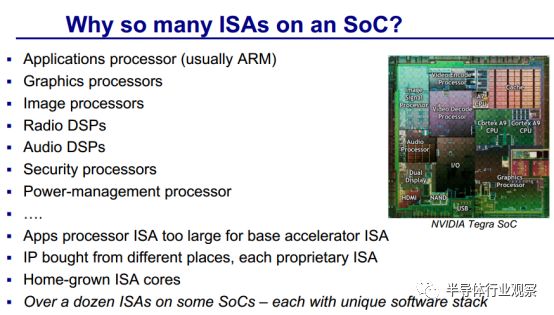

David Paterson表示,SoC上擁有了很多ISA。

緊接著,他提出,我們是否真的需要不同的ISA?這些指令集是否真的需要?dú)w屬于專人?

況且在ISA領(lǐng)域,之前并沒有公認(rèn)的標(biāo)準(zhǔn),也沒有開源免費(fèi)的ISA,僅有商用的ISA,這讓整個(gè)ISA領(lǐng)域的生態(tài)顯得死氣沉沉。David Paterson就提出了是否存在一個(gè)免費(fèi)的ISA讓所有人都能夠使用的問題?于是,RISC-V應(yīng)運(yùn)而生。

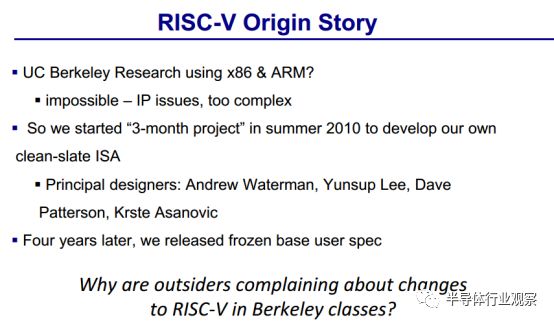

要做開源的ISA,基于x86和ARM都幾乎不可能,因?yàn)樗鼈兌继珡?fù)雜,而且還存在IP的問題。

在2010年夏天,Paterson教授帶領(lǐng)團(tuán)隊(duì)開始從頭開始設(shè)計(jì)一個(gè)干凈的ISA。經(jīng)歷了很多年,經(jīng)過多次流片驗(yàn)證,終于在2014年發(fā)布了最終版spec,就是RISC-V(V是第五代的意思)。

RISC-V作為一個(gè)開源ISA,首先要滿足對(duì)ISA的一般要求。

首先,它必須與現(xiàn)存的主流編程語言和軟件兼容。

第二,它必須有直接硬件實(shí)現(xiàn),而不是一個(gè)虛擬機(jī)。

第三,它必須有很好的彈性,能滿足小至微控制器(MCU)大到超級(jí)計(jì)算機(jī)的需求。

第四,能與各種實(shí)現(xiàn)方式兼容,包括FPGA,ASIC,全定制CPU,以及未來的其他實(shí)現(xiàn)。

第五,需要與各種微架構(gòu)配適,包括有序執(zhí)行,無序執(zhí)行,單發(fā)射,超標(biāo)量等等。

最后,還需要滿足可擴(kuò)展性(可以作為基礎(chǔ)ISA,在特殊用途中加上額外的增強(qiáng)ISA),以及穩(wěn)定性(不會(huì)一直變化,不會(huì)突然消失等等)。

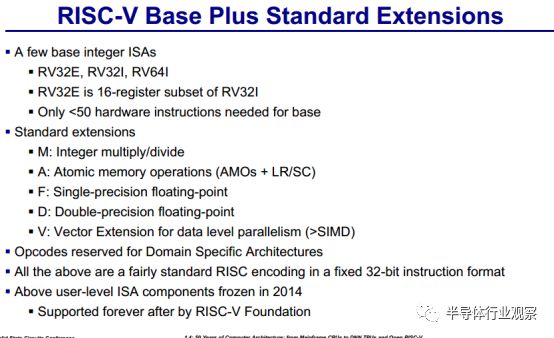

除了滿足一般的需求外,RISC-V還有自己的特色。

這個(gè)新近流行的架構(gòu)還具備以下特點(diǎn):

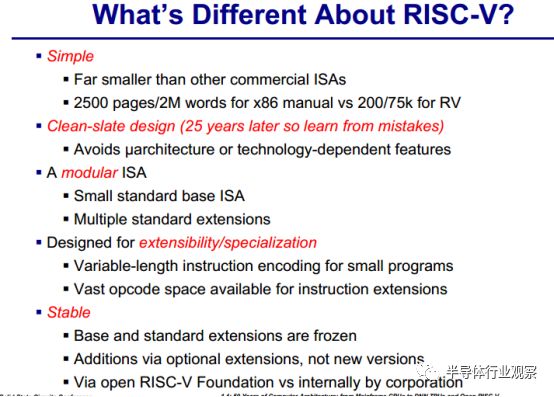

首先,它很簡(jiǎn)單,比其他的商用ISA規(guī)模都要小很多。

第二,它很干凈,例如在用戶與特權(quán)ISA之間涇渭分明,有非常清晰的界限。另外,RISC-V中沒有與微架構(gòu)或?qū)崿F(xiàn)方式有關(guān)的特性,因此具有普適性。

第三,RISC-V是模塊化的ISA,它的基礎(chǔ)ISA集很小,但是可以根據(jù)用戶需求去加載擴(kuò)展集。

最后,RISC-V特別為了可擴(kuò)展性和專精化做了優(yōu)化,使用了可變長(zhǎng)度的指令編碼,并且有許多空間以供指令集擴(kuò)展。

最特別的一點(diǎn)是,RISC-V支撐了一個(gè)開源的社區(qū),包含了非盈利基金會(huì)以及開源代碼庫(kù)。RISC-V的愿景是未來各種靈活而低價(jià)處理器芯片的基礎(chǔ)。RISC-V一開始的貢獻(xiàn)者包括伯克利和SiFive(一家初創(chuàng)公司),目前在征求各類設(shè)計(jì)者加入開源社區(qū),需要代碼以及其他硬件IP(如PLL,PHY等等)。

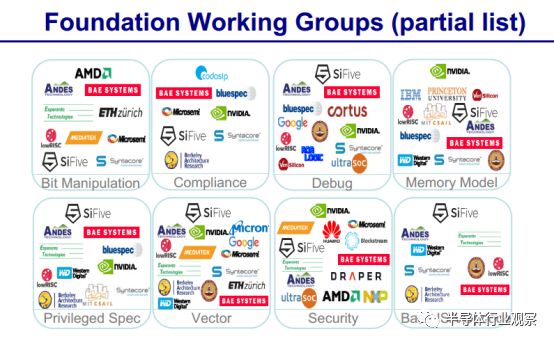

現(xiàn)在的RISC-V聯(lián)盟擁有了過百個(gè)會(huì)員:

另外還有很多的工作組:

David Paterson最后還總結(jié)一下幾大使用RISC和RISC-V的理由。

第一,35年以來,RISC始終是一個(gè)好主意。

第二,RISC-V是免費(fèi)開源架構(gòu),無須付費(fèi)。

第三,它的ISA比起其他ISA來說簡(jiǎn)單許多,因此驗(yàn)證起來也方便許多。RISC-V可以在各種設(shè)計(jì)中比起其他ISA更高效,面積、功耗和性能都更好

第四,RISC-V很穩(wěn)定,不用擔(dān)心突然發(fā)生很大變化或者直接就消失。

第五,RISC-V可以作為各種SoC核的基礎(chǔ)ISA。

現(xiàn)在RISC-V的小目標(biāo),是成為一種適合各種計(jì)算設(shè)備的業(yè)界標(biāo)準(zhǔn)ISA。一個(gè)新的處理器時(shí)代即將到來。

-

ISA

+關(guān)注

關(guān)注

0文章

57瀏覽量

44490 -

TPU

+關(guān)注

關(guān)注

0文章

170瀏覽量

21655 -

開源架構(gòu)

+關(guān)注

關(guān)注

0文章

8瀏覽量

7039 -

處理器架構(gòu)

+關(guān)注

關(guān)注

0文章

8瀏覽量

6777

原文標(biāo)題:David Paterson眼里的處理器架構(gòu)未來

文章出處:【微信號(hào):icbank,微信公眾號(hào):icbank】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

TMS320VC5402 定點(diǎn)數(shù)字信號(hào)處理器深度解析

SMJ320C80數(shù)字信號(hào)處理器:架構(gòu)、特性與應(yīng)用全解析

TAS3103A數(shù)字音頻處理器:特性、架構(gòu)與應(yīng)用詳解

MAX1232微處理器監(jiān)控器:高效可靠的系統(tǒng)守護(hù)專家

Cortex-M0 處理器介紹

利用Verdi調(diào)試協(xié)處理器的實(shí)現(xiàn)步驟

蜂鳥E203協(xié)處理器EAI指令及接口

基于E203 NICE協(xié)處理器擴(kuò)展指令

云拼接處理器的性能如何?

龍芯發(fā)布新一代處理器,進(jìn)軍服務(wù)器和AI處理器市場(chǎng)

龍芯處理器支持WINDOWS嗎?

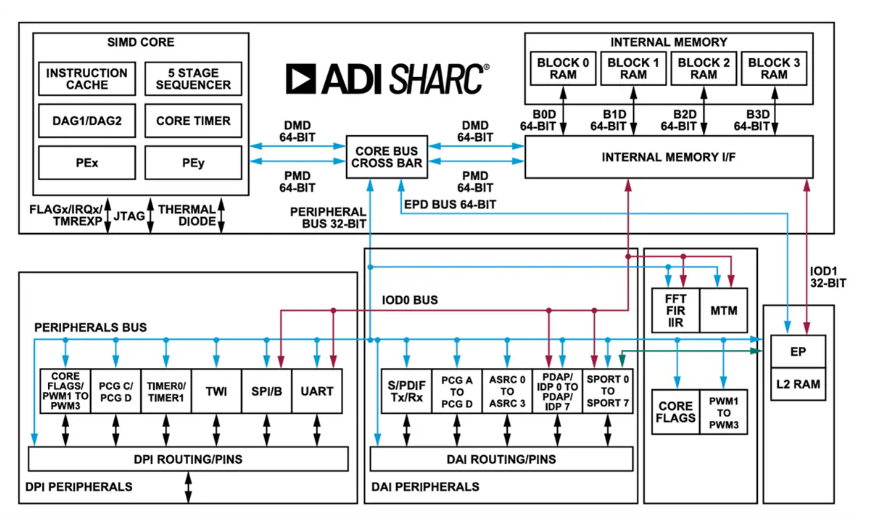

Analog Devices Inc. ADSP1802 SHARC?處理器數(shù)據(jù)手冊(cè)

技術(shù)分享 | 如何在2k0300(LoongArch架構(gòu))處理器上跑通qt開發(fā)流程

ADSP1802 SHARC處理器技術(shù)手冊(cè)

專家與處理器架構(gòu)未來

專家與處理器架構(gòu)未來

評(píng)論