“本文探討了不同地平面情況下的電容耦合及電感耦合,并給出了 PCB 布線時的注意事項。”

普遍認同的觀點是,地平面為電流提供了一個低電感和低電阻的返回路徑,并且能夠防止不同導線之間的串擾(crosstalk)或耦合(coupling)。 地平面通過提供一個與導線物理距離非常接近的電流返回路徑來實現這一點。電感和感性耦合取決于形成的回路面積,而地平面通過最小化這個面積來減少電感和感性耦合。在容性耦合的情況下,地平面“短路”了導線之間的電場,從而最小化了相互電容。 在這些基本要點之后,大家開始出現分歧。有些人說地平面應在電路板的兩側,有些人則說只應在一側。有些人認為地平面應該在電路的不同區域之間分割,而其他人則認為這樣做會使情況變得更糟。有人說應該在高速信號之間放置屏蔽線,也有人說不應該。

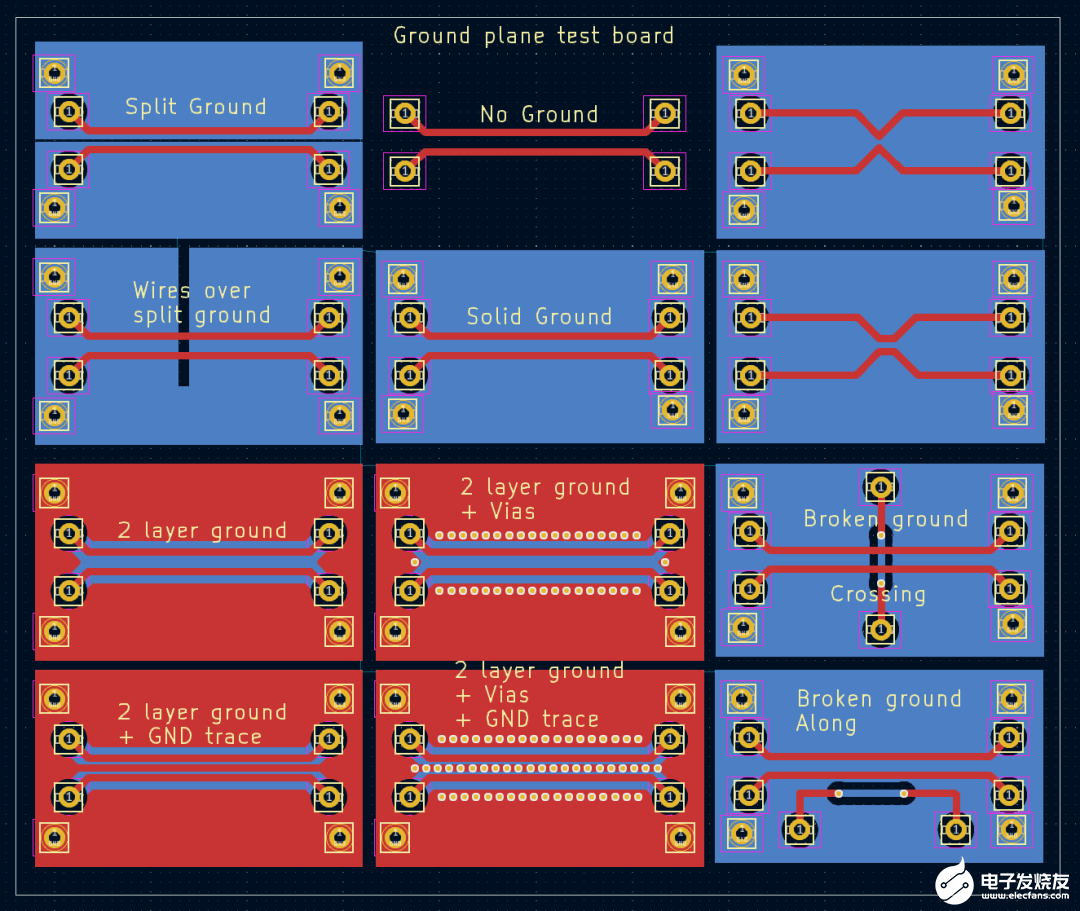

為了測試其中的一些說法,我設計了一塊 1.6 mm 厚的電路板,上面有幾對 15 mm 長的導線,導線之間有 2 mm 的間隙。無論是電容耦合還是電感耦合,長而平行且靠近的線路都是最糟糕的情況。每根導線的兩端都有一個引腳,如果存在地平面,就在導線引腳旁邊放置一個地引腳,以保持返回路徑盡可能接近:

其中一對沒有地平面,另一對只有底層的一個簡單的地平面,其余的地平面各有不同:

兩個走線之間有分割的地平面。

兩個走線穿過分割的地平面的分割處。

有地平面,走線跳轉到底層。(一個平行,一個交叉)

兩層都有地平面

兩層都有地平面,導線旁有過孔。

兩層都有地平面,帶有屏蔽線

兩層都有地平面,帶有屏蔽線,且屏蔽線上和走線旁都有過孔。

我用 50 MHz 正弦波(10ns 上升/下降時間)進行了測試,這應該能代表典型的業余項目,但不適用于微波范圍的測試(所使用的波長比走線大得多)。

電容耦合

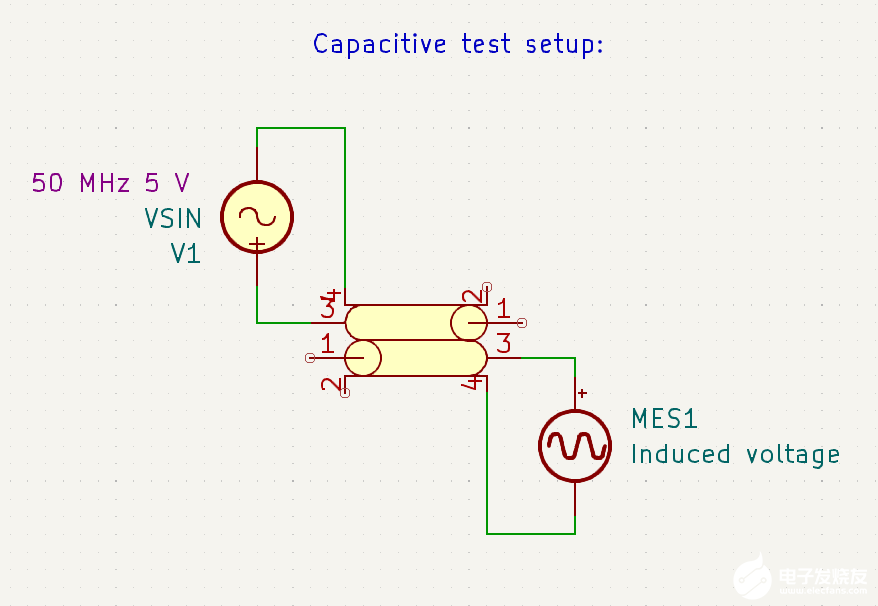

實驗目的:測量電容耦合

實驗設備:

函數發生器(Function generator):用于產生一個 5V 的 50MHz 正弦波信號。

示波器(Scope):用于測量和顯示信號。

實驗步驟:

將函數發生器的輸出連接到一根導線的一端。

將示波器的探頭連接到另一條導線的另一端,用于測量信號。

在進行有地平面的測試時,移除了示波器探頭的標準地線(ground lead),并使用一根短于2厘米的導線,將探頭的地環(ground ring)連接到地平面上。

在沒有地平面的測試中,直接將示波器的地夾(ground clip)夾到函數發生器的地線上。

示波器探頭對地的電容大約是10皮法(pF),大約是74HC邏輯門輸入電容的兩倍。這些測量值的精度大約是5%,毫伏級別的電壓變化可能是由于測量誤差造成的,不必過于關注。 以下為測量結果:

| 配置 | 耦合電壓峰峰值 |

| 無地平面,15cm示波器地線夾提供地 | 800 mV |

| 標準地平面 | 340 mV |

| 走線之間有分割的地平面 | 352 mV |

| 走線跨過分割的地平面 | 360 mV |

| 標準地平面,但有導線切割穿過地平面;且待測的信號線跨過切割的導線 | 351 mV |

| 標準地平面,但有導線切割穿過地平面;且待測的信號線平行靠近切割的導線 | 340 mV |

| 雙面的地平面 | 294 mV |

| 雙面的地平面+縫合孔(僅一側) | 300 mV |

| 雙面的地平面+屏蔽線 | 88 mV |

| 雙面的地平面+屏蔽線+縫合孔 | 48 mV |

地平面對電容耦合的影響:

即使在最糟糕的布局中,接地平面也能將電容耦合降低 2 倍以上。這意味著地平面提供了一個低電感和低電阻的電流返回路徑,并且能夠減少不同走線之間的串擾和耦合。

通常建議在電源、數字和模擬部分之間分割地平面,但這樣做實際上增加了耦合。

在雙面接地的情況下,走線只有在兩側都有縫合孔的情況下耦合才會有所改善;如果在兩個走線之間放置一個接地的屏蔽走線,效果會更好(比沒有地平面好16倍以上)。

地平面下的短走線的影響:

在遠小于波長的尺度上,地平面下的短走線影響相對較小。

我測量了從一個交叉走線耦合到主走線的信號為153毫伏,這個值并不小,但并不像平行走線那樣糟糕。

地平面上走線的對地電容:

地平面上的走線對地有顯著的電容,對于1毫米寬的走線大約是每厘米0.7皮法。這可能會給高阻抗信號帶來麻煩,即使是相對較短的走線。

隨著板層數的增加,這種電容會變得更糟,尤其是當習慣于將地/電源平面放置在板的中間層時。

驅動阻抗對電容耦合的影響:

驅動阻抗對于電容耦合非常重要。當受影響的走線通過 100Ω電阻驅動而不是開路時,耦合信號降低到原始電壓的約1/4。

電感耦合

對于電感耦合,我也使用了 50 MHz 正弦波,但將導線的另一端接地。我還添加了一個 10 歐姆的電流檢測電阻(10mV = 1mA)來測量電流。

同樣,這些測量值的精確度僅為 5%左右,因此無需在意單毫伏的差異。

| 配置 | 旁路電壓峰峰值 | 耦合電壓峰峰值 |

| 無地平面,15cm示波器地線夾提供地 | 8 mV | 62 mV |

| 標準地平面 | 12 mV | 26 mV |

| 走線之間有分割的地平面 | 11 mV | 28 mV |

| 走線跨過分割的地平面 | 10 mV | 29 mV |

| 標準地平面,但由導線切割穿過地平面;且待測的信號線跨過切割的導線 | 8 mV | 44 mV |

| 標準地平面,但由導線切割穿過地平面;且待測的信號線平行靠近切割的導線 | 9 mV | 28 mV |

| 雙面的地平面 | 11 mV | 28 mV |

| 雙面的地平面+縫合孔 | 9 mV | 22 mV |

| 雙面的地平面+屏蔽線 | 10 mV | 33 mV |

| 雙面的地平面+屏蔽線+縫合孔 | 10 mV | 7 mV |

這里的結果與電容耦合的結果類似,并不與電容耦合的結論相悖。雖然與電容耦合相比,電感耦合看起來微不足道,但它會對驅動阻抗很低(如測試中使用的 0 歐姆短路)的線路產生影響,而且這里使用的電流僅為毫安,而不是驅動 MOSFET 柵極等常用的幾安培電流。

耦合到底重要嗎?

雖然50 MHz的頻率看似很高,但數字信號中的耦合現象很容易發生。即使方波的頻率只有幾千赫茲,根據上升時間的不同,諧波也可能高達數百兆赫茲。由于低阻抗輸出和邏輯電平之間的較大差距,數字線路本身具有相當強的抗干擾能力。 然而,大多數項目都會在某些時候處理模擬信號,而這些信號很容易受到快速切換的數字線路的干擾。最簡單的解決方法是將數字部分和敏感的模擬部分物理隔離,并避免它們之間的平行走線。使用去耦電容、磁珠和地平面保持電源清潔也非常重要。高阻抗線路很容易出現問題,因此盡可能避免高阻抗線路,并保持他們的長度盡可能的短是理想的選擇。最后的辦法是在地平面上使用帶縫合孔的屏蔽線。 如果耦合不可避免,另一種方法是降低數字信號的速度,例如在輸出端放置一個 5 千歐電阻。這不會對低速信號產生影響,但可以減緩有問題的信號邊緣。 另一種情況是電流的返回路徑不是地平面,這種情況下地平面的效果會大打折扣。在這種情況下,在PCB上布線時要讓信號走線和返回路徑盡可能靠近,并保持整體長度盡可能短。

參考文獻: https://10maurycy10.github.io/projects/testing_groundplanes/ 本文遵循 Creative Commons Attribution-ShareAlike 4.0 International License.

注意:如果想第一時間收到 KiCad 內容推送,請點擊下方的名片,按關注,再設為星標。

常用合集匯總:

和 Dr Peter 一起學 KiCad

KiCad 8 探秘合集

KiCad 使用經驗分享

KiCad 設計項目(Made with KiCad)

常見問題與解決方法

KiCad 開發筆記

插件應用

發布記錄

審核編輯 黃宇

-

pcb

+關注

關注

4415文章

23936瀏覽量

425758 -

電感耦合

+關注

關注

1文章

71瀏覽量

16438

發布評論請先 登錄

射頻PCB的“隱形殺手”:90%的工程師都忽視的鋪銅細節!

PCB接地設計實戰避坑指南:從“環路”到“干凈地”的進階之路

探究PCB樣板貼片技術特點

探究薄膜射頻/微波定向耦合器 CP0603 SMD 類型

探索薄膜射頻/微波定向耦合器CP0402:卓越性能背后的設計奧秘

EXCUSE ME,表層的AC耦合電容和PCB內層的高速線會有串擾?

到底DDR走線能不能參考電源層啊?

降低adc在不同PCB上的噪聲,如何做到接近AD4134驗證板噪聲水平?

多層PCB板在醫療領域的應用

如何減小DAC電路的耦合影響?

PCB疊層設計避坑指南

PCB的EMC設計(一):層的設置與排布原則

PCB 地平面奧秘及耦合的探究

PCB 地平面奧秘及耦合的探究

評論