“持續更新 8 年,Github 超過 1k star 的項目。一種使用文本替代原理圖的語言。”

追蹤 skidl 項目很久了,之所以之前沒有分享是因為老版本只能支持 KiCad 5.0 符號庫的解析,而且生成的網表也僅能支持 KiCad 6,所以用起來比較麻煩。最近作者又更新了一個大版本,全面支持 KiCad 7 和 KiCad 8,雖然仍有一些問題,但跑起來比之前方便了很多。AI 時代的到來,讓自動化設計又多了一個研究的方向。由于 skidl 的設計初衷就是用文本描述原理圖,這對于機器學習來說無疑是非常合適的!感興趣的小伙伴趕緊學習起來吧,有興趣進一步討論的也可以私信我或留言。SKiDL 簡介

通過 SKiDL Python 軟件包,您可以用文本描述電子元件之間的連接。生成的 Python 程序可對常見錯誤進行電氣規則檢查,并輸出網表,作為 PCB Layout 工具的輸入。-

項目主頁:https://github.com/devbisme/skidl

-

License: MIT

-

文檔:http://devbisme.github.io/skidl

-

用戶論壇:https://github.com/devbisme/skidl/discussions

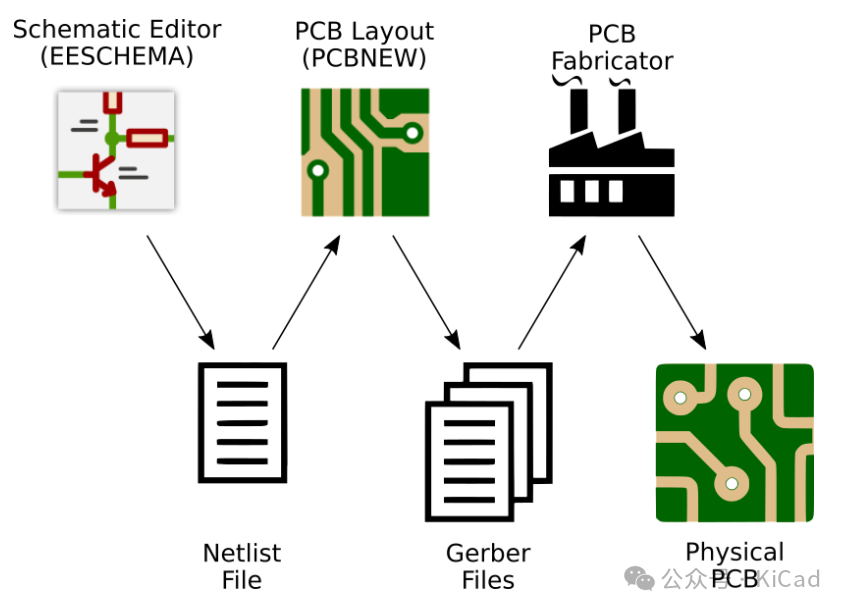

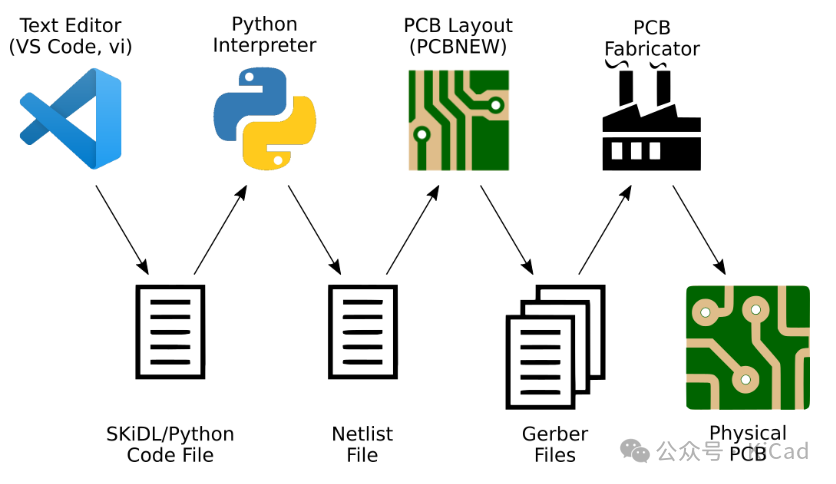

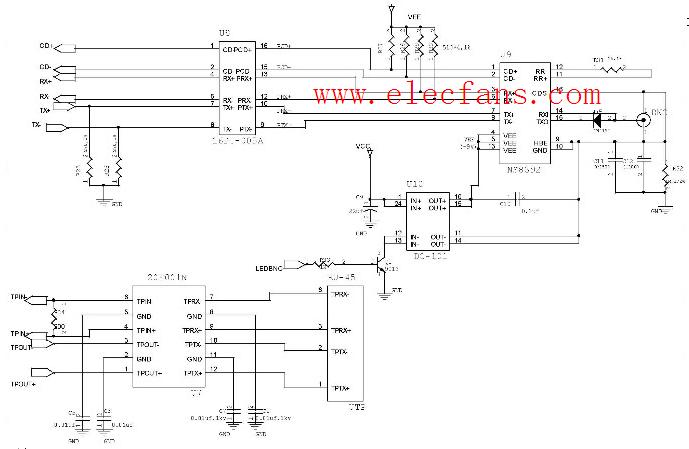

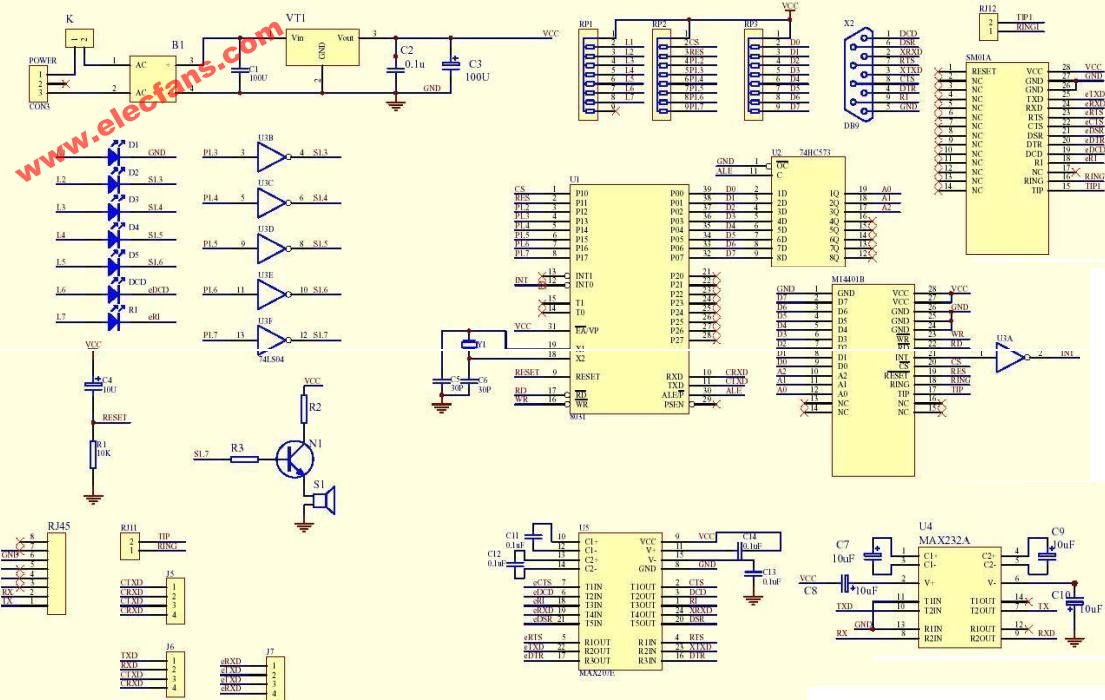

skidl 希望做到的,提供一個選項,既可以通過傳統方式設計原理圖(下圖一),也可以用代碼的方式實現(下圖二):

功能

-

語法強大、靈活(因為它是 Python)。

-

允許對電子電路進行簡潔描述(想象一下不需要在多頁原理圖中追蹤信號)。

-

允許對電子電路進行文本描述(想想在電路中使用 diff和 git)。

-

針對常見錯誤(如未連接器件的 I/O 引腳)執行電氣規則檢查 (ERC)。

-

支持電子設計的平鋪/分層/混合描述。

-

支持設計復用(想象一下使用 PyPi 和 Github 發布電子設計)。

-

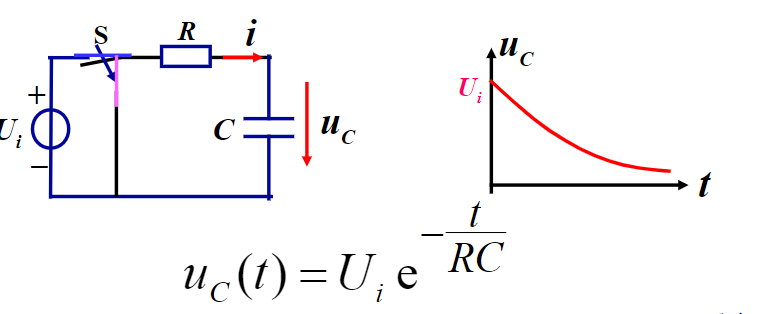

可創建智能電路模塊,這些模塊的行為/結構可通過參數改變(想想濾波器,其元件值可根據你所需的截止頻率自動調整)。

-

可與任何 ECAD 工具配合使用(只需兩種方法:一種用于讀取元件庫,另一種用于輸出正確的網表格式)。

-

可執行 SPICE 仿真(僅限 Python 3)。

-

充分利用 Python 生態系統的所有優勢(因為它是 Python)。

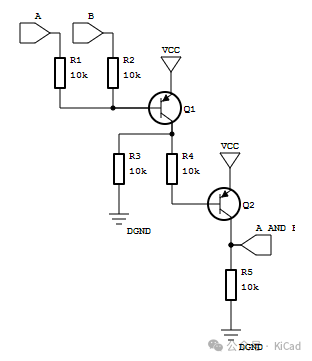

舉例

下面的 SKiDL 程序描述了一個由分立晶體管構建的雙輸入 AND 門,作為一個非常簡單的例子:

以下是輸出的網表,可以直接在 KiCad 中導入:from skidl import *# Create part templates.q = Part("Device", "Q_PNP_CBE", dest=TEMPLATE)r = Part("Device", "R", dest=TEMPLATE)# Create nets.gnd, vcc = Net("GND"), Net("VCC")a, b, a_and_b = Net("A"), Net("B"), Net("A_AND_B")# Instantiate parts.gndt = Part("power", "GND") # Ground terminal.vcct = Part("power", "VCC") # Power terminal.q1, q2 = q(2) # Two transistors.r1, r2, r3, r4, r5 = r(5, value="10K") # Five 10K resistors.# Make connections between parts.a & r1 & q1["B C"] & r4 & q2["B C"] & a_and_b & r5 & gndb & r2 & q1["B"]q1["C"] & r3 & gndvcc += q1["E"], q2["E"], vcctgnd += gndtgenerate_netlist(tool=KICAD8) # Create KICAD version 8 netlist.

(export (version D)(design(source "/home/devb/projects/KiCad/tools/skidl/tests/examples/svg/simple_and_gate.py")(date "07/19/2024 05:54 AM")(tool "SKiDL (1.2.2)"))(components(comp (ref(value GND)(footprint )(fields(field (name F0)(field (name F1) GND))(libsource (lib power) (part GND))(sheetpath (names /top/18388231966295430075) (tstamps /top/18388231966295430075)))(comp (ref(value VCC)(footprint )(fields(field (name F0)(field (name F1) VCC))(libsource (lib power) (part VCC))(sheetpath (names /top/12673122245445984714) (tstamps /top/12673122245445984714)))(comp (ref Q1)(value Q_PNP_CBE)(footprint )(fields(field (name F0) Q)(field (name F1) Q_PNP_CBE))(libsource (lib Device) (part Q_PNP_CBE))(sheetpath (names /top/5884947020177711792) (tstamps /top/5884947020177711792)))(comp (ref Q2)(value Q_PNP_CBE)(footprint )(fields(field (name F0) Q)(field (name F1) Q_PNP_CBE))(libsource (lib Device) (part Q_PNP_CBE))(sheetpath (names /top/12871193304116279102) (tstamps /top/12871193304116279102)))(comp (ref R1)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/17200003438453088695) (tstamps /top/17200003438453088695)))(comp (ref R2)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/12314015795656540138) (tstamps /top/12314015795656540138)))(comp (ref R3)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/11448722674936198910) (tstamps /top/11448722674936198910)))(comp (ref R4)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/2224275500810828611) (tstamps /top/2224275500810828611)))(comp (ref R5)(value 10K)(footprint )(fields(field (name F0) R)(field (name F1) R))(libsource (lib Device) (part R))(sheetpath (names /top/3631169005149914336) (tstamps /top/3631169005149914336))))(nets(net (code 1) (name A)(node (ref R1) (pin 1)))(net (code 2) (name A_AND_B)(node (ref Q2) (pin 1))(node (ref R5) (pin 1)))(net (code 3) (name B)(node (ref R2) (pin 1)))(net (code 4) (name GND)(node (ref(node (ref R3) (pin 2))(node (ref R5) (pin 2)))(net (code 5) (name N$1)(node (ref Q1) (pin 2))(node (ref R1) (pin 2))(node (ref R2) (pin 2)))(net (code 6) (name N$2)(node (ref Q1) (pin 1))(node (ref R3) (pin 1))(node (ref R4) (pin 1)))(net (code 7) (name N$3)(node (ref Q2) (pin 2))(node (ref R4) (pin 2)))(net (code 8) (name VCC)(node (ref(node (ref Q1) (pin 3))(node (ref Q2) (pin 3)))))

注意事項

skidl 在 Windows 上運行的時候經常會碰到問題。最常見的問題是沒有正確設置符號庫的環境變量,導致無法找到符號庫,解析錯誤。這個錯誤可以在代碼中加入以下語句解決:

os.environ["KICAD8_SYMBOL_DIR"] = "C:\symbols"

“=” 號后面的路徑為實際的符號路徑。

如果您使用的不是 KiCad 8,而是其他版本的 KiCad,那么最好設置一下默認工具:

set_default_tool(KICAD8)

同樣的,輸出網表的時候也要指定網表的版本(K8/K7/K6 網表格式有變動):

generate_netlist(tool=KICAD8)

此外, 目前版本的 skidl 還可以直接生成原理圖和 PCB,但功能尚不完備,環境配置比較復雜,建議編程基礎較好的小伙伴嘗試。結束語

skidl 的具體使用方式,這里就不再贅述了,有興趣的小伙伴可以自行閱讀 skidl 的文檔,遇到問題也可以搜索倉庫中的 issue 和 forum,作者 Dave 也非常樂意與大家互動,解答大家的問題。 最后總結一下 skidl 做了什么:用 python 代碼實現圖形界面的原理圖設計。具體的實現方式為:- 通過環境變量找到需要使用的原理圖符號,parse出符號的引腳編號(名稱)

- 在文本編輯器(或IDE)中使用編程語言連接這些管腳

- 生成 KiCad 格式的網表

-

電路原理圖

+關注

關注

40文章

356瀏覽量

40162 -

python

+關注

關注

58文章

4881瀏覽量

90270 -

KiCAD

+關注

關注

6文章

326瀏覽量

10511

發布評論請先 登錄

如何讀懂電路原理圖

開源工具SkiDL - 用Python來描述電路

SkiDL:使用 Python 設計電路原理圖

SkiDL:使用 Python 設計電路原理圖

評論