由于芯片設(shè)計復(fù)雜度的提升、集成規(guī)模的擴大,以及產(chǎn)品上市時間要求的縮短,使得設(shè)計驗證變得更加困難。特別是在多FPGA環(huán)境中,設(shè)計調(diào)試和驗證的復(fù)雜性進(jìn)一步增加,傳統(tǒng)的調(diào)試手段難以滿足對高性能、高效率的需求。因此,高效的調(diào)試(Debugging)手段在原型驗證中顯得尤為重要。今天,我們將探討設(shè)計調(diào)試的常見方法,涵蓋從簡單到復(fù)雜的多種調(diào)試。

1. 原型驗證為什么重要?隨著大規(guī)模集成電路設(shè)計復(fù)雜性的增加,芯片驗證面臨著巨大的資金和時間挑戰(zhàn)。早期開發(fā)者只能通過模擬或流片來驗證設(shè)計,耗時且成本高。原型驗證通過在流片前盡可能還原芯片的實際使用場景,確保功能模塊的可靠性和穩(wěn)定性,同時評估性能。這不僅能縮短芯片上市時間,還可以向客戶演示產(chǎn)品并提前預(yù)售。此外,原型驗證還可以顯著降低成本。在通過功能驗證后,原型驗證使得驅(qū)動開發(fā)能夠提前展開,無需等待芯片流片(Tape Out)。當(dāng)芯片回片后,應(yīng)用程序可以基于原型驗證時開發(fā)的驅(qū)動進(jìn)行簡單適配,迅速應(yīng)用于SoC上,進(jìn)一步縮短上市周期。

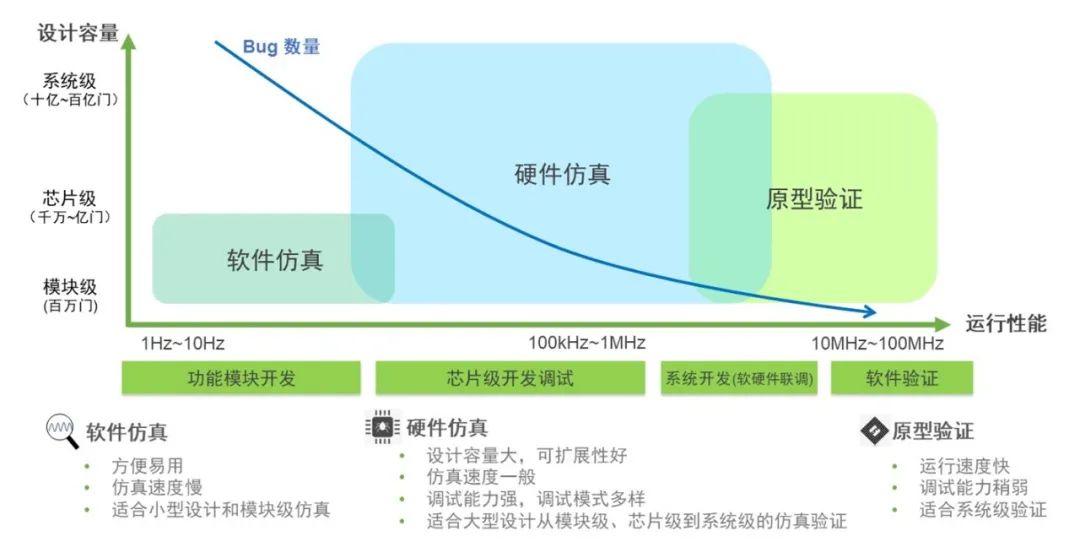

與軟件仿真和硬件仿真相比,原型驗證的最大優(yōu)勢在于其高性能。當(dāng)前有多種驗證方法可供選擇,如軟件仿真、硬件仿真和原型驗證。三者在芯片前端設(shè)計的功能驗證階段發(fā)揮著重要作用。相比之下,軟件仿真操作簡便,但速度較慢,適合小型設(shè)計和模塊級驗證;硬件仿真容量大,擴展性好,調(diào)試能力強,適合大型設(shè)計的模塊、芯片級和系統(tǒng)級驗證;而原型驗證則運行速度快,但調(diào)試能力相對較弱。如今許多用戶依賴FPGA芯片供應(yīng)商提供的調(diào)試工具,但這些調(diào)試手段相對單一且有限。接下來,我們將詳細(xì)介紹如何應(yīng)對這些調(diào)試挑戰(zhàn),并介紹思爾芯在這一領(lǐng)域的調(diào)試方案。

在調(diào)試與觀測工具方面,思爾芯的芯神瞳 Prodigy原型驗證解決方案就提供了全面且靈活的調(diào)試手段,配備了實時控制軟件(Player Pro-RunTime)、設(shè)計調(diào)試軟件(Player Pro-DebugTime)、深度調(diào)試套件 Multi-Debug Module(MDM)、協(xié)同仿真軟件ProtoBridge等完整工具鏈,極大提升了用戶效率。這些功能的增加主要是由于思爾芯面向廣泛的客戶需求,而這是其他廠商可能未能提供的。

2. 設(shè)計調(diào)試有哪些手段?

在原型驗證中,調(diào)試的核心任務(wù)是定位和解決設(shè)計中的故障,以確保系統(tǒng)功能的正確性。特別是在大規(guī)模復(fù)雜的SoC設(shè)計原型驗證過程中,工程師需要確保設(shè)計中的問題是可調(diào)試的,最大程度地減少開發(fā)過程中花費在調(diào)試上的時間。通常,用戶將設(shè)計下載到FPGA后,第一次運行時總會遇到各種失敗情況。這些失敗的原因可能是FPGA原型的網(wǎng)絡(luò)不正確、設(shè)計本身存在問題,或是設(shè)計在編譯過程中引入的錯誤(如由于設(shè)計分割和引腳復(fù)用引起的時序錯誤)。因此,開發(fā)人員需要有效的軟件調(diào)試和觀測工具,來確認(rèn)硬件是否正常運行,所有功能模塊是否按照預(yù)期工作,以快速定位和解決問題。這就需要借助外部邏輯分析儀或內(nèi)嵌邏輯分析儀來探測故障的根源。

目前,常見的設(shè)計調(diào)試手段包括:基本I/O、AXI總線事務(wù)、信號級調(diào)試以及基于協(xié)議的連接等。多數(shù)用戶還習(xí)慣于使用FPGA廠商提供的內(nèi)嵌邏輯分析儀,進(jìn)行原型驗證系統(tǒng)上板測試階段的調(diào)試。然而,這些工具在面對復(fù)雜的多FPGA設(shè)計,即大規(guī)模復(fù)雜設(shè)計時,可能會面臨資源消耗過大以及管理難度較高的問題。

思爾芯為工程師們提供了一套全面且靈活的調(diào)試解決方案,涵蓋從簡單到復(fù)雜的多種調(diào)試方法,滿足不同客戶在原型驗證中的多樣化需求,確保調(diào)試過程順利進(jìn)行。

- 基本I/O調(diào)試(Basic I/Os)

FPGA廠商在其軟件生態(tài)系統(tǒng)中也提供了多種信號級探測工具,常見的解決方案包括VIO IP核、信號源和探針編輯器,這些工具通常通過JTAG進(jìn)行監(jiān)控和驅(qū)動網(wǎng)絡(luò)。而思爾芯的I/O調(diào)試功能更加豐富,不僅在原型驗證系統(tǒng)上集成了多個基本的I/O接口,如按鍵、DIP開關(guān)、GPIO和UART等,使設(shè)計中的交互操作更加直觀便捷。此外,思爾芯的Player Pro軟件通過虛擬接口增強了遠(yuǎn)程診斷能力,使調(diào)試過程更加高效便捷。

- 總線事務(wù)調(diào)試(Bus Transaction Debugging)

在復(fù)雜SoC設(shè)計中,AXI總線事務(wù)調(diào)試是一種非常有效的手段,特別是在AXI已成為主流協(xié)議的設(shè)計中。思爾芯的ProtoBridge解決方案通過PCIe提供約4GB/s的高帶寬,實現(xiàn)AXI事務(wù)的高性能橋接。該解決方案包括一個AXI橋接的RTL接口,便于與測試設(shè)計連接,同時還提供PCIe設(shè)備驅(qū)動程序和API,支持開發(fā)基于軟件的激勵,很適合軟硬件協(xié)同開發(fā)。此外,思爾芯的原型驗證已內(nèi)建大約10Mbps的以太網(wǎng)調(diào)試,支持設(shè)計中存儲器映射AXI從設(shè)備的快速讀寫訪問,可以滿足低帶寬的AXI調(diào)試需求。

- 信號級調(diào)試(Signal Level Debugging)

信號級調(diào)試是原型驗證中最基礎(chǔ)且常用的調(diào)試方法,主要通過探測設(shè)計中的內(nèi)部信號來診斷問題。思爾芯的Player Pro軟件在此領(lǐng)域表現(xiàn)尤為出色,能夠幫助設(shè)計人員輕松將內(nèi)部信號引出并分配給I/O,從而更有效地進(jìn)行調(diào)試。思爾芯還提供了多種擴展卡,方便用戶進(jìn)行針腳連接、3.3V電壓轉(zhuǎn)換,此外還增加了額外的按鈕和開關(guān)接口以及外部邏輯分析儀的連接接口,進(jìn)一步提高了調(diào)試的靈活性和效率。

- 基于協(xié)議的調(diào)試(In-System Protocol Debugging)

當(dāng)FPGA原型與真實世界的數(shù)據(jù)進(jìn)行交互時,基于協(xié)議的調(diào)試尤為重要。思爾芯提供了超過90種現(xiàn)成的擴展卡和參考設(shè)計,幫助用戶實現(xiàn)多種協(xié)議的系統(tǒng)內(nèi)測試。如果用戶有更為特殊的需求,思爾芯還可以提供定制化的解決方案,以優(yōu)化系統(tǒng)級的測試和調(diào)試,確保用戶的原型驗證過程順利完成。

強大的調(diào)試工具包括邏輯分析儀、協(xié)議分析儀和實時監(jiān)控工具等。這些工具必須能夠與原型驗證平臺無縫集成,提供實時的調(diào)試信息和可視化的數(shù)據(jù)分析功能。此外,還需要支持遠(yuǎn)程調(diào)試,以便在不同地理位置的團隊之間進(jìn)行協(xié)作。主要挑戰(zhàn)在于如何在不影響系統(tǒng)性能的情況下,提供詳盡的調(diào)試信息,以及設(shè)計直觀高效的調(diào)試界面。確保這些工具能夠快速、準(zhǔn)確地反饋系統(tǒng)狀態(tài)和數(shù)據(jù),以便開發(fā)人員及時發(fā)現(xiàn)和解決潛在問題。通過這些多樣化的調(diào)試方法,思爾芯不僅幫助用戶在原型驗證中快速定位問題,還極大地提升了調(diào)試效率和系統(tǒng)穩(wěn)定性,確保設(shè)計能夠順利進(jìn)入下一個開發(fā)階段。

- 深度邏輯分析調(diào)試方案

FPGA廠商的嵌入式邏輯分析儀(如SignalTap和ChipScope)通常用于在FPGA的片上RAM塊中采樣和存儲信號,隨后通過JTAG讀取這些信號。目前,大多數(shù)用戶已經(jīng)習(xí)慣使用FPGA廠商提供的嵌入式邏輯分析儀(ILA)來進(jìn)行單顆FPGA的原型驗證系統(tǒng)調(diào)試。

然而,對于需要進(jìn)行深度調(diào)試或多FPGA級聯(lián)的用戶來說,常遇到的問題是需要更多內(nèi)存來存儲信號,以及跨FPGA的調(diào)試需求。由于FPGA內(nèi)部資源有限,且多FPGA級聯(lián)的原型驗證系統(tǒng)規(guī)模龐大,多個模塊通常分散在不同的FPGA中。此時就需要具備cross-trigger功能,即當(dāng)某顆FPGA中的調(diào)試模塊觸發(fā)時,能夠同時抓取多顆FPGA中的調(diào)試模塊的trace數(shù)據(jù)。一些FPGA廠商提供的ILA可以實現(xiàn)同一顆FPGA內(nèi)不同的時鐘域以及不同F(xiàn)PGA之間的ILA內(nèi)核的交叉觸發(fā)。

為了更好地支持多FPGA的信號級探測,思爾芯提供了多 FPGA 并發(fā)深度調(diào)試方案。最新的MDM Pro支持同時對多達(dá)8個FPGA進(jìn)行并發(fā)探測,并具備多FPGA觸發(fā)功能。MDM Pro配備了64GB的內(nèi)置DDR4內(nèi)存,能夠?qū)崿F(xiàn)深度信號跟蹤。它可以捕獲多達(dá)16K條信號,分為8組,每組包含2K個探針,而無需重新編譯FPGA。這一解決方案通過將MDM Pro預(yù)構(gòu)建到我們的Quad 10M和Quad 19P邏輯系統(tǒng)中,提升了生產(chǎn)力。MDM Pro的觸發(fā)設(shè)置設(shè)計直觀,且與FPGA廠商工具中的觸發(fā)設(shè)置非常相似,確保了工程師在使用時能夠順暢過渡。

MDM Pro具備靈活性,能夠適應(yīng)不同的設(shè)計流程偏好,支持IP模式和編譯模式兩種流程。在IP模式下,設(shè)計人員可以直接在RTL中實例化MDM客戶端,以連接他們希望捕獲的信號。或者,設(shè)計人員也可以通過編譯模式,使用Player Pro指定需要捕獲的信號,從而提供了一種高效且多樣化的調(diào)試方式

。3. 寫在最后

在芯片設(shè)計過程中,原型驗證在性能上顯著優(yōu)于軟件仿真和硬件仿真,盡管在可視性方面稍顯不足。這促使了商用原型驗證解決方案對高效調(diào)試手段的深度需求與重要性,以最大化原型驗證的優(yōu)勢。作為國內(nèi)最早推出原型驗證工具的EDA供應(yīng)商,思爾芯一直以來通過其全面且靈活的調(diào)試手段提升原型驗證的生產(chǎn)力和效率。由于在大規(guī)模復(fù)雜 SoC 設(shè)計原型驗證過程中,可用的可視性往往局限于單個FPGA,這使得跨多個FPGA映射的設(shè)計使調(diào)試可見性變得更加困難。思爾芯高效且多樣化的調(diào)試方式,適用于從簡單到復(fù)雜的多種應(yīng)用場景,尤其應(yīng)對多FPGA環(huán)境中的復(fù)雜挑戰(zhàn),并在工程師加速設(shè)計驗證和縮短上市時間方面發(fā)揮了關(guān)鍵作用。

-

芯片

+關(guān)注

關(guān)注

463文章

54267瀏覽量

468290 -

集成電路

+關(guān)注

關(guān)注

5461文章

12642瀏覽量

375403 -

soc

+關(guān)注

關(guān)注

40文章

4608瀏覽量

229919 -

驗證

+關(guān)注

關(guān)注

0文章

68瀏覽量

15743

發(fā)布評論請先 登錄

迅為iTOP-Hi3403開發(fā)板:解鎖多目拼接相機的10.4TOPS強“芯”動力,開啟4K智能視覺新紀(jì)元

【「龍芯之光 自主可控處理器設(shè)計解析」閱讀體驗】--LoongArch的SOC邏輯設(shè)計

Renesas FPB - RA2T1快速原型開發(fā)板:開啟高效設(shè)計之旅

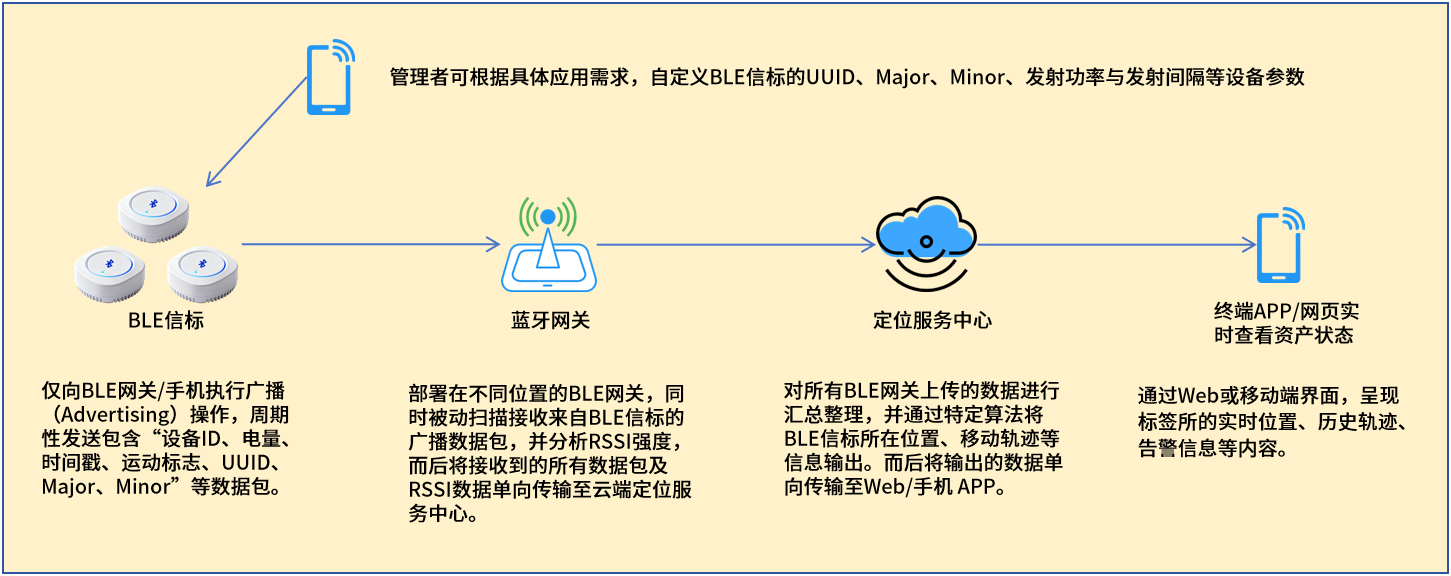

BLE SoC,如何助力管理者實現(xiàn)高效的資產(chǎn)追蹤?

基于DP1323EL的電動車解鎖方案:超高速讀寫,提升電動車一鍵解鎖體驗

FPGA原型驗證實戰(zhàn):如何應(yīng)對外設(shè)連接問題

如何使用CMSIS DAP仿真器調(diào)試,通過NucleiStudio調(diào)試蜂鳥SOC

【喜報】芯神瞳原型驗證解決方案榮膺工博會“集成電路創(chuàng)新成果獎”

MDD高效率整流管的調(diào)試與驗證建議

開芯院采用芯華章P2E硬件驗證平臺加速RISC-V驗證

Veloce Primo補全完整的SoC驗證環(huán)境

超大規(guī)模芯片驗證:基于AMD VP1902的S8-100原型驗證系統(tǒng)實測性能翻倍

泰芯半導(dǎo)體開啟AIOT高效傳輸新紀(jì)元

nRF54系列新一代無線 SoC

如何解決Air780EPM開發(fā)中的調(diào)試難題?深度解析高效調(diào)試方法

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗證之路

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗證之路

評論