總線時鐘周期與CPU時鐘周期是計算機(jī)體系結(jié)構(gòu)中兩個重要但有所區(qū)別的概念。為了深入探討它們之間的區(qū)別,本文將從定義、作用、關(guān)系、影響因素以及實際應(yīng)用等多個方面進(jìn)行詳細(xì)闡述。

一、定義

總線時鐘周期

總線時鐘周期,或稱總線周期,是指CPU通過外部總線對存儲器或I/O端口進(jìn)行一次完整的讀寫操作所需的時間。它是衡量總線數(shù)據(jù)傳輸效率的一個重要指標(biāo)。在總線周期中,CPU會按照預(yù)定的時序和協(xié)議與總線上的其他設(shè)備進(jìn)行數(shù)據(jù)交換。

CPU時鐘周期

CPU時鐘周期,或稱CPU主頻周期,是CPU內(nèi)部時鐘的一個脈沖時間,是CPU執(zhí)行一個基本操作(如讀取寄存器、執(zhí)行算術(shù)邏輯運(yùn)算等)所需的最短時間單位。CPU的時鐘頻率越高,時鐘周期就越短,CPU執(zhí)行指令的速度就越快。

二、作用

總線時鐘周期的作用

總線時鐘周期的作用主要體現(xiàn)在以下幾個方面:

- 數(shù)據(jù)傳輸 :在總線時鐘周期內(nèi),CPU通過總線與存儲器或I/O端口進(jìn)行數(shù)據(jù)交換。這是計算機(jī)內(nèi)部數(shù)據(jù)傳輸?shù)闹饕绞街弧?/li>

- 同步控制 :總線時鐘周期為總線上的數(shù)據(jù)傳輸提供了同步控制機(jī)制。通過時鐘信號的上升沿或下降沿來同步數(shù)據(jù)的發(fā)送和接收,確保數(shù)據(jù)傳輸?shù)臏?zhǔn)確性和穩(wěn)定性。

- 性能評估 :總線時鐘周期的長短可以反映總線的數(shù)據(jù)傳輸效率和性能。較短的總線時鐘周期意味著更高的數(shù)據(jù)傳輸速率和更低的延遲。

CPU時鐘周期的作用

CPU時鐘周期的作用則更加廣泛和核心:

- 指令執(zhí)行 :CPU按照時鐘周期的節(jié)奏執(zhí)行指令。每個時鐘周期內(nèi),CPU可以完成一個或多個基本操作,如讀取指令、執(zhí)行指令、存儲結(jié)果等。

- 性能基準(zhǔn) :CPU時鐘周期是評估CPU性能的重要基準(zhǔn)。主頻越高,時鐘周期越短,CPU的運(yùn)算速度和處理能力就越強(qiáng)。

- 系統(tǒng)同步 :CPU時鐘周期還決定了計算機(jī)系統(tǒng)的整體同步性。計算機(jī)內(nèi)部的各個部件(如內(nèi)存、I/O設(shè)備等)都需要在統(tǒng)一的時鐘信號控制下協(xié)調(diào)工作。

三、關(guān)系

總線時鐘周期與CPU時鐘周期之間存在一定的關(guān)系,但它們是兩個不同的概念,各自具有不同的作用和意義。

- 時間單位 :兩者都是時間單位,但衡量的對象和范圍不同。總線時鐘周期衡量的是總線數(shù)據(jù)傳輸?shù)臅r間,而CPU時鐘周期衡量的是CPU內(nèi)部操作的時間。

- 組成關(guān)系 :一個總線周期通常由若干個CPU時鐘周期組成。在總線周期內(nèi),CPU需要完成多個基本操作(如地址發(fā)送、數(shù)據(jù)發(fā)送/接收等),這些操作都需要在CPU時鐘周期的控制下完成。

- 相互依賴 :總線時鐘周期和CPU時鐘周期相互依賴、相互影響。總線數(shù)據(jù)傳輸?shù)男适艿紺PU時鐘周期長短的影響;同時,CPU執(zhí)行指令的速度也受到總線數(shù)據(jù)傳輸效率的限制。

四、影響因素

總線時鐘周期的影響因素

- 總線帶寬 :總線帶寬越寬,數(shù)據(jù)傳輸速率越高,總線時鐘周期可以相應(yīng)縮短。

- 總線協(xié)議 :不同的總線協(xié)議具有不同的數(shù)據(jù)傳輸機(jī)制和時序要求,這會影響總線時鐘周期的長短。

- 總線負(fù)載 :總線上的設(shè)備數(shù)量和數(shù)據(jù)傳輸量越大,總線負(fù)載越重,總線時鐘周期可能會相應(yīng)延長。

CPU時鐘周期的影響因素

- CPU主頻 :CPU主頻越高,時鐘周期越短。主頻是決定CPU時鐘周期長短的關(guān)鍵因素。

- CPU架構(gòu) :不同的CPU架構(gòu)具有不同的指令集和內(nèi)部操作機(jī)制,這會影響CPU執(zhí)行指令的速度和效率。

- 制造工藝 :制造工藝的改進(jìn)可以提高CPU的集成度和性能,從而縮短時鐘周期。

五、實際應(yīng)用

在實際應(yīng)用中,總線時鐘周期與CPU時鐘周期的關(guān)系對于計算機(jī)系統(tǒng)的整體性能具有重要影響。

- 系統(tǒng)優(yōu)化 :在系統(tǒng)設(shè)計時,需要根據(jù)實際需求合理選擇總線類型和CPU型號,以優(yōu)化總線時鐘周期和CPU時鐘周期之間的關(guān)系。通過提高總線帶寬、優(yōu)化總線協(xié)議和降低總線負(fù)載等方式來縮短總線時鐘周期;同時,通過提高CPU主頻、改進(jìn)CPU架構(gòu)和制造工藝等方式來縮短CPU時鐘周期。

- 性能評估 :在性能評估時,需要綜合考慮總線時鐘周期和CPU時鐘周期的影響。通過測量總線數(shù)據(jù)傳輸速率和CPU執(zhí)行指令的速度來評估計算機(jī)系統(tǒng)的整體性能。同時,還需要關(guān)注系統(tǒng)穩(wěn)定性、功耗和散熱等方面的性能表現(xiàn)。

- 未來發(fā)展 :隨著計算機(jī)技術(shù)的不斷發(fā)展,總線技術(shù)和CPU技術(shù)也在不斷進(jìn)步。未來的總線將具有更高的帶寬和更低的延遲;未來的CPU將具有更高的主頻和更強(qiáng)的處理能力。這將進(jìn)一步縮短總線時鐘周期和CPU時鐘周期,提高計算機(jī)系統(tǒng)的整體性能。

六、總結(jié)

總線時鐘周期與CPU時鐘周期是計算機(jī)體系結(jié)構(gòu)中兩個重要但有所區(qū)別的概念。它們分別衡量了總線數(shù)據(jù)傳輸和CPU內(nèi)部操作的時間單位。在實際應(yīng)用中,需要綜合考慮兩者之間的關(guān)系和影響因素來優(yōu)化計算機(jī)系統(tǒng)的整體性能。通過不斷的技術(shù)創(chuàng)新和系統(tǒng)優(yōu)化,可以進(jìn)一步縮短總線時鐘周期和CPU時鐘周期,提高計算機(jī)系統(tǒng)的運(yùn)算速度和處理能力。

-

cpu

+關(guān)注

關(guān)注

68文章

11279瀏覽量

224978 -

總線

+關(guān)注

關(guān)注

10文章

3040瀏覽量

91660 -

時鐘周期

+關(guān)注

關(guān)注

0文章

18瀏覽量

12595

發(fā)布評論請先 登錄

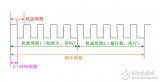

詳細(xì)解讀|時鐘周期、機(jī)器周期、指令周期、總線周期

msp430時鐘周期、機(jī)器周期、指令周期定義及關(guān)系

什么是時鐘周期_時鐘周期怎么算

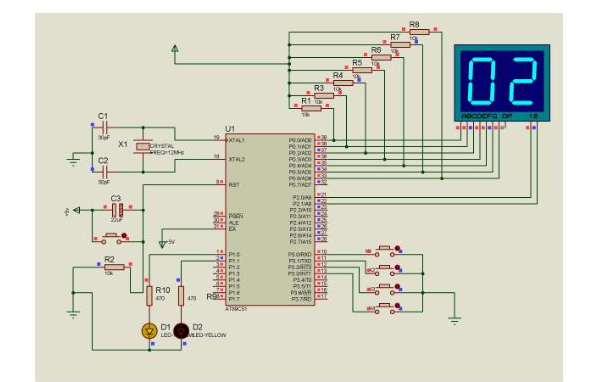

單片機(jī)的時鐘周期和機(jī)器周期與指令周期到底有什么區(qū)別

51/時鐘周期、時鐘頻率、狀態(tài)周期、機(jī)器周期

C51單片機(jī)晶振頻率、時鐘周期、狀態(tài)周期、機(jī)器周期、指令周期和總線周期的關(guān)系

振蕩周期、時鐘周期、機(jī)器周期、指令周期的區(qū)別與聯(lián)系

總線時鐘周期與CPU時鐘周期的區(qū)別

總線時鐘周期與CPU時鐘周期的區(qū)別

評論