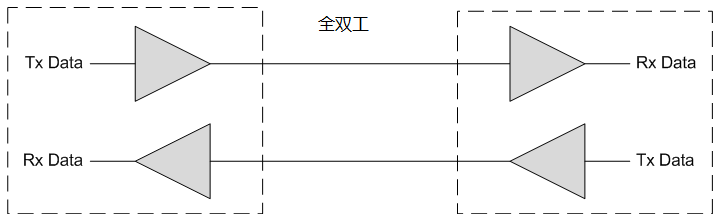

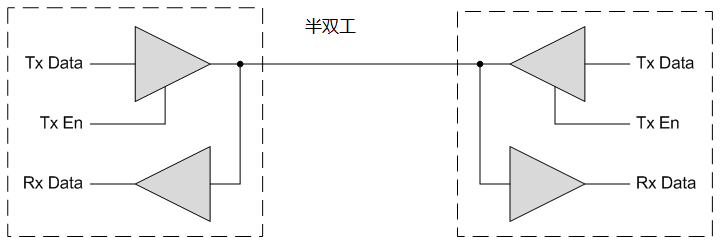

典型的全雙工(Full Duplex)系統(tǒng)如下圖所示,芯片1和芯片2之間有彼此獨立的數(shù)據(jù)傳輸線,這意味著芯片1和芯片2可以同時給對方發(fā)送數(shù)據(jù)而不會發(fā)生沖突。SPI/UART采用的就是全雙工通信方式。半雙工系統(tǒng)則不同,芯片1和芯片2之間只有一條專用的且被彼此共享的數(shù)據(jù)傳輸線。這就要求芯片1和芯片2必須協(xié)商好,當(dāng)前誰發(fā)送數(shù)據(jù),誰接收數(shù)據(jù)。如果兩者同時發(fā)送數(shù)據(jù)就會導(dǎo)致發(fā)送沖突,從而造成數(shù)據(jù)丟失。I2C采用的就是半雙工通信方式。

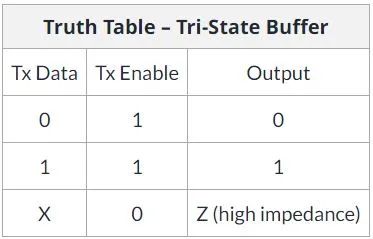

在上面兩張圖片中,其中的三角形代表輸入/輸出緩沖器(IBUF/OBUF),在半雙工系統(tǒng)中,多了一個控制信號TxEn,該信號控制的是三態(tài)緩沖器。這里我們先看一下三態(tài)緩沖器的真值表,如下圖所示。可以看到TxEn為1時三態(tài)緩沖器輸出等于輸入,為0時,輸出為高阻。當(dāng)芯片1和芯片2的TxEn均為高時,兩者均會驅(qū)動數(shù)據(jù)傳輸線發(fā)送數(shù)據(jù),造成沖突。這在半雙工系統(tǒng)中是一定要避免的。

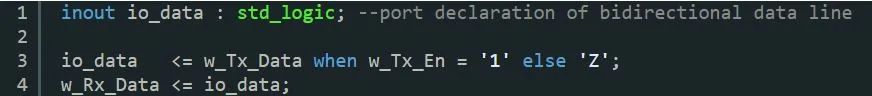

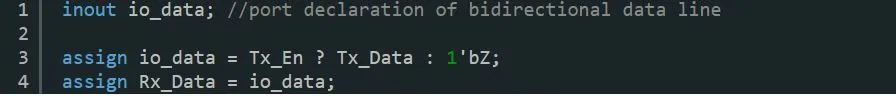

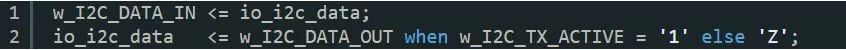

無論是VHDL還是Verilog/SystemVerilog,都提供了相應(yīng)的語句描述三態(tài)緩沖器,而綜合工具也可將其正確地推斷出來。下面給出了三態(tài)緩沖器對應(yīng)的VHDL代碼和Verilog代碼。其中io_data被聲明為雙向信號。需要注意的是盡管VHDL不區(qū)分大小寫,但高阻態(tài)則必須用大寫Z來表示,Verilog中大小寫均可。

VHDL代碼

Verilog/SystemVerilog代碼

當(dāng)前主流的FPGA結(jié)構(gòu)中,三態(tài)緩沖器只存在于IOB(Input/Output Block)中。因此,對應(yīng)的雙向IO一定要放在設(shè)計的頂層、。如果在子模塊中使用了三態(tài)緩沖器,如下圖的I2C子模塊,因為綜合工具判斷其出現(xiàn)在子模塊中,所以會將三態(tài)緩沖器移除使其成為普通輸出,從而造成功能錯誤。

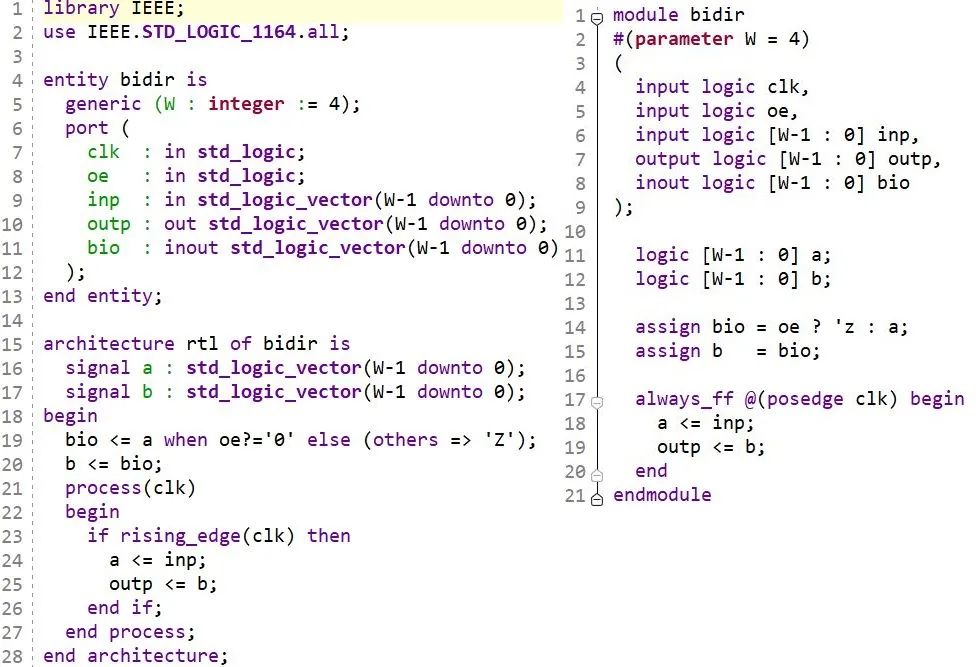

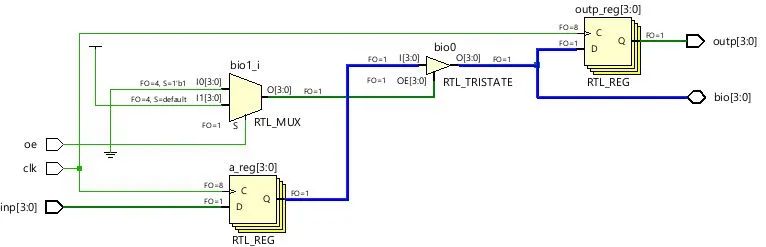

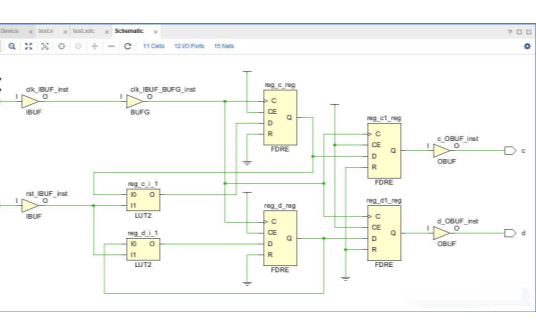

我們看一個案例,相應(yīng)的VHDL代碼和SystemVerilog代碼如下圖所示。雙向端口bio均通過關(guān)鍵字inout定義。bio作為輸入時和信號b相關(guān),作為輸出時和信號a相關(guān)。信號a由寄存器輸出,信號b連接輸出寄存器的輸入端。這兩組寄存器都可以放置在IOB內(nèi)。

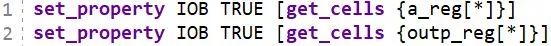

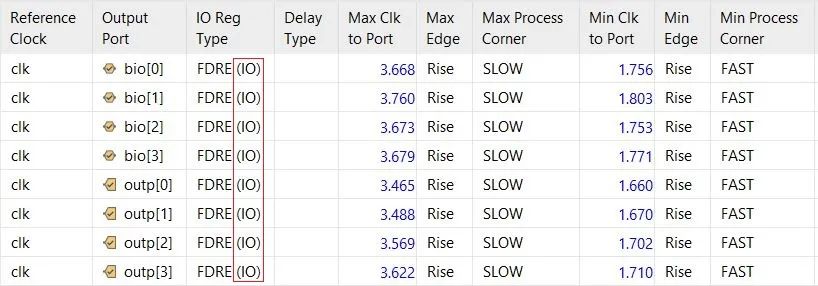

通過如下圖所示約束可將這兩組寄存器放置在IOB內(nèi),這里屬性IOB的作用對象是通過命令get_cells獲取的寄存器對象。通過命令report_datasheet可查看是否放置成功。如顯示FDRE(IO)則說明該寄存器在IOB內(nèi)。

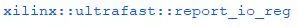

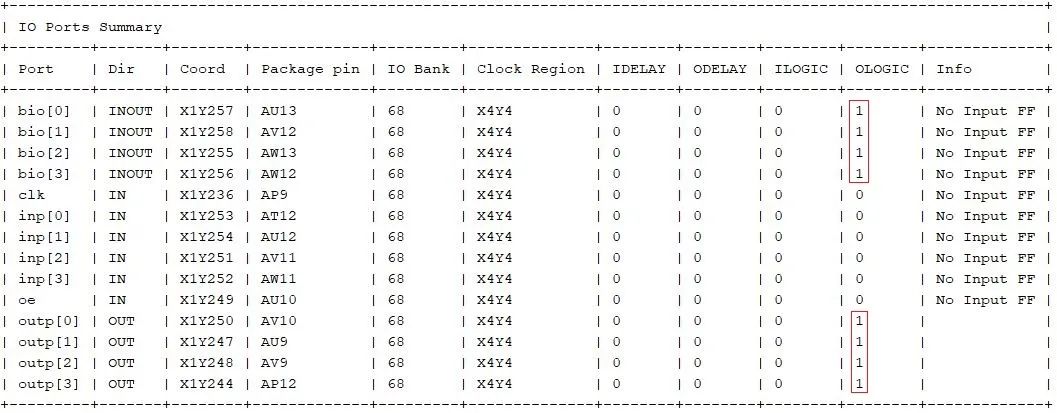

也可以通過report_io_reg查看寄存器是否在IOB內(nèi)。

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636318 -

芯片

+關(guān)注

關(guān)注

463文章

54010瀏覽量

466072 -

緩沖器

+關(guān)注

關(guān)注

6文章

2227瀏覽量

48882 -

Verilog

+關(guān)注

關(guān)注

30文章

1374瀏覽量

114526

原文標(biāo)題:雙向IO與IOB

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

FPGA中雙向端口IO的研究

無法將符號組合到單個IOB中

DCM/IOB不合適

請問我還有別的辦法實現(xiàn)雙向IO嗎?

IOB / BUFGCTRL時鐘元件對發(fā)生錯誤

不兼容的IOB被鎖定到同一個銀行11沖突的IO標(biāo)準(zhǔn)是什么

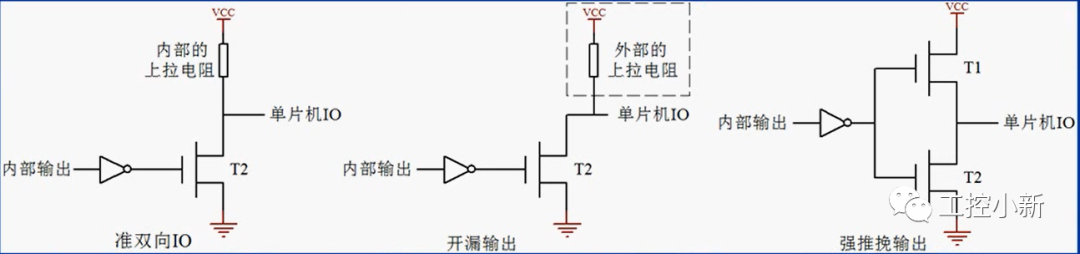

stm32單片機(jī)準(zhǔn)雙向IO口配置介紹

一文詳解Spartan-6系列IO Tile結(jié)構(gòu)

《Linux設(shè)備驅(qū)動開發(fā)詳解》第8章、Linux設(shè)備驅(qū)動中的阻塞與非阻塞IO

FPGA中IOB寄存器的使用教程詳細(xì)說明

FPGA中IOB寄存器的使用心得

xilinx FPGA的IOB使用教程說明

關(guān)于stm32單片機(jī)準(zhǔn)雙向IO口配置

xilinx FPGA IOB約束使用以及注意事項

雙向IO與IOB詳解

雙向IO與IOB詳解

評論