在Altium Designer(簡(jiǎn)稱(chēng)AD)中,將原理圖畫(huà)好后生成PCB(Printed Circuit Board,印制電路板)是一個(gè)重要的設(shè)計(jì)流程。這個(gè)過(guò)程涉及從邏輯設(shè)計(jì)到物理布局的轉(zhuǎn)變,需要仔細(xì)規(guī)劃和執(zhí)行。以下是將原理圖畫(huà)好后生成PCB的步驟,包括每個(gè)步驟的具體操作和注意事項(xiàng)。

一、準(zhǔn)備階段

1. 創(chuàng)建項(xiàng)目和原理圖

- 打開(kāi)AD并創(chuàng)建新項(xiàng)目 :首先,啟動(dòng)Altium Designer軟件,點(diǎn)擊“文件”>“新建”>“項(xiàng)目”,創(chuàng)建一個(gè)新的項(xiàng)目文件。為項(xiàng)目命名并選擇一個(gè)合適的保存位置。

- 添加原理圖文件 :在項(xiàng)目下,點(diǎn)擊“文件”>“新建”>“原理圖”,創(chuàng)建一個(gè)新的原理圖文件。同樣,為原理圖命名并保存。

2. 設(shè)計(jì)原理圖

- 放置元件 :在原理圖編輯器中,使用工具欄上的元件放置工具,從元件庫(kù)中選取所需的元件并放置到原理圖上。確保元件的型號(hào)、參數(shù)等信息準(zhǔn)確無(wú)誤。

- 連接元件 :使用連線工具或網(wǎng)絡(luò)標(biāo)簽,將元件之間的引腳連接起來(lái),形成完整的電路圖。注意檢查連接的正確性和完整性。

3. 編譯原理圖

- 編譯檢查 :完成原理圖設(shè)計(jì)后,點(diǎn)擊工具欄上的“編譯”按鈕或選擇“項(xiàng)目”>“編譯項(xiàng)目”進(jìn)行編譯檢查。這一步將檢查原理圖中是否存在錯(cuò)誤或警告,如元件未連接、引腳號(hào)不匹配等。

- 修正錯(cuò)誤 :根據(jù)編譯結(jié)果中的錯(cuò)誤和警告信息,回到原理圖編輯器中修正相應(yīng)的問(wèn)題。確保原理圖在邏輯上是正確的。

二、準(zhǔn)備PCB轉(zhuǎn)換

1. 為元件分配封裝

- 查看元件封裝 :在原理圖編輯器中,雙擊某個(gè)元件以打開(kāi)其屬性對(duì)話框。在“封裝”選項(xiàng)卡中查看該元件的封裝信息。如果封裝信息不正確或缺失,需要為其分配正確的封裝。

- 分配封裝 :如果元件的封裝信息不正確或缺失,可以通過(guò)點(diǎn)擊“瀏覽”按鈕從封裝庫(kù)中選擇合適的封裝進(jìn)行分配。確保為所有元件都分配了正確的封裝。

2. 創(chuàng)建PCB文件

- 新建PCB文件 :在項(xiàng)目下,點(diǎn)擊“文件”>“新建”>“PCB文件”,創(chuàng)建一個(gè)新的PCB文件。為PCB文件命名并保存。

三、轉(zhuǎn)換到PCB

1. 更新PCB文件

- 選擇更新PCB :在原理圖編輯器中,點(diǎn)擊菜單欄上的“設(shè)計(jì)”>“更新PCB文檔...”選項(xiàng)。這將打開(kāi)一個(gè)對(duì)話框,顯示當(dāng)前項(xiàng)目中的PCB文件列表。

- 執(zhí)行更新 :在對(duì)話框中,選擇要更新的PCB文件并點(diǎn)擊“執(zhí)行更改”按鈕。AD將開(kāi)始將原理圖中的元件和連接信息導(dǎo)入到PCB文件中。

2. 檢查導(dǎo)入結(jié)果

- 查看導(dǎo)入狀態(tài) :在更新過(guò)程中,注意觀察導(dǎo)入狀態(tài)窗口中的信息。如果出現(xiàn)錯(cuò)誤或警告,需要根據(jù)提示回到原理圖編輯器中進(jìn)行修正。

- 驗(yàn)證導(dǎo)入結(jié)果 :更新完成后,在PCB編輯器中打開(kāi)PCB文件,檢查所有元件是否都已正確導(dǎo)入并放置在PCB板上。同時(shí)檢查連接是否保持與原理圖一致。

四、PCB設(shè)計(jì)

1. 元件布局

- 規(guī)劃布局 :在PCB編輯器中,根據(jù)電路的功能和性能要求,合理規(guī)劃元件的布局。注意將高頻元件和低頻元件分開(kāi)放置,以減少相互干擾。

- 放置元件 :使用工具欄上的元件放置工具,在PCB板上放置元件。注意保持元件之間的距離符合設(shè)計(jì)規(guī)則的要求,并盡量使布局緊湊有序。

2. 布線

- 設(shè)置布線規(guī)則 :在PCB編輯器中,設(shè)置合適的布線規(guī)則以確保布線的質(zhì)量和可靠性。這些規(guī)則包括線寬、線間距、過(guò)孔大小等參數(shù)。

- 開(kāi)始布線 :使用布線工具在元件之間繪制導(dǎo)線以形成電路連接。在布線過(guò)程中要注意信號(hào)的完整性和電磁兼容性等問(wèn)題。

- 優(yōu)化布線 :完成初步布線后,使用AD提供的布線優(yōu)化工具對(duì)布線進(jìn)行優(yōu)化處理以改善布線的質(zhì)量和美觀度。

五、檢查和優(yōu)化

1. DRC檢查

- 運(yùn)行DRC檢查 :在PCB編輯器中,點(diǎn)擊工具欄上的“DRC檢查”按鈕或選擇“工具”>“設(shè)計(jì)規(guī)則檢查”來(lái)運(yùn)行DRC檢查。這將檢查PCB設(shè)計(jì)是否符合所有的設(shè)計(jì)規(guī)則要求。

- 修正問(wèn)題 :根據(jù)DRC檢查結(jié)果中的錯(cuò)誤和警告信息回到PCB編輯器中進(jìn)行修正處理。確保所有問(wèn)題都得到解決并滿(mǎn)足設(shè)計(jì)要求。

2. 優(yōu)化設(shè)計(jì)

- 調(diào)整布局和布線 :根據(jù)DRC檢查結(jié)果和實(shí)際需求對(duì)PCB的布局和布線進(jìn)行調(diào)整和優(yōu)化處理。以提高電路的性能和可靠性為目標(biāo)進(jìn)行持續(xù)改進(jìn)。

- 審查設(shè)計(jì) :最后對(duì)整個(gè)PCB設(shè)計(jì)進(jìn)行審查以確認(rèn)其滿(mǎn)足所有設(shè)計(jì)要求并具備良好的可制造性和可測(cè)試性等特點(diǎn)。

六、導(dǎo)出和制造

- 導(dǎo)出PCB文件 :完成PCB設(shè)計(jì)后,可以將PCB文件導(dǎo)出為制造商所需的格式(如Gerber文件)以便進(jìn)行制造加工。

- 制造PCB :將導(dǎo)出的PCB文件發(fā)送給制造商進(jìn)行制造加工。制造商將根據(jù)文件內(nèi)容制作實(shí)際的PCB板以供后續(xù)組裝和測(cè)試使用。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

pcb

+關(guān)注

關(guān)注

4404文章

23878瀏覽量

424303 -

印制電路板

+關(guān)注

關(guān)注

14文章

975瀏覽量

43127 -

AD

+關(guān)注

關(guān)注

28文章

879瀏覽量

154900 -

元件

+關(guān)注

關(guān)注

4文章

1217瀏覽量

38738

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

PROTEL中怎么把幾張原理圖畫(huà)成一個(gè)PCB

我看人家一塊板的原理圖都是好幾張,PROTEL中怎么把幾張原理圖畫(huà)成一個(gè)PCB呀求大蝦幫忙 不勝感激

發(fā)表于 10-24 15:14

原理圖生成pcb部分飛線沒(méi)有是怎么回事?

Altium中原理圖生成pcb后,pcb中不能顯示芯片與其他元器件的飛線(芯片是自己繪制的封裝),試過(guò)了connections show all,但還是沒(méi)有飛線,求詳細(xì)解釋?zhuān)〖保?/div>

發(fā)表于 03-01 07:42

求解答:用multisim畫(huà)好原理圖生成protel PCB網(wǎng)絡(luò)表時(shí)出現(xiàn)的...

用multisim畫(huà)好原理圖生成protelPCB網(wǎng)絡(luò)表,由于在multisim中芯片的電源和接地都是默認(rèn)的,在導(dǎo)入網(wǎng)絡(luò)表時(shí)出現(xiàn)錯(cuò)誤,怎么解決這樣的問(wèn)題呢?

發(fā)表于 06-20 22:47

為什么沒(méi)有生成PCB的選項(xiàng)了?

本帖最后由 WAITXHURT 于 2012-12-31 11:30 編輯

原理圖畫(huà)好后,發(fā)現(xiàn)沒(méi)有生成PCB的選項(xiàng)了,文件下拉菜單連輸出也沒(méi)有了,怎么解決啊?

發(fā)表于 09-03 12:48

原理圖畫(huà)完了一定要生成網(wǎng)絡(luò)表么

現(xiàn)在剛開(kāi)始學(xué)protel99 慢慢畫(huà)好了原理圖 能不能不生成網(wǎng)絡(luò)表呢 這網(wǎng)絡(luò)表是干什么用的啊

發(fā)表于 08-07 16:03

在畫(huà)好原理圖生成PCB圖的時(shí)候出現(xiàn)了這種問(wèn)題求各位大神指教一下?

我在畫(huà)好原理圖生成PCB圖的時(shí)候出現(xiàn)了這種問(wèn)題求各位大神指教一下?急急急!!!

發(fā)表于 07-29 12:09

AD10畫(huà)雙運(yùn)放原理圖生成PCB

`像這樣我在原理圖畫(huà)一個(gè)5532的雙運(yùn)放 然后生成PCB怎么到了PCB這就成了兩個(gè)5532了呢 ?`

發(fā)表于 04-23 00:57

畫(huà)好pcb原理圖和封裝以后,生成pcb出現(xiàn)下圖錯(cuò)誤

請(qǐng)問(wèn)畫(huà)好pcb原理圖和封裝以后,生成pcb為什么會(huì)是這種錯(cuò)誤

發(fā)表于 05-28 00:05

怎么解決生成PCB后引腳變綠問(wèn)題?

本人想畫(huà)一個(gè)32最小系統(tǒng)圖,原理圖畫(huà)好,生成PCB后,引腳變綠了,如圖,修改規(guī)則組焊層間距為0也還是不行,該怎么設(shè)置才行

發(fā)表于 07-12 00:23

Pspice的DSN仿真原理圖畫(huà)好了,需要插入以下 字符到原理圖中,該如何操作? 請(qǐng)大佬指點(diǎn)

Pspice的DSN仿真原理圖畫(huà)好了,需要插入以下 字符到原理圖中,該如何操作? 請(qǐng)大佬指點(diǎn)迷津

*@PSpice: ** [@pspice](https://www.eda365.com

發(fā)表于 06-15 22:15

PCB1.~(10).PcbDoc_畫(huà)好的原理圖及其pcb布圖

ad制圖。畫(huà)好的原理圖及其pcb布圖。很好的展示了pcb線路繪制。單層板

發(fā)表于 10-30 13:41

?38次下載

如何用altium_designer_09_把已畫(huà)好的原理圖_自動(dòng)生成pcb

如何用altium_designer_09_把已畫(huà)好的原題圖_自動(dòng)生成pcb

發(fā)表于 11-20 11:31

?81次下載

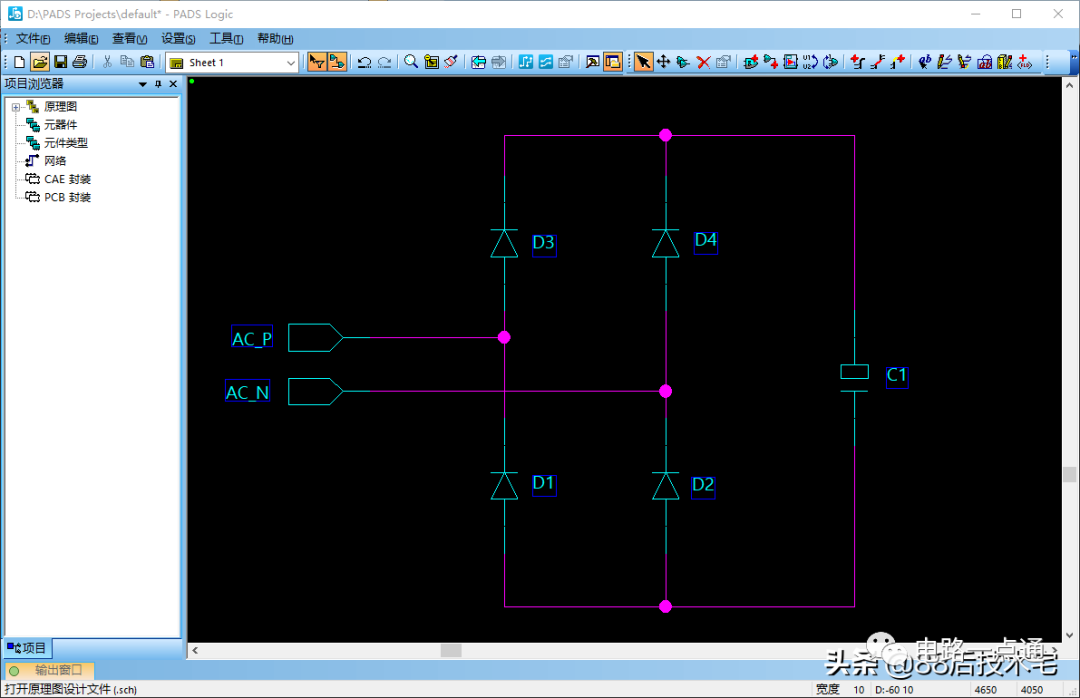

PADS原理圖怎么導(dǎo)入PCB PADS從原理圖到PCB設(shè)計(jì)項(xiàng)目的基本流程

AltiumDesigner不需要網(wǎng)表導(dǎo)入導(dǎo)出這一操作,原理圖畫(huà)好后直接轉(zhuǎn)入PCB非常方便。PADS就麻煩些,需要從原理圖導(dǎo)出網(wǎng)表和PCB里導(dǎo)入網(wǎng)表。這也是許多從AD轉(zhuǎn)PADS覺(jué)得不適

ad中原理圖畫(huà)好如何生成pcb

ad中原理圖畫(huà)好如何生成pcb

評(píng)論