我們以T20F256為例來做一個實驗。

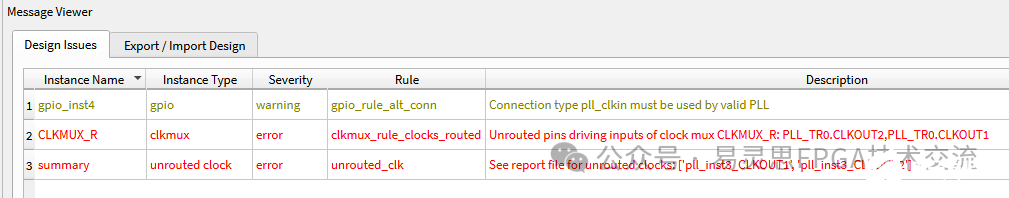

我們把T20F256的5個PLL全部打開,每個PLL的三路輸出也全面打開。在生成約束時會報以下錯。

Unrouted pins driving inputs of clock muxCLKMUX_R:PLL_TR0.CLKOUT2,PLL_TR0.CLKOUT1.

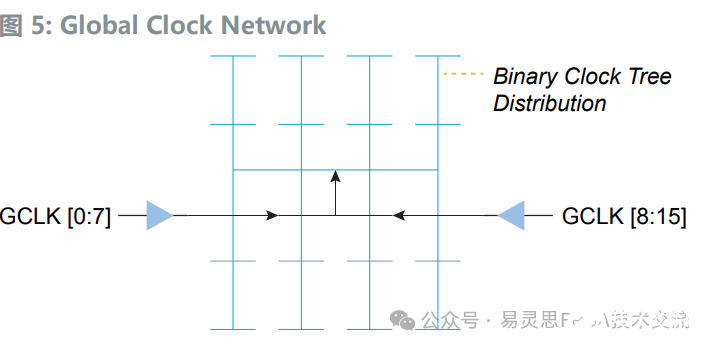

在T20中有16個全局時鐘網(wǎng)絡(luò)GCLK。在芯片的左右兩側(cè)各8個。全局時鐘管腳或者PLL的輸出時鐘通過左右兩個CLKMUX上全局網(wǎng)絡(luò)。左側(cè)的PLL(包括PLL_TL0和PLL_TL1)上左側(cè)的CLKMUX_L;右側(cè)的PLL(包括PLL_TR0,PLL_TR1和PLLBR0)上右側(cè)的CLKMUX_R。

當兩側(cè)要上全局時鐘網(wǎng)絡(luò)的時鐘超過8個時就會報錯。

拿上面的例子來分析報“Unrouted pins driving inputs of clock muxCLKMUX_R:PLL_TR0.CLKOUT2,PLL_TR0.CLKOUT1"錯誤的原因。

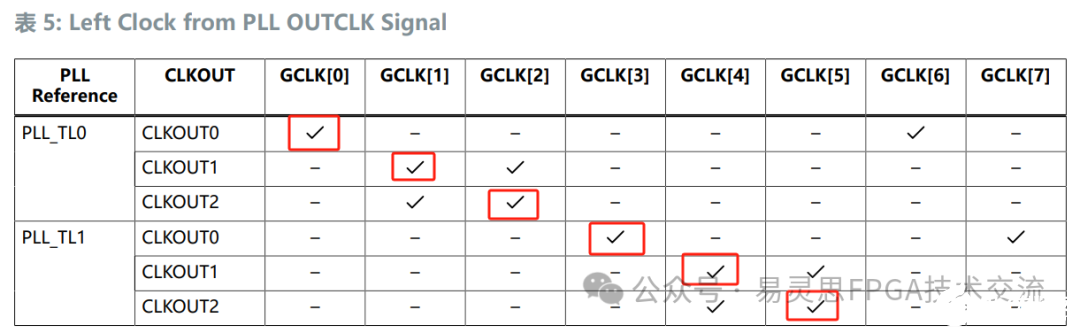

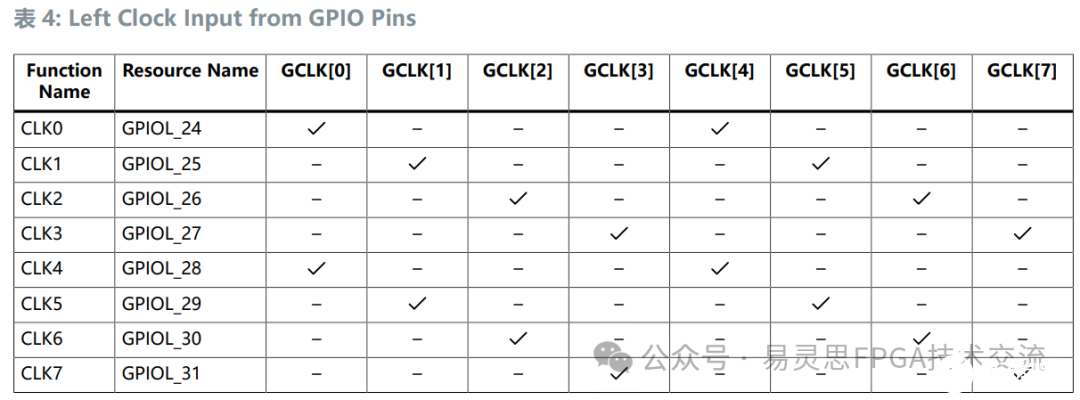

當我們把所有PLL及其輸出都打開后,先來分析左側(cè)的CLKMUX_L的使用情況。如下圖左側(cè)的GCLK的編號為0~7。而PLL_TL0和PLL_TL1只有6個時鐘,那么按紅色標注,PLL_TL0.CLKOUT0上GCLK0;PLL_TL0.CLKOUT1上GCLK1;PLL_TL0.CLKOUT2上GCLK2...,按紅色的標記是每個時鐘都會有GCLK可以走的。

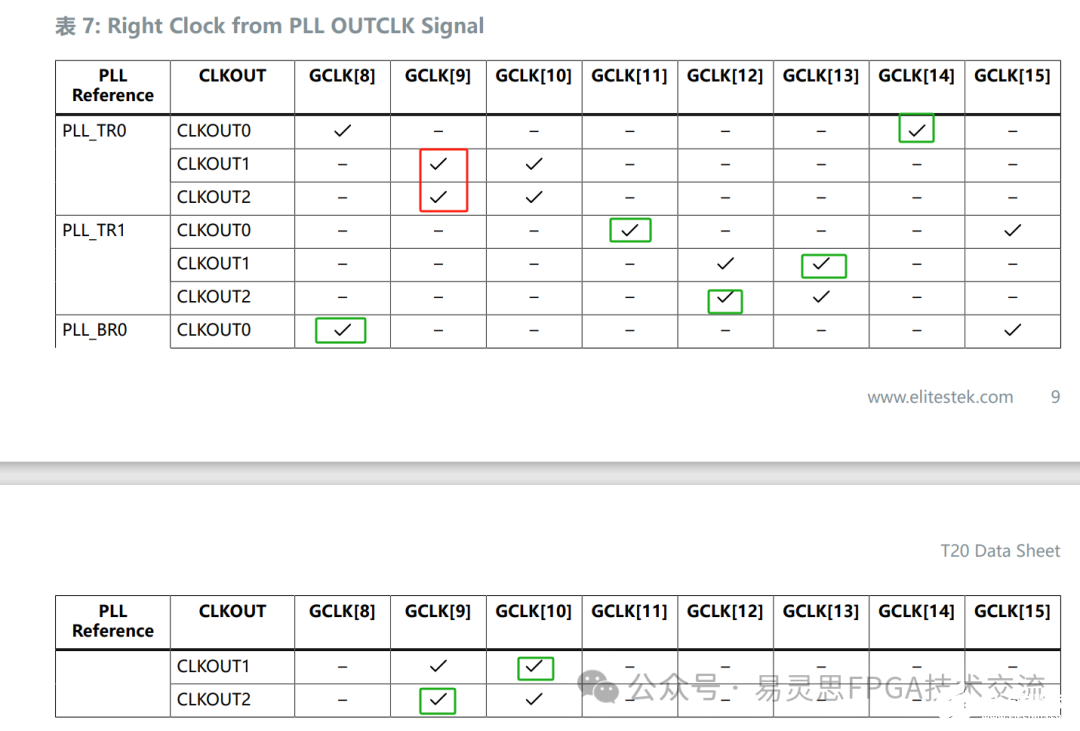

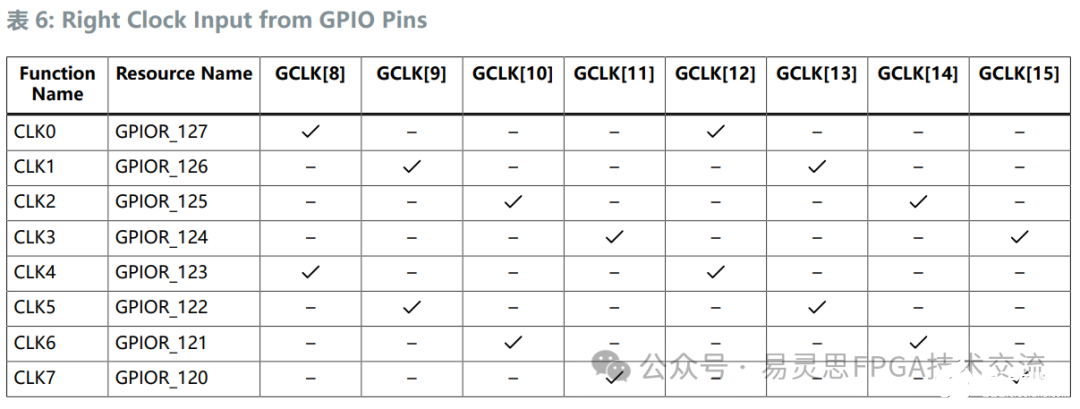

同樣的,當我們把所有PLL及其輸出都打開后,先來分析右側(cè)的CLKMUX_L的使用情況。如下圖左側(cè)的GCLK的編號為8~15。右側(cè)有三個PLL分別為PLL_TR0,PLL_TR1和PLLBR0。按綠色框分配之后,PLL_TR0的CLKOUT1和2是沒有網(wǎng)絡(luò)可以走的。雖然它們可以走GCLK9和GCLK10,但是這兩個網(wǎng)絡(luò)已經(jīng)被PLL_BR0的CLKOUT1和2占用了。所以就會報出上面的負錯誤。

可能有人會問。為什么GCLK15及GCLK6,GCLK7都沒有用到呢。這是因為我們這里只談到了PLL的輸出時鐘,另外還有沒有專用時鐘管腳沒有考慮。如下圖。

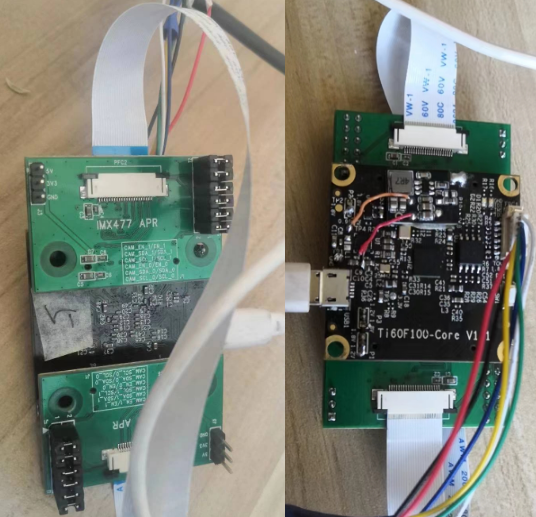

鈦金系列的器件也有相似的問題。具體大家可以先看下時鐘網(wǎng)線的說明。

-

時鐘網(wǎng)絡(luò)

+關(guān)注

關(guān)注

0文章

16瀏覽量

6702 -

易靈思

+關(guān)注

關(guān)注

6文章

64瀏覽量

5541

發(fā)布評論請先 登錄

易靈思推Trion Titanium FPGA,采用 “Quantum? 計算架構(gòu)”

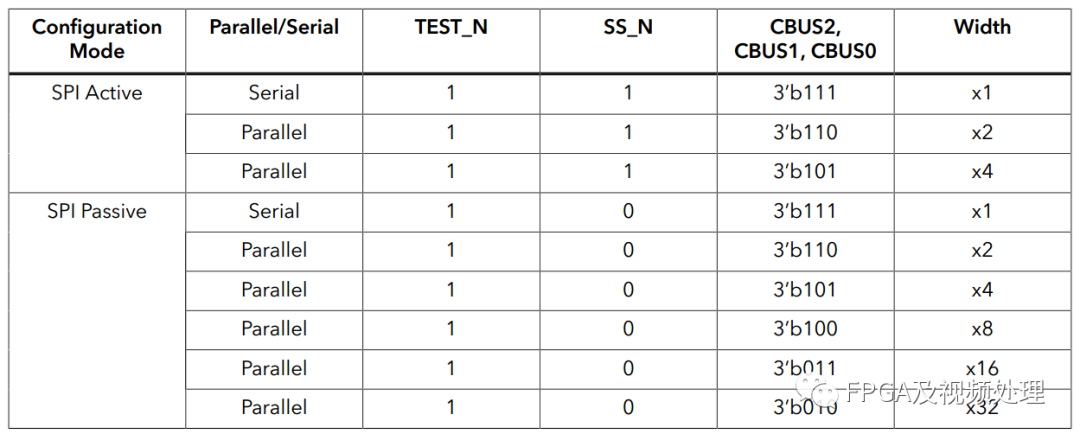

易靈思Programmer工具的配置模式過程分析

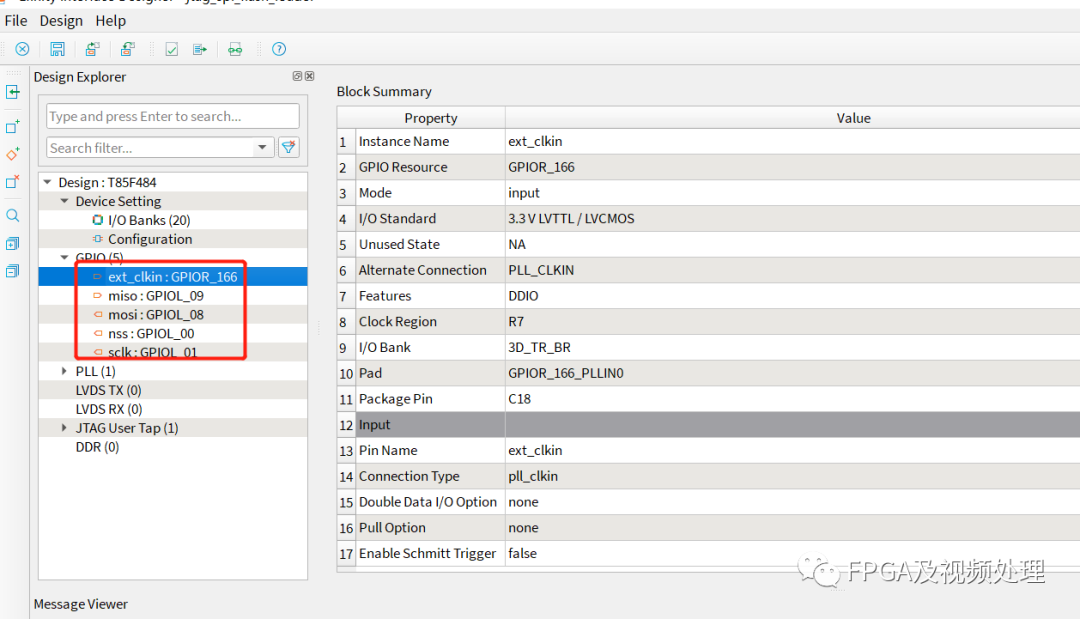

易靈思JTAG寫入Flash工程的創(chuàng)建過程和燒寫操作

易靈思FPGA產(chǎn)品幫助安防領(lǐng)域創(chuàng)新和突破

易靈思MIPI CSI自環(huán)調(diào)試步驟

易靈思FPGA之---國產(chǎn)化替代選型策略

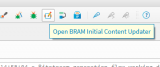

易靈思IDE更新ROM可以不用全編譯了

易靈思FPGA軟件更新的節(jié)奏,也許能磨出一個好產(chǎn)品

易靈思RAM使用--Update3

易靈思FPGA產(chǎn)品的主要特點

易靈思的時鐘網(wǎng)絡(luò)問題

易靈思的時鐘網(wǎng)絡(luò)問題

評論