CMOS的工作原理

CMOS(互補金屬氧化物半導體)是一種廣泛使用的半導體技術,用于構建集成電路和各種電子設備。CMOS技術的核心在于它使用互補的p型和n型MOSFET(金屬氧化物半導體場效應晶體管)來構建邏輯門和其他電子電路。

CMOS的基本結構

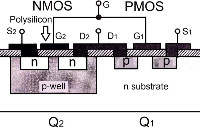

CMOS由p型MOSFET(p-MOSFET)和n型MOSFET(n-MOSFET)組成。這兩種晶體管在結構上互補,能夠共同工作以實現邏輯功能。

- p-MOSFET :p-MOSFET的源極和漏極摻雜有p型材料,柵極通過一個絕緣層與硅基底隔離。當在柵極上施加正電壓時,會在柵極下方形成一個反型通道(n型通道),允許電流從源極流向漏極。

- n-MOSFET :n-MOSFET的源極和漏極摻雜有n型材料。當在柵極上施加負電壓時,會在柵極下方形成一個反型通道(p型通道),允許電流從源極流向漏極。

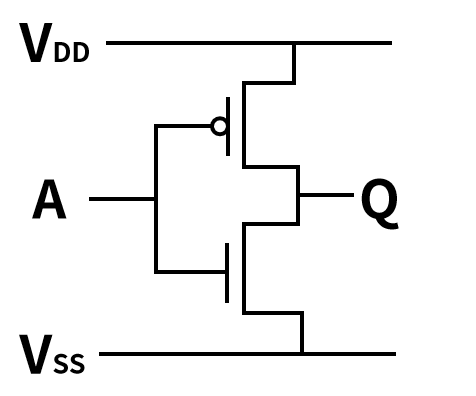

CMOS邏輯門

CMOS邏輯門,如CMOS反相器(NOT門),是最簡單的CMOS邏輯電路之一。它由一個p-MOSFET和一個n-MOSFET并聯組成,兩個晶體管的源極分別接電源的正負極,柵極共同接收輸入信號,漏極共同輸出。

- 工作過程 :

- 當輸入為低電平時,n-MOSFET導通,p-MOSFET截止,輸出為高電平。

- 當輸入為高電平時,p-MOSFET導通,n-MOSFET截止,輸出為低電平。

這種互補的工作方式使得CMOS邏輯門在靜態狀態下(無輸入變化時)幾乎不消耗功率,因為只有一個晶體管導通。

CMOS的優勢

- 低功耗 :CMOS電路在靜態狀態下功耗極低,只有在狀態變化時才消耗功率。

- 高集成度 :CMOS技術允許在小尺寸芯片上集成大量晶體管,實現復雜電路。

- 可靠性高 :CMOS電路具有較高的可靠性和穩定性。

- 可擴展性 :CMOS技術可以隨著工藝進步而不斷縮小晶體管尺寸,提高性能。

CMOS是晶體管嗎?

CMOS本身不是晶體管,而是一種使用p-MOSFET和n-MOSFET的半導體技術。這兩種晶體管是CMOS技術的基本構建塊,它們共同構成了CMOS電路的各種邏輯門和功能模塊。

晶體管的作用

晶體管,特別是場效應晶體管(FET),是現代電子設備中用于放大、開關、穩壓等的基本電子元件。在CMOS技術中,p-MOSFET和n-MOSFET作為晶體管,承擔著開關和放大的功能。

- 開關功能 :晶體管可以用作電子開關,控制電流的流動。

- 放大功能 :晶體管可以放大電信號,用于信號處理。

- 邏輯功能 :晶體管可以構建邏輯門,實現復雜的邏輯運算。

結論

CMOS技術以其低功耗、高集成度、高可靠性等優勢,在現代電子設備中得到了廣泛應用。CMOS電路是由p-MOSFET和n-MOSFET這兩種互補的晶體管構成的,它們共同工作以實現各種電子功能。

-

集成電路

+關注

關注

5452文章

12572瀏覽量

374554 -

CMOS

+關注

關注

58文章

6217瀏覽量

242846 -

晶體管

+關注

關注

78文章

10396瀏覽量

147763

發布評論請先 登錄

多值電場型電壓選擇晶體管結構

Robot之眼CMOS傳感器靜電防護指南

晶體管光耦的工作原理

CMOS的邏輯門如何應用在電路中

無結場效應晶體管器件結構與工藝

CMOS工藝流程簡介

什么是晶體管?你了解多少?知道怎樣工作的嗎?

浮思特 | CMOS技術原理與應用:從晶體管結構到反相器設計

CMOS的工作原理 CMOS是晶體管嗎?

CMOS的工作原理 CMOS是晶體管嗎?

評論