因為目前軟件的限制,RISCV的邏輯不能同時共用JTAG,所以如果想要同時去調試邏輯和RISCV的話,可以通過RISCV的soft Jtag來實現。soft Jtag就是通過GPIO來實現的軟件JTAG。這里我們以TI60F225 DEMO來演示。

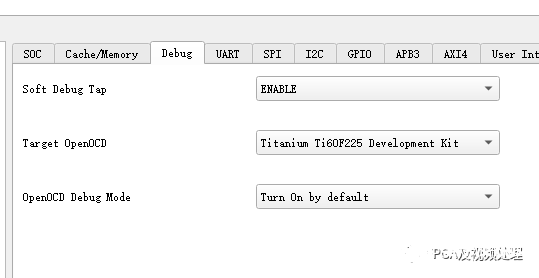

在使用softJTAG的過程中,首先要把RISCV的IP的調試選項選擇為soft,也就是Eanble Soft Debug Tap.

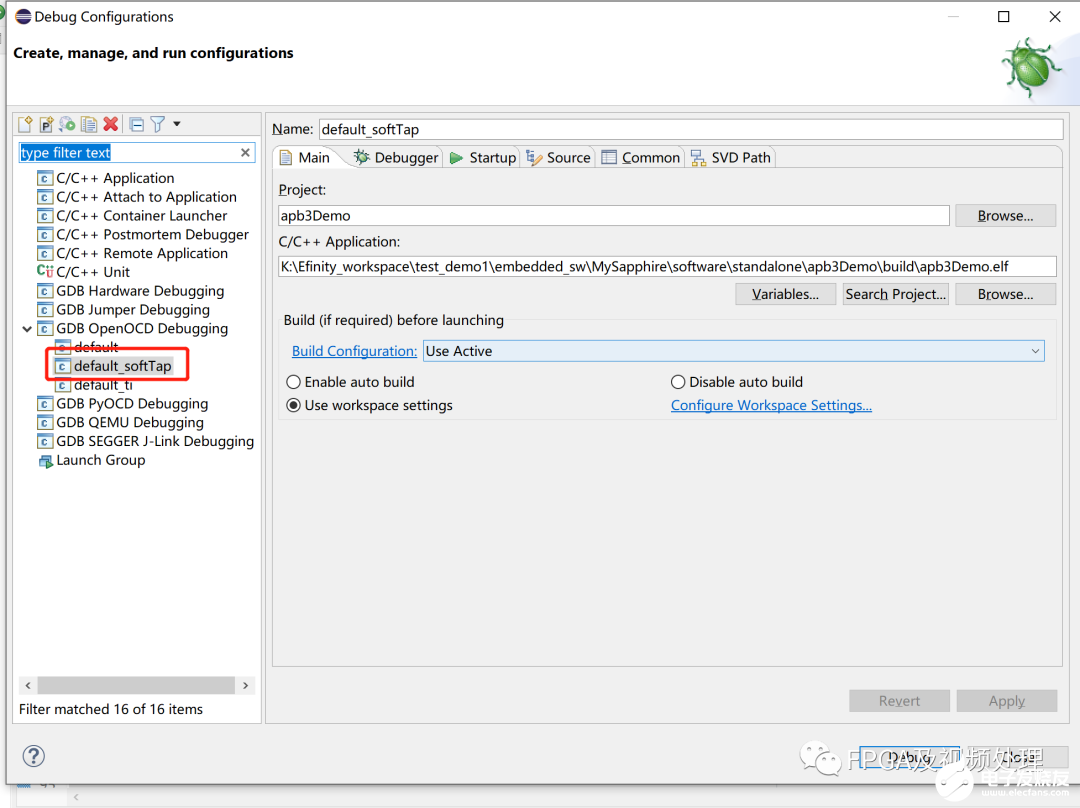

第二,使用softjtag 在通過openOCD來配置時要選擇default_softTap,它對應“embedded_swsapphire_socconfig”下面的default_softTap.launch文件。

第三個要注意的點就是器件的名稱。如果使用的是HardJtag會把ftdi_ti.cfg里面的器件與下面器件的名稱對應起來。但是softJtag對應的文件不是ftdi_ti.cfg也沒有對應的soft.cfg,而是對應c232hm_ddhsl_0.cfg,所以要把c232hm_ddhsl_0.cfg里面的器件名稱和下載器的對應起來。

打開“embedded_swsapphire_socconfig”下面的default_softTap.launch文件也可以看到調用文件的路徑指向的是c232hm_ddhsl_0.cfg

打開“embedded_swsapphire_socconfig”下面的default_ti.launch文件也可以看到調用文件的路徑指向的是ftdi_ti.cfg

在2023.1版本的RISCV中已經沒有c232hm_ddhsl_0.cfg文件了。代之的是一個external.cfg文件。

第四,如果使用易靈思下載器一定要連接VREF,并且要確認好IO電壓,一定要確認好IO電壓。

第五、使用soft Jtag容易出現連接不穩定的情況,以下來自Bruce 和Wayne的建議:

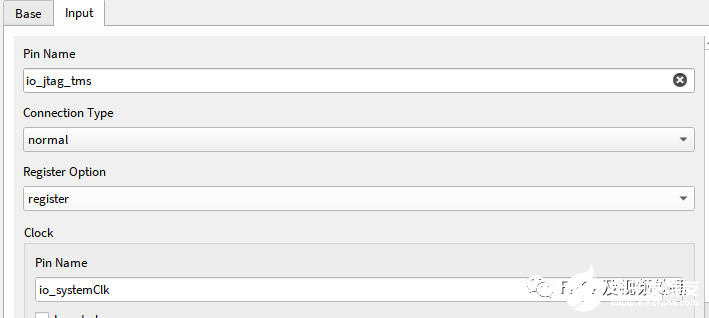

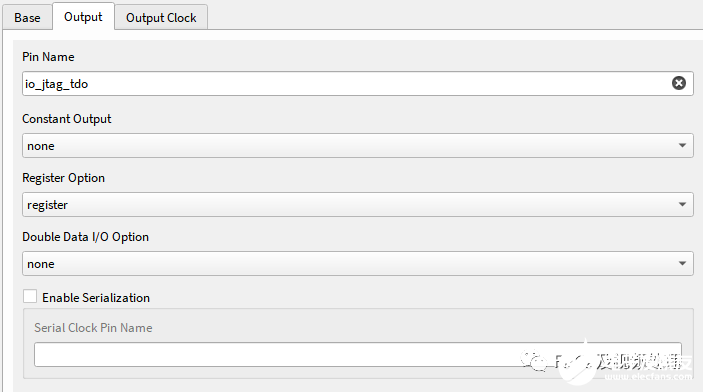

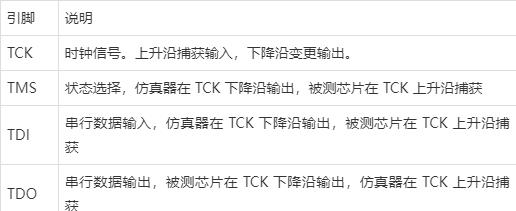

在Interface Designer里修改對應于JTAG softTAP的GPIO設置:

1. 打開TMS TDO內部弱上拉;

2. 打開TMS TDO TCK TDI GPIO的IO Register 并使用RISCV系統主時鐘驅動;

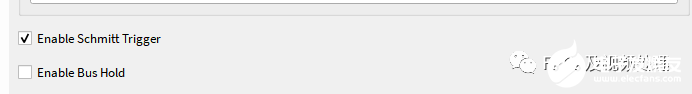

3. 如果SoftTAP綁定的是普通的GPIO,打開施密特觸發器和Slow Slew;

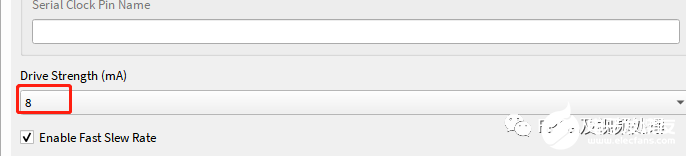

4.TDO 在 fpga輸出的驅動電流修改到最大;

下面以TMS和TDO為例的設置情況。

TMS參數設置

TDO參數設置

更新說明:補充器件的名稱在2023.1版本之后的說明。

審核編輯 黃宇

-

RISC

+關注

關注

6文章

485瀏覽量

86605 -

JTAG調試

+關注

關注

0文章

5瀏覽量

3019

發布評論請先 登錄

突破AMP架構調試瓶頸:RK3568開發板的JTAG仿真方案

用于SWD/JTAG調試器的多功能轉接板設計

嵌入式開發調試神器全解析:JTAG、SWD、串口打印

【CIE全國RISC-V創新應用大賽】+MUSE Pi Pro RiscV UEFI固件開發

全志D1開發板(哪吒 RISCV64)開箱評測

使用蜂鳥調試器,無法用cjtag協議調試CM32M433R芯片怎么解決?

windows下編譯riscv openocd是什么原因?

JTAG標準的狀態機實現

新品 | Cardputer Accessory Kit v1.1 &amp; Atomic GPS Base V2.0

有辦法讓SDK 1.3.5與JTAG調試器配合使用嗎?

RISC-V JTAG:開啟MCU 芯片調試之旅

canmv-k230-v1.1 wifi連不上是怎么回事?

FPGA的Jtag接口燒了,怎么辦?

新品 | Cardputer v1.1 與 Dial v1.1 Wi-Fi信號升級!更低功耗!

RISCV soft JTAG調試_v1.1

RISCV soft JTAG調試_v1.1

評論