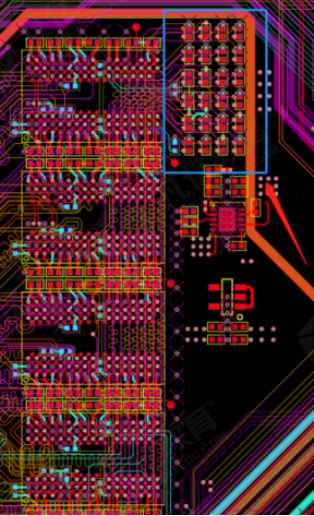

大家如果做過DDR的設計可能會發現在進行多片DDR連線時,通常在信號的末端會放置很多的電阻(如下圖所示),那么這些電阻都是起什么作用的呢?

通常在DDR末端的電阻是為了防止信號反射的,起阻抗匹配的作用,之前我們介紹過另一種防止信號反射的解決措施,就是在信號的發送端串聯一個電阻,從信號源端把問題解決,我們本次講的端接方式是從信號的末端入手,消除信號反射!

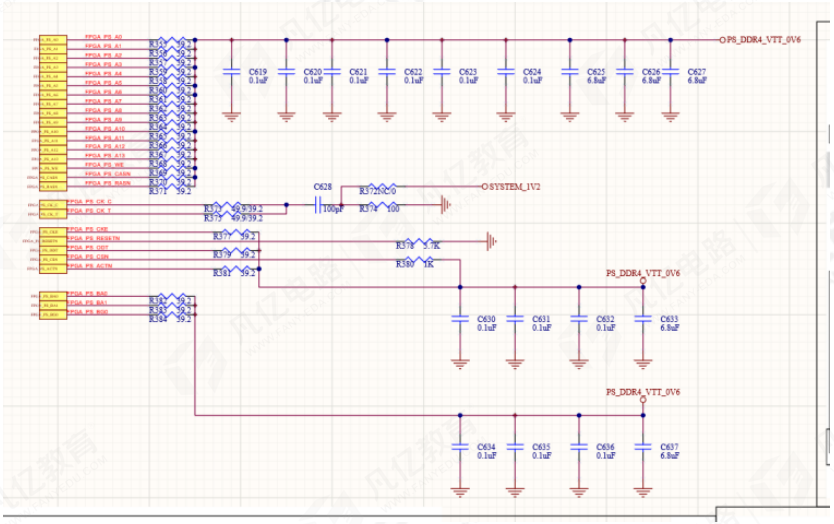

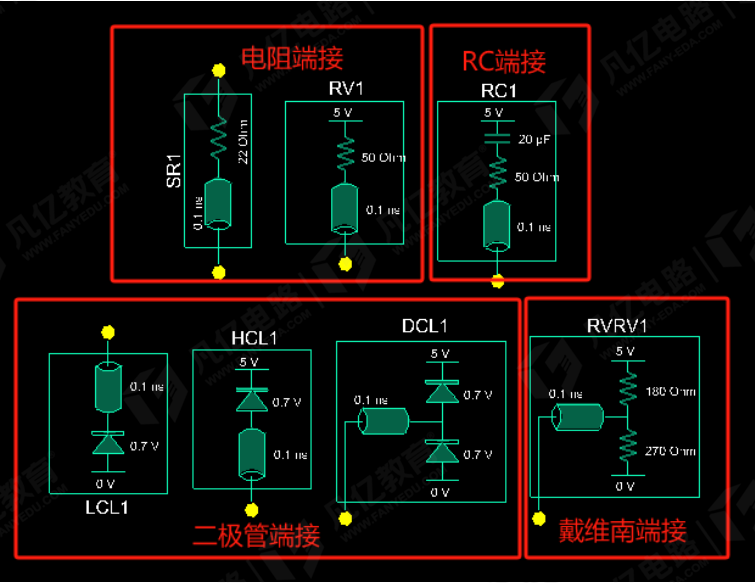

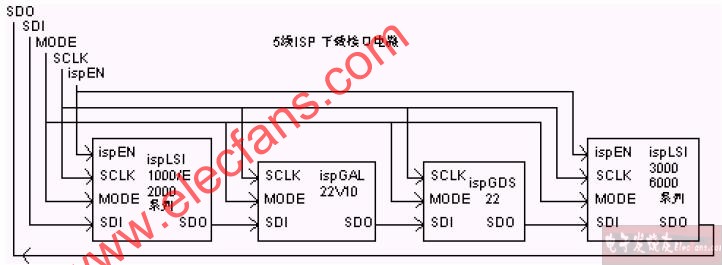

信號末端端接的方式有很多種,基本端接樣式式如下圖所示:

通常這些端接都可以有效的抑制信號的反射,不同的端接的應用場景也是有點區別的。

終端匹配電阻通過調整傳輸線末端的阻抗,使得反射信號與原始信號相互抵消。當傳輸線末端的阻抗與數據線之間的阻抗相匹配時,反射波最小,從而提高信號傳輸的質量和穩定性。

戴維南端接使用了兩個電阻并聯的方式,一個電阻下拉到地,一個電阻上拉到電源,其中接電源的電阻可以使驅動器更加容易到達邏輯高電平,接地的電阻可以使驅動器更加容易到達邏輯低電平,這兩個并聯電阻需要與傳輸線的阻抗相匹配,比如兩個電阻為R1和R2兩個電阻的阻值選取需要滿足公式Z0=R1*R2/R1+R2。

AC端接是在原有單一電阻端接上加了一個電容,一般采用0.1uF多層陶瓷電容,電容具有隔直流通交流的特性,因此可以有效的降低功率消耗,同時電容容值選取適當可以有效消除信號的過沖和下沖。

肖特基二極管端接是由兩個二極管組成,傳輸線末端任何的信號反射,如果導致接收器輸入端上的電壓超過VCC和二極管的正向偏值電壓,該二極管就會正向導通連接到VCC上。該二極管導通從而將信號的過沖箝位到VCC和二極管的閾值電壓的和上。

同樣連接到地上的二極管也可以將信號的下沖限制在二極管的正向偏置電壓上。然而該二極管不會吸收任何的能量,而僅僅只是將能量導向電源或者是地。該端接能有效減小信號過沖和下沖,但是二極管的開關速度會限制響應時間,所以較高速系統不合適。

端接的方式有很多種,但是其目的都是一樣的,都是為了改善信號的質量,我們應該在合適的場景下選擇相應的端接方式。同時我們需要注意的是端接電阻需要盡量靠近最后一片DDR顆粒,這樣信號的改善效果最好。

審核編輯:劉清

-

二極管

+關注

關注

149文章

10410瀏覽量

178479 -

驅動器

+關注

關注

54文章

9083瀏覽量

155574 -

阻抗匹配

+關注

關注

14文章

368瀏覽量

32072 -

DDR

+關注

關注

11文章

754瀏覽量

69137 -

陶瓷電容

+關注

關注

4文章

476瀏覽量

25006

原文標題:為什么多片DDR菊花鏈拓撲連接時末端需要接很多的電阻

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

采用菊花鏈的方式連接多片ADS1299,有的片是內部信號的高電平有的是低電平,如何解決?

多片ADS1298采用哪種方式連接(級聯或者菊花鏈)?

SDRAM的電源系統及拓撲結構

ddr3菊花鏈拓撲結構是什么

多片DDR菊花鏈拓撲連接時末端的電阻都是起什么作用的呢?

多片DDR菊花鏈拓撲連接時末端的電阻都是起什么作用的呢?

評論