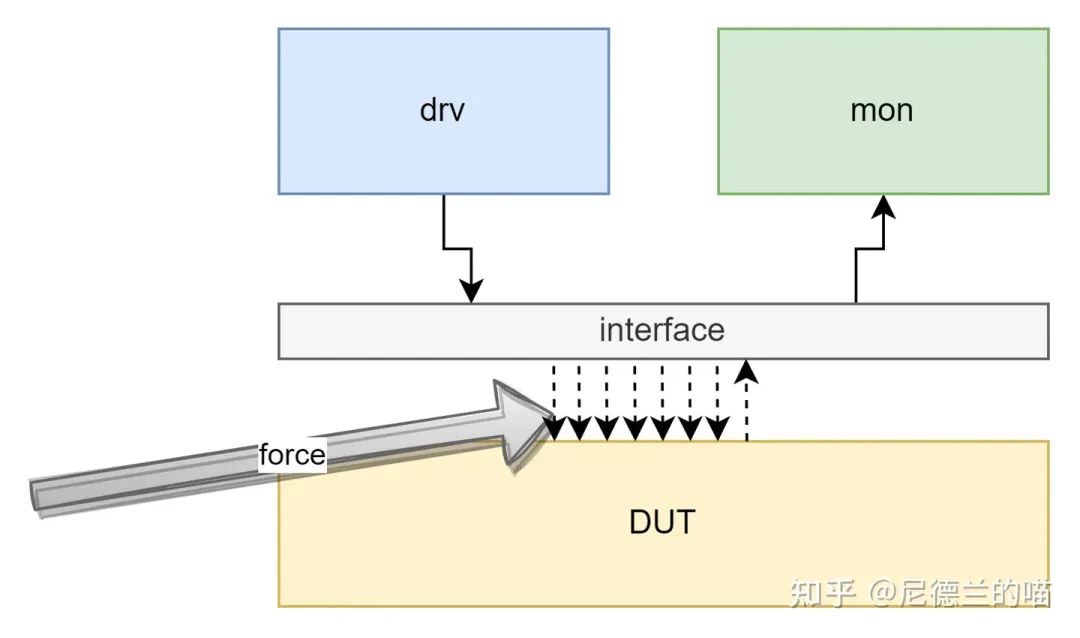

經(jīng)過遠(yuǎn)程的事故回放,可以說情況是非常明確的,這個代碼的互連結(jié)構(gòu)就是這么個典型結(jié)構(gòu):

如果用代碼表示呢,大概其就是這樣:

assign vid_in = u_tx_if.valid;

assign data_in = u_tx_if.data;

initial begin

force vid_in = 1'b0;

end

然后肇事者做個了什么操作呢,他去對RTL的接口進(jìn)行了force。說句題外話,講真的其實個人是不太理解在環(huán)境與RTL進(jìn)行互連的時候為什么會有force操作的,在我看來assign是完成能夠互連任務(wù)的。

唯一一種我能想到的場景就是RTL分別例化在BT和SST環(huán)境時,為了省力氣不想重新做互連結(jié)構(gòu)所以通過force的方式進(jìn)行驅(qū)動,除此之外不太能理解force的出現(xiàn)了。

還有一個原因讓我一直避免force,剛畢業(yè)的時候有大佬和我講,force、callback和宏是驗證環(huán)境里的三口“毒品”,用起來雖然很爽能快速的達(dá)到目的但是無異于飲鴆止渴,給環(huán)境帶來了很大的不確定和不可控風(fēng)險。

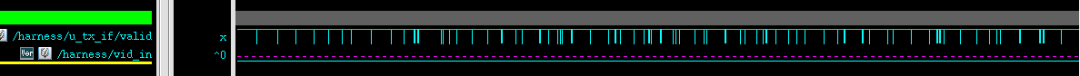

扯遠(yuǎn)了,回到剛剛的問題,肇事者對RTL的接口進(jìn)行了force,而后出現(xiàn)的現(xiàn)象就是,monitor通過u_tx_if采樣時還是采樣到了1也就是driver驅(qū)動的數(shù)值而不是force在接口上的數(shù)值。

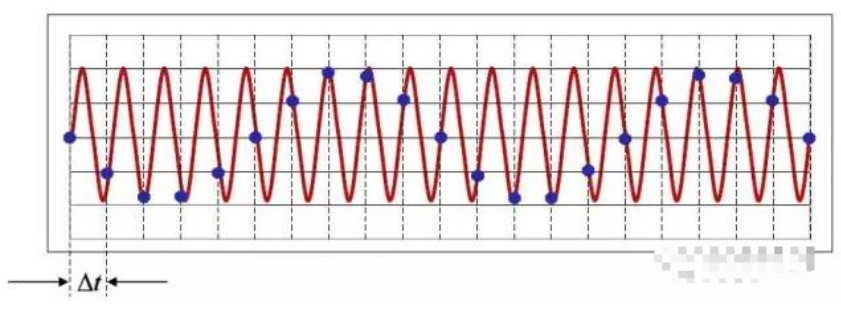

為什么還會采樣到1呢?顯然這里犯了一個形而上學(xué)的bug,仿真工具只是在模擬真實電路的行為,不是真的在內(nèi)部搭了一個電路,不是說通過assign a = b之后a和b就真的通過一根線給連在一起綁在一艘船上了!仿真時只會把assign等號右邊的值u_tx_if.valid賦值給左邊,不會把左邊的vid_in賦值給右邊啊:

那你mon連接的是u_tx_if,必然能夠采樣到drv本身驅(qū)動到interface上的值啊!

-

模擬電路

+關(guān)注

關(guān)注

126文章

1605瀏覽量

105426 -

SST

+關(guān)注

關(guān)注

0文章

108瀏覽量

36096 -

RTL

+關(guān)注

關(guān)注

1文章

394瀏覽量

62656 -

DRV

+關(guān)注

關(guān)注

0文章

18瀏覽量

20970

發(fā)布評論請先 登錄

關(guān)于tb中force signal的問題?

關(guān)于ti控制程序的問題,force angle freq和 IQ

swp2加入到vlan100其pvid功能也沒生效求解答

CubeMxSetting配置參數(shù)在rt-thread studio生效之后,提示文件不存在的原因是什么?

Design of Crimp force Monitor

Application of Atomic Force Mi

Force Spectroscopy with the At

Advanced Atomic Force Microsco

Force/Sense DAC Applications

Force/Sense DAC Applications

模組采樣線短路之后會怎樣?

如何設(shè)置采樣頻率才合理呢?

force之后,采樣時怎么沒生效呢?

force之后,采樣時怎么沒生效呢?

評論