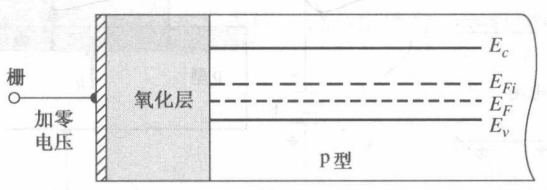

MOS結構能帶圖

金屬-絕緣體(氧化層)-半導體構成MOS結構,金屬作為柵極,當柵極零偏時,理想情況下半導體能帶是平的,意味著半導體內沒有凈電荷存在。

以P型半導體為例,對柵極加負電壓,受電場的影響,氧化物-半導體界面處的價帶更加靠近費米能級,說明這里有空穴的堆積,由于沒有電流流過,費米能級依然是水平的。

加正偏壓情況,界面處空穴被推離,費米能級離價帶更遠,產生空間電荷區。

繼續增大電壓,費米能級變得更接近導帶,說明半導體表面已從P型變成了N型,產生了電子反型層。

耗盡區寬度

先定義半導體的本征費米能級和EFi費米能級EF之差為?fp,以半導體體內為零勢能參考點,表面處的電勢?s稱為表面勢,它就是體內和表面本征費米能級的差值,那么耗盡區寬度可以寫為

當?s=2?fp時,表面處的電子濃度等于體內空穴濃度,這種情況稱為閾值反型點,此時外加的電壓稱為閾值電壓。如果外加電壓大于閾值電壓,表面處導帶會輕微地向費米能級彎曲,電子數量繼續增加,但耗盡區寬度將不會發生變化,因為此時反型層可以產生足夠多的負電荷,不需要擴展耗盡區。

功函數差

類似金半接觸,功函數的差異會導致電荷轉移產生電場和電勢差,這個電勢差會降落在氧化層和半導體內,

平帶電壓

平帶電壓的定義為當半導體內沒有能帶彎曲時所加的柵壓,此時表面勢為零,凈空間電荷為零,但由于功函數差和氧化層內可能存在的陷阱電荷,此時穿過氧化物的電壓不一定為零。

假設氧化物中陷阱電荷量為Qss′,單位面積的柵氧化層電容為Cox,則平帶時穿過氧化物的電壓為

要想使表面勢為零,需要產生一個能抵消功函數差和氧化物陷阱電荷的電壓(注意實際功函數差和氧化層電荷的正負號)

這個電壓就叫平帶電壓(也可以認為是零偏時的表面電勢)。

閾值電壓

閾值電壓定義為達到閾值反型點時所加的柵壓。在剛反型時,耗盡層空間電荷值達到最大值

先暫時不考慮功函數差和氧化層電荷的影響,從理想MOS結構來看,此時閾值電壓就等于氧化層電壓和表面電勢之和

考慮功函數差和氧化層電荷的影響,加上平帶電壓即可

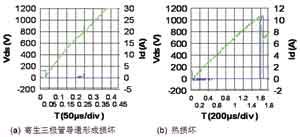

C-V特性

堆積模式下,MOS電容的單位面積電容就是柵氧化層電容,為定值

耗盡模式下,MOS電容為柵氧化層和耗盡層電容串聯

總電容隨耗盡區寬度增大而減小,當達到閾值反型點時,耗盡區寬度達到最大,此時總電容最小。

反型情況下,如果反型層電荷能跟上電容電壓的變化(低頻),則總電容就是柵氧化層電容(公式同積累模式)

如果反型層電荷跟不上電容電壓的變化(高頻),則總電容就是閾值反型時的最小電容。

不同的氧化層電荷會導致C-V曲線的平移(只影響平帶電壓),可以用來確定氧化層電荷。

界面態存在時,C-V曲線形狀將會發生變化,因為界面態中的電荷數量會隨著外加電壓變化而變化。

思考

堆積/耗盡/反型的電子/空穴來源是哪里?

在達到閾值電壓前,氧化層壓降和半導體表面電勢之間是如何分配的。

-

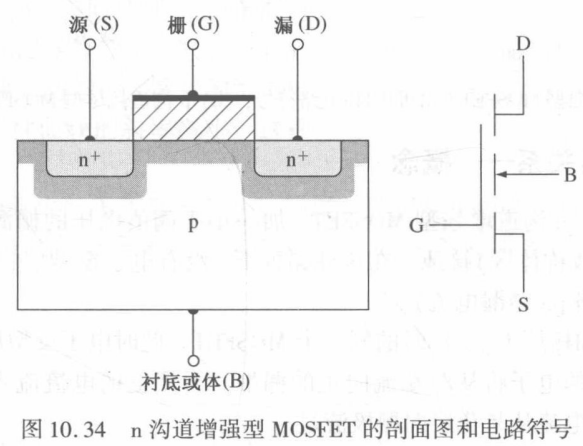

MOSFET

+關注

關注

151文章

9676瀏覽量

233633 -

半導體

+關注

關注

339文章

30747瀏覽量

264328 -

MOS

+關注

關注

32文章

1742瀏覽量

100755 -

源極

+關注

關注

1文章

55瀏覽量

8540

發布評論請先 登錄

功率MOSFET基本結構:平面結構

MOSFET結構解析(2)

MOSFET的基本結構與工作原理

功率MOSFET結構及特點

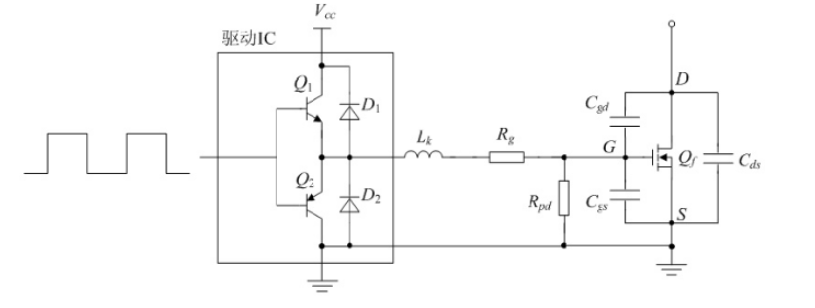

【資料不錯】MOSFET開時米勒平臺的形成過程的詳細解析!

溝槽結構SiC-MOSFET與實際產品

溝槽型SiC MOSFET的結構和應用

解析GaN-MOSFET的結構設計

深入解析 onsemi NTHL045N065SC1 SiC MOSFET

MOSFET結構解析(1)

MOSFET結構解析(1)

評論