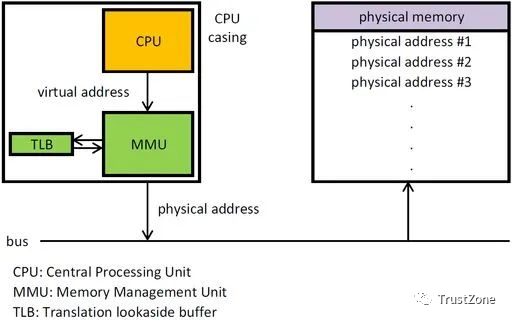

TLB 是 translation lookaside buffer 的簡稱。首先,我們知道 MMU 的作用是把虛擬地址轉換成物理地址。

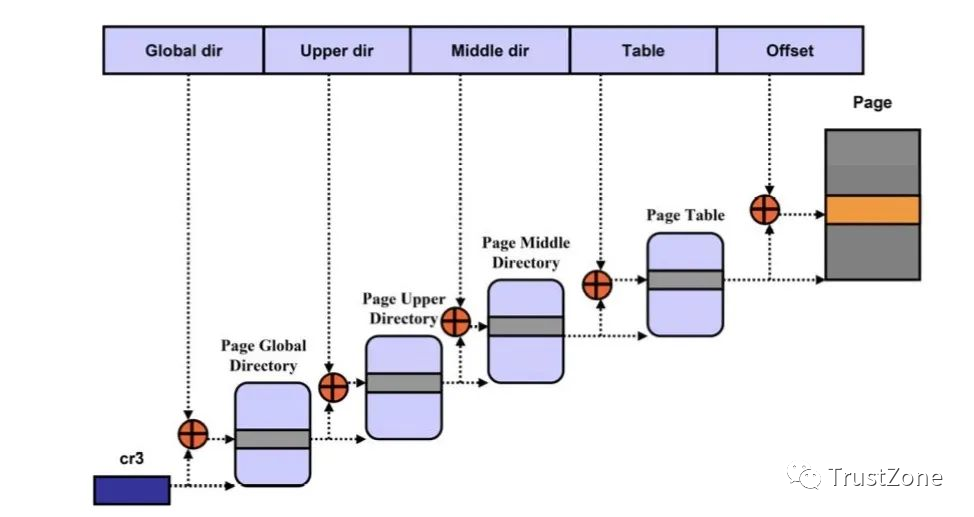

虛擬地址和物理地址的映射關系存儲在頁表中,而現在頁表又是分級的。

64 位系統一般都是 3~5 級。

常見的配置是 4 級頁表,就以 4 級頁表為例說明。

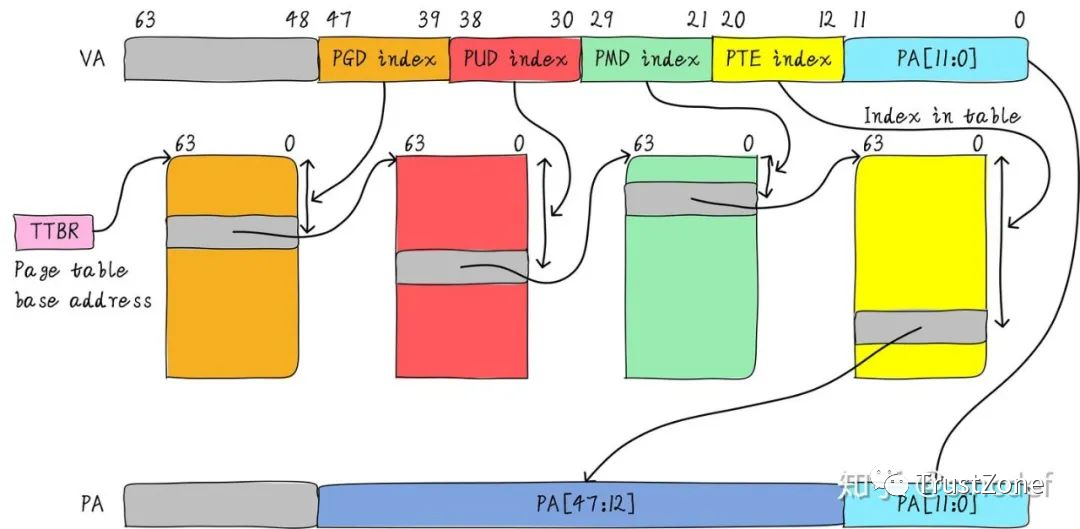

分別是 PGD、PUD、PMD、PTE 四級頁表。

在硬件上會有一個叫做頁表基地址寄存器,它存儲 PGD 頁表的首地址。

MMU 就是根據頁表基地址寄存器從 PGD 頁表一路查到 PTE,最終找到物理地址(PTE頁表中存儲物理地址)。

這就像在地圖上顯示你的家在哪一樣,我為了找到你家的地址,先確定你是中國,再確定你是某個省,繼續往下某個市,最后找到你家是一樣的原理。一級一級找下去。(這個比喻真的不錯)

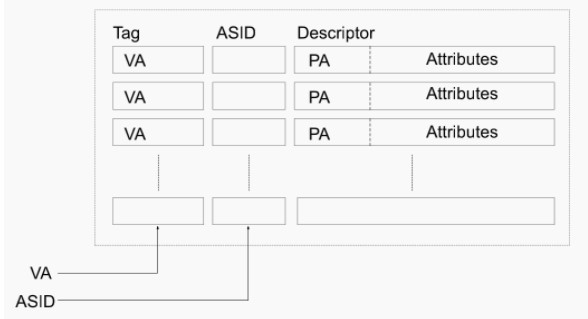

這個過程你也看到了,非常繁瑣。如果第一次查到你家的具體位置,我如果記下來你的姓名和你家的地址。下次查找時,是不是只需要跟我說你的姓名是什么,我就直接能夠告訴你地址,而不需要一級一級查找。

四級頁表查找過程需要四次內存訪問。延時可想而知,非常影響性能。頁表查找過程的示例如下圖所示。以后有機會詳細展開,這里了解下即可。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

寄存器

+關注

關注

31文章

5608瀏覽量

130002 -

內存

+關注

關注

9文章

3210瀏覽量

76377 -

硬件

+關注

關注

11文章

3595瀏覽量

69021 -

MMU

+關注

關注

0文章

92瀏覽量

19227

發布評論請先 登錄

相關推薦

熱點推薦

詳解TLB的作用及工作原理

了TLB,TLB是Translation Lookaside Buffer的簡稱,可翻譯為“地址轉換后援緩沖器”,也可簡稱為“快表”。簡單地說,TLB就是頁表的Cache,其中存儲了當前最可能被訪問

發表于 05-12 14:41

?5498次閱讀

請問AM335 u-boot 中的MMU,gd->arch.tlb_addr是在哪里初始化的?

本帖最后由 一只耳朵怪 于 2018-6-20 15:46 編輯

在board_init_f 函數中,只有定義了CONFIG_SYS_DCACHE_OFF,才會對 tlb_addr 初始化

發表于 06-20 02:06

labview2015調用tlb庫錯誤信息:LabVIEW: 輸入為空引用句柄或之前已刪除的引用句柄。

一個設備的控制API給的是*.tlb,使用工具注冊后以ActiveX的方式加載到labview中,運行報錯如下。不知為何報錯?請有經驗的大牛們指導一二。謝謝測試程序(2015)+API的tlb庫和注冊工具見附件

發表于 07-12 14:25

FIDEMAILATION中的TLB異常

我從SMTP.C文件中找到了FIDEMAILATION中的TLB異常。這似乎只有當我在優化級別1并運行沒有斷點的例程時才發生。如果我跨過它,一切似乎都起作用了。我在和諧1.04,XC 1.34

發表于 09-18 13:22

以Freescale的E500內核為例簡單介紹TLB Entry基本組成結構

稱之為頁表(Page Table)。最容易的想到的是使用主存儲器存放這個映射關系表,但是沒有程序能夠忍受在使用虛擬地址訪問一段物理空間時,首先需要從主存儲器的頁表中獲得物理地址。使用TLB

發表于 09-07 14:38

看一條關于TLB維護的指令

今天來看一條關于TLB維護的指令,無效操作指令TLBI。TLBI指令用于TLB無效操。TLBI指令的編碼格式如下:TLBI的語法格式如下:TLBI <tlbi_op>

發表于 02-16 13:59

P2020 TLB0/TLB1失效的原因?怎么解決?

P2020初始化時,需要通過MMUCSR0(MMU Control and Status Register 0)使TLB0和TLB1失效,我的問題是TLB0/TLB1失效:如果

發表于 03-21 07:57

嵌入式處理器的TLB電路設計

摘要:為了提高基于虛擬存儲技術的嵌入式處理器的性能,本文提出了一種用于高效加速地址轉換的TLB電路結構該電路采用64-entries的全關聯結構,硬件支持基于段及不同大小頁的轉

發表于 05-12 10:01

?18次下載

CPU場景下的TLB相關細節

一、前言 進程切換是一個復雜的過程,本文不準備詳細描述整個進程切換的方方面面,而是關注進程切換中一個小小的知識點:TLB的處理。為了能夠講清楚這個問題,我們在第二章描述在單CPU場景下一些和TLB

Versal ACAP、APU - DSB 指令后可能會發生推測性 TLB 填充

和 ISB 的組合可防止隨后的猜測。但是,對于在 DSB SYS + ISB 之后執行頁面轉換的單次加載、存儲或其他內存操作,可推測在 DSB SYS + ISB 完成之前的初始查找中是否發生了 TLB 錯誤,并填充新的 TLB 條目。

發表于 08-05 17:27

?728次閱讀

TLB成功開發出CXL內存模塊PCB,并向三星和SK海力士提供首批樣品

近日,韓國上市PCB制造商TLB (KOSDAQ:356860)成功開發出CXL內存模塊PCB,并已獨家向三星電子和SK海力士提供了6款以上的首批樣品。

為什么要有TLB

為什么要有TLB

評論