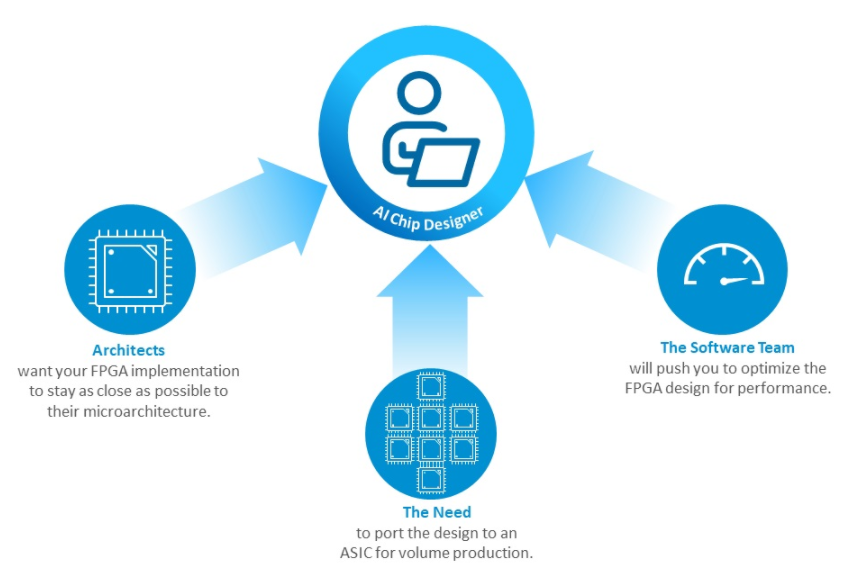

如果您選擇——大多數(shù)團隊都會選擇——用FPGAs進行概念驗證或驗證平臺,那么從一開始,您就會被同時拉向三個方向,如圖1所示。架構(gòu)師希望您的FPGA實現(xiàn)盡可能接近他們的微架構(gòu)。對他們來說,關(guān)鍵是看設(shè)計如何有效地實現(xiàn)他們的算法。但是,軟件團隊會督促您針對性能優(yōu)化FPGA設(shè)計。這意味著改變架構(gòu)以適應(yīng)所選FPGA芯片的優(yōu)勢和限制。你可以依靠營銷來增加這種壓力——主要是如果他們的計劃包括早期進入FPGAs市場。存在這樣一種風(fēng)險,即概念的證明會像科學(xué)怪人一樣,有自己的生命。

圖1:如果你選擇在FPGAs中做一個概念驗證或驗證平臺,你會被拉向三個方向:來自架構(gòu)師、軟件團隊和生產(chǎn)需求。

第三,需要將設(shè)計移植到ASIC上進行批量生產(chǎn)。這將為您帶來競爭力所需的性能、動力和面積。理想情況下,ASIC設(shè)計將準(zhǔn)確反映最初的理論架構(gòu),并針對您選擇的ASIC工藝和IP庫進行優(yōu)化。通過轉(zhuǎn)換成熟的FPGA設(shè)計,您可以在多大程度上獲得ASIC設(shè)計,這是一個至關(guān)重要的問題。答案將取決于架構(gòu)師、FPGA和ASIC團隊合作的緊密程度。

也許支持這種說法的最好方式是看看一些區(qū)分人工智能加速器的架構(gòu)特征,并在設(shè)計過程中遵循它們。

并行處理是人工智能加速器的基礎(chǔ)。它可以通過大量小型專用處理核心來實現(xiàn),如特定算法的GPU。或者它可以以數(shù)據(jù)流的方式完成:專用處理器的流水線。這兩種架構(gòu)都給FPGA實現(xiàn)帶來了挑戰(zhàn)。

設(shè)計者可以在RTL對處理元件及其互連進行編碼,并將RTL交給FPGA設(shè)計工具。但是,要獲得具有足夠設(shè)備利用率和性能的設(shè)計——獲得接近100%的布線——通常至少需要在平面規(guī)劃和布局方面進行人工干預(yù)。

這種規(guī)劃必須關(guān)注FPGA中資源的可用性和位置,而不是加速器的原始架構(gòu)。例如,該體系結(jié)構(gòu)可能希望計算元素群集在本地組中。然而,F(xiàn)PGA可能要求您將計算元素分散在整個芯片中,甚至將它們分成更小的模塊,以確保足夠的路由和RAM資源。這可能需要改變互連架構(gòu),例如改變總線結(jié)構(gòu)。

還會出現(xiàn)其他選擇。例如,深度學(xué)習(xí)推理加速器的設(shè)計師經(jīng)常使用精度降低的算法——比如8位而不是32位——來提高速度和節(jié)省能源。但出于性能和資源的原因,F(xiàn)PGA團隊可能希望使用FPGA的32位乘累加硬宏,而不是由邏輯單元構(gòu)造的8位乘法器。這種選擇會使FPGA設(shè)計逐漸偏離原始架構(gòu),并影響轉(zhuǎn)換過程。

ASIC轉(zhuǎn)換

然后,是時候?qū)崿F(xiàn)轉(zhuǎn)移到ASIC上了。在小型、簡單的SOC中,F(xiàn)PGA到ASIC的轉(zhuǎn)換意味著一個近乎機械的逐步過程。拿出任何特殊的FPGA功能,如乘法累加模塊、高速串行接口、PCIe接口和DRAM控制器。用功能等同的ASIC IP替換它們,并對內(nèi)部總線或接口進行任何必要的更改以連接它們。為了重新合成邏輯,插入新的時鐘網(wǎng)和自測結(jié)構(gòu),分配功率,并進行驗證。

這對于人工智能加速器來說仍然是可行的。在FPGA中工作的任何東西都可以通過這種方式轉(zhuǎn)移到ASIC中。但是,您為優(yōu)化FPGA設(shè)計所做的設(shè)計更改呢?由于ASIC中有基本上無限的邏輯和路由資源以及大量的第三方IP庫,這些針對FPGA的更改將是不必要的,甚至可能適得其反。

進行轉(zhuǎn)換的團隊必須理解最初的設(shè)計意圖,這樣他們才能根據(jù)具體情況決定是使用FPGA設(shè)計還是恢復(fù)最初的架構(gòu)。這對于確定合成哪個代碼和選擇如何最好地使用IP是正確的。

再舉兩個例子可能會有幫助。首先是記憶。由于它們的并行架構(gòu),AI加速器通常在處理元件內(nèi)部或之間采用許多不同形狀、大小、類型和速度的小型RAM實例。這種做法完全符合ASIC設(shè)計的優(yōu)勢,但它可能會對FPGA造成嚴(yán)重破壞。雖然可以將各組FPGA邏輯單元轉(zhuǎn)換成邏輯結(jié)構(gòu)中的小RAM,但設(shè)計人員通常會在FPGA中使用大型硬連線可配置RAM模塊。這給FPGA團隊留下了兩個選擇:要么修改原始架構(gòu),使用大的共享RAM塊,而不是許多較小的塊,要么設(shè)計一個包裝FPGA的大塊RAM的包裝器,以仿真一組較小的實例,希望不會耗盡塊RAM附近的路由資源。

圖2:從FPGA遷移到ASIC提供了更多選擇。決策取決于對設(shè)計意圖的清晰理解。

當(dāng)從FPGA轉(zhuǎn)移到ASIC時,有更多的選擇,如圖2所示。轉(zhuǎn)換團隊?wèi)?yīng)該直接轉(zhuǎn)換FPGA設(shè)計嗎?經(jīng)驗豐富的轉(zhuǎn)換供應(yīng)商在ASIC設(shè)計中實現(xiàn)FPGA模塊RAM的功能不會有任何問題。或者團隊?wèi)?yīng)該恢復(fù)到具有許多分散的RAM實例的原始架構(gòu)?更小的ram將更快、更節(jié)能,并可能恢復(fù)原始架構(gòu)的數(shù)據(jù)流,消除可能的內(nèi)存瓶頸。然而,決策取決于對設(shè)計意圖的清晰理解。

多合一

還有多個FPGAs的問題。許多加速器設(shè)計對于單個FPGA來說太大,必須分布在多個芯片上。這些芯片如何相互通信將影響轉(zhuǎn)換過程。

例如,如果FPGA通過諸如存儲器總線的高速并行總線鏈接,設(shè)計者可以將所有FPGA的內(nèi)容放入ASIC中,通過相同的并行總線排列鏈接。假設(shè)FPGAs通過類似PCIe的東西連接。在這種情況下,設(shè)計人員將不得不移除PCI接口,并根據(jù)模塊間數(shù)據(jù)流的性質(zhì),用直接并行連接或可能的片上網(wǎng)絡(luò)來取代它們。重要的是要回顧原始架構(gòu),看看它是否被修改以適應(yīng)芯片到芯片接口的插入——例如,通過插入大緩沖存儲器或創(chuàng)建消息傳遞協(xié)議——并消除這些修改。

密切的合作

一旦功能設(shè)計完成,工作就可以進入時鐘架構(gòu)了。這里,ASIC也不受FPGAs的限制。轉(zhuǎn)換團隊可以研究原始架構(gòu)的工作原理,并利用它為本地時鐘區(qū)域、門控和頻移提供的所有機會,所有這些在ASIC領(lǐng)域都是現(xiàn)成的。

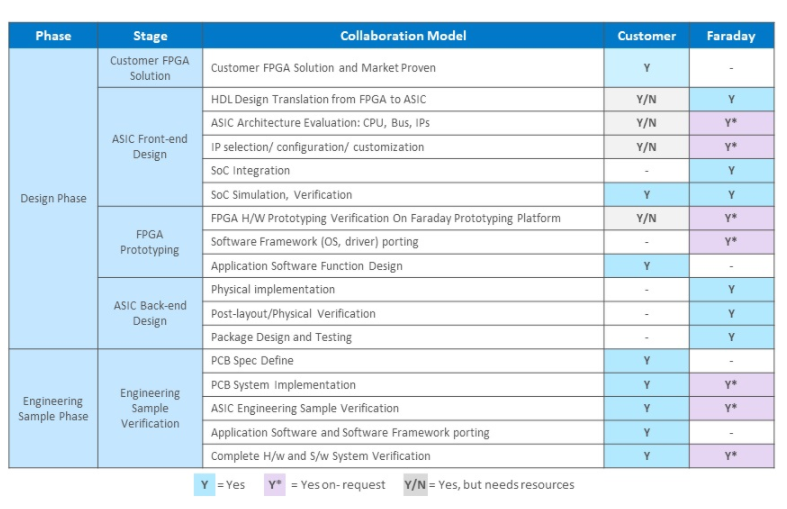

圖3:該表列出了FPGA到ASIC轉(zhuǎn)換過程中的每個步驟,并指明了負(fù)責(zé)執(zhí)行該步驟的人員。

同樣,經(jīng)驗豐富的轉(zhuǎn)換團隊可以利用他們對設(shè)計意圖的理解和對測試供應(yīng)商能力的了解,利用加速器的并行架構(gòu)來實施并行內(nèi)置自測。這種優(yōu)化超越了ASIC設(shè)計,深入到供應(yīng)鏈中。做得好的話,它將大幅降低測試成本,顯著節(jié)約整體單位成本,如圖3所示。

我們已經(jīng)看到,將AI加速器設(shè)計從中間FPGAs轉(zhuǎn)換為ASIC幾乎是一個機械的過程。但由于人工智能高度并行加速器的性質(zhì),理解原始設(shè)計意圖和架構(gòu)微妙之處、能夠識別FPGA特定優(yōu)化、擁有人工智能芯片經(jīng)驗、能夠在客戶和供應(yīng)商專家之間自由分配任務(wù)的轉(zhuǎn)換團隊可以實現(xiàn)更好的結(jié)果。從一開始,具有出色功率、性能和面積的ASIC就是設(shè)計的全部內(nèi)容。

精彩推薦 至芯科技FPGA就業(yè)培訓(xùn)班——助你步入成功之路、11月30號北京中心開課、歡迎咨詢! 基于LVDS的高速串行數(shù)據(jù)傳輸系統(tǒng)設(shè)計 FPGA學(xué)習(xí)-異步FIFO原型設(shè)計與驗證掃碼加微信邀請您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標(biāo)題:為你的AI芯片從FPGA走向ASIC?

文章出處:【微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636368

原文標(biāo)題:為你的AI芯片從FPGA走向ASIC?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

倒計時開始!Embedded World 2026,Enclustra邀你見證FPGA/SoC與物理AI的未來

AI ASIC:博通份額將達60%,聯(lián)發(fā)科成長顯著,臺積電成最大贏家

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+AI芯片到AGI芯片

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+AI的科學(xué)應(yīng)用

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+AI芯片的需求和挑戰(zhàn)

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+可期之變:從AI硬件到AI濕件

AI 芯片浪潮下,職場晉升新契機?

【免費送書】AI芯片,從過去走向未來:《AI芯片:前沿技術(shù)與創(chuàng)新未來》

【書籍評測活動NO.64】AI芯片,從過去走向未來:《AI芯片:科技探索與AGI愿景》

AI芯片,需要ASIC

從14nm到3nm:AI ASIC算力、能效雙突破

邊緣AI盒子技術(shù)解析:ASIC/FPGA/GPU芯片及邊緣-云端協(xié)同與自適應(yīng)推理

從發(fā)明到 AI 加速:慶祝 FPGA 創(chuàng)新 40 周年

為你的AI芯片從FPGA走向ASIC?

為你的AI芯片從FPGA走向ASIC?

評論