作者: 謝敏釗,來源: 韜略科技EMC微信公眾號

一. 前言

隨著科技和智能設(shè)備的飛速發(fā)展,越來越多的電子產(chǎn)品應(yīng)運而生,但隨之而來的電磁輻射問題也越來越多,電磁輻射污染問題成為了繼大氣污染、水污染及噪聲污染之后的第四大污染,復雜的電磁環(huán)境不僅容易在電子產(chǎn)品間相互影響,嚴重的還會影響到我們的生活質(zhì)量以及我們的身心健康。而時鐘問題作為EMC測試中最常見的輻射問題之一,對工程師的困擾也十分嚴重,而鋪地接地作為硬件工程師LAYOUT基本技能之一,也蘊藏的很多學問在里面,稍有不慎,就可能導致EMC輻射超標,本文則針對該問題結(jié)合實際情況進行探討。

二. 實際案例

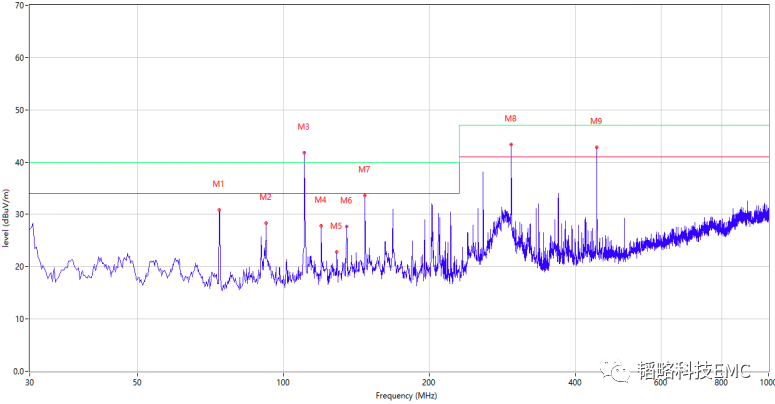

本文的主角是一款后裝車機,經(jīng)過測試摸底確認為時鐘輻射超標,具體數(shù)據(jù)如下:

經(jīng)過頻譜儀和時鐘篩查后,最終鎖定在某個模塊的時鐘上,如下圖:

(可以借助頻譜儀鎖定具體問題點)

三. 整改過程

具體問題源頭鎖定后,開始進行下一步的整改,采用常規(guī)的電阻、磁珠、電容濾波效果都不佳后,那就要繼續(xù)往其他的角度去思考是不是某個模塊或者線路或者地設(shè)計有問題導致,濾波基本都沒有效果。

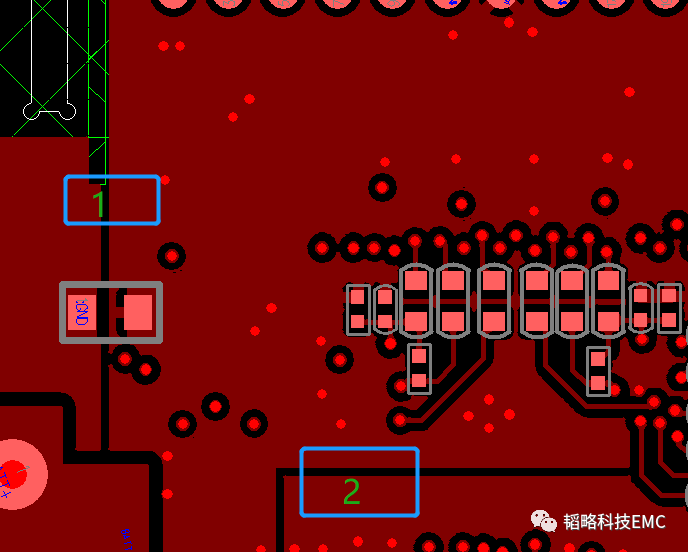

繼續(xù)用頻譜儀點板上的地,發(fā)現(xiàn)時鐘接受端模塊的地(模擬地)有超標頻點的時鐘出現(xiàn),比底噪高出十幾個dB,而用探針點系統(tǒng)地卻沒有超標時鐘出現(xiàn),說明模擬地被時鐘“污染”導致會影響到其他的走線,所以我們需要對地進行進一步的優(yōu)化。雖然該板子已經(jīng)有一個0Ω電阻接地,但是明顯該接地點并不能起到降低地阻抗的效果。在研究了PCB后,我們需要增加幾個接地點以優(yōu)化模擬地阻抗和噪聲回路。

(增加0Ω電阻位置優(yōu)化接地阻抗)

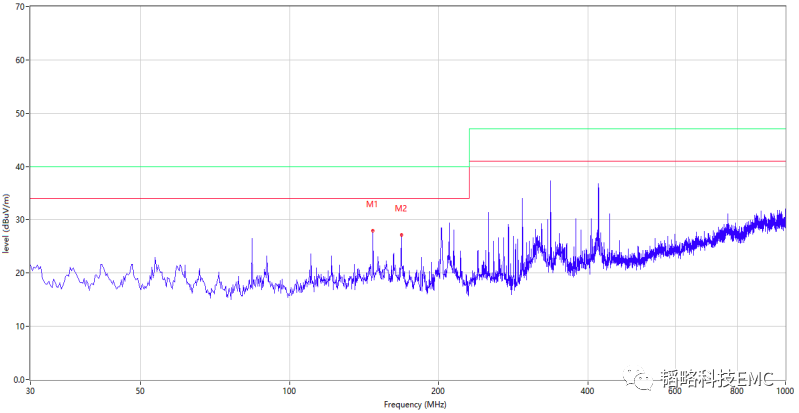

在優(yōu)化接地后,具體數(shù)據(jù)如下圖:

(優(yōu)化接地后測試數(shù)據(jù))

可以發(fā)現(xiàn),優(yōu)化接地后,時鐘頻點有很明顯的下降,雖然我們在時鐘源頭整改沒有效果,但是我們優(yōu)化時鐘接收端的地后卻又明顯的效果,說明該模塊的地阻抗和系統(tǒng)地的阻抗存在阻抗差導致時鐘回路改變從而導致時鐘輻射超標,所以我們PCB設(shè)計的時候要注意尤其模擬地和系統(tǒng)地的接地情況,在保持分地的情況也要考慮回路和阻抗差,從而從設(shè)計避免后續(xù)不必要的改版時間和拖延產(chǎn)品上市時間。

四. 總結(jié)

時鐘輻射超標問題確實是EMC整改過程非常棘手的問題,但是我們可以在設(shè)計初期就做好設(shè)計和預防,就可以盡量避免大部分的問題出現(xiàn)。

注:以上僅為本人觀點,如有不足之處,敬請指教。

審核編輯 黃宇

-

阻抗

+關(guān)注

關(guān)注

17文章

988瀏覽量

49240 -

時鐘

+關(guān)注

關(guān)注

11文章

1971瀏覽量

135000 -

emc

+關(guān)注

關(guān)注

176文章

4390瀏覽量

191593

發(fā)布評論請先 登錄

TSN時鐘同步 | PTP對時案例演示——基于NXP i.MX 8M Plus

AD9253對時鐘抖動的要求怎么樣,應(yīng)該選擇怎樣的時鐘架構(gòu)?

請問依靠RM48系列MCU的自身資源是否可以實現(xiàn)對時鐘的高覆蓋率診斷?

屏蔽地線對阻抗的影響有哪些

以datasheet中的時鐘樹圖為基礎(chǔ)對時鐘系統(tǒng)進行學習總結(jié)

在uboot中對時鐘進行了初始化

STM32庫函數(shù)對時鐘的設(shè)置

電力系統(tǒng)如何實現(xiàn)全站統(tǒng)一對時

如何對時鐘信號的轉(zhuǎn)換速率進行優(yōu)化的詳細中文介紹

地阻抗對時鐘的影響

地阻抗對時鐘的影響

評論