一、運放電路上的延時有哪些

1、Ts:運放的建立時間

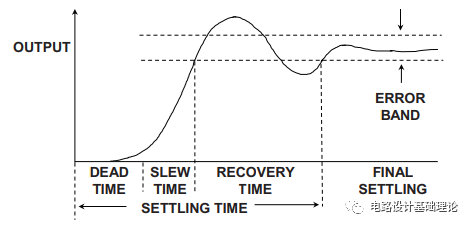

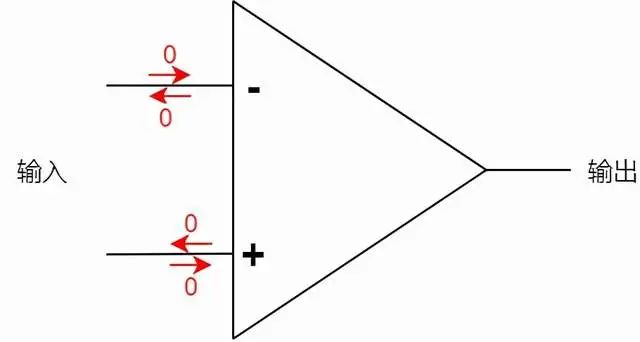

運放的建立時間主要分為兩階段,第一階段主要是運放輸出電壓從初始值到達目標值附近,這階段變化為非線性并且這段時間與壓擺率有關(guān) (壓擺率的大小決定了給運放補償電容充電的快慢),第二階段是輸出已經(jīng)接近目標值了,這階段變化為準線性,主要受運放的零-極點影響;在高速運放中,第一階段的時間很短,主要的建立時間都受第二階段影響。

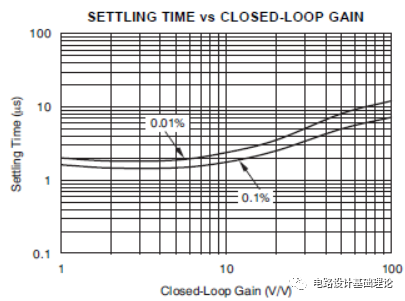

根據(jù)運放的特性來看,運放的建立時間會受大信號-壓擺率,小信號-閉環(huán)增益影響

根據(jù)GBW=G*Freq,當(dāng)閉環(huán)增益變大時,F(xiàn)req就會變小,進而導(dǎo)致輸出誤差的環(huán)路增益(AolB)變小,從而影響運放建立時間變長。

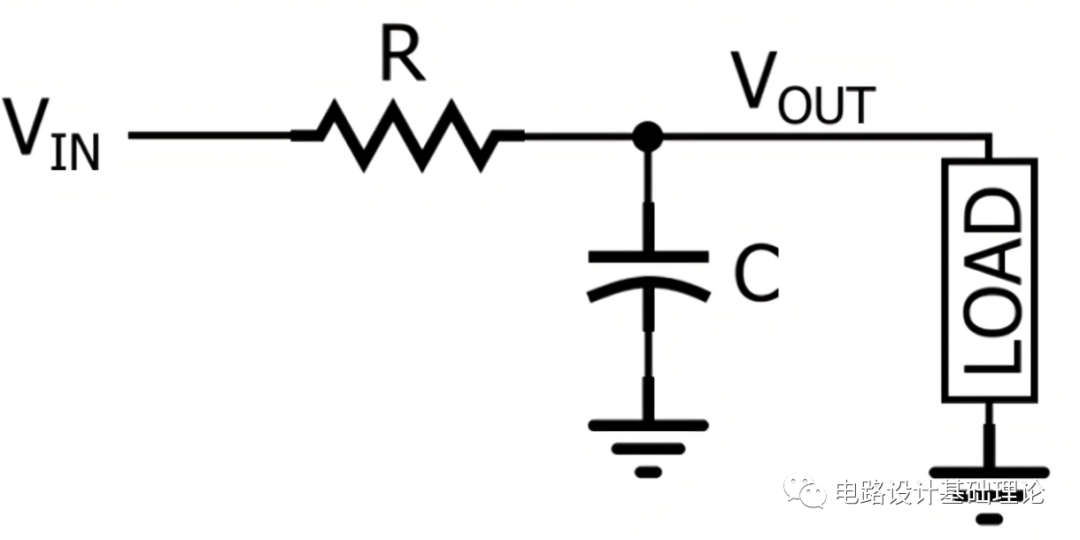

2、Trc:RC濾波電路延時

RC低通濾波器用于防止震蕩電路,這種設(shè)計通常被應(yīng)用于輸入端以及輸出端 通過電容充放電的反應(yīng)時間來使信號穩(wěn)定不變但同樣也使信號下降延遲了時間 。

二、如何選取合適的參數(shù)

1、運放的參數(shù)選取

影響到運放建立時間的主要參數(shù)為壓擺率、增益帶寬積兩個參數(shù)

壓擺率:Slew rate

SR=2ΠFreqVp

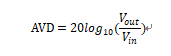

增益帶寬積:gain-bandwidth product

GBW=G*Freq

選擇運放時我們也應(yīng)該注意以下兩點:

失真特性:對于ADC的驅(qū)動運放來說,我們通常需要選擇輸入輸出軌對軌的運放,防止不必要的輸出失真。

噪聲特性:對于運放的噪聲特性來說,為了不讓運放的噪聲對ADC的精度產(chǎn)生影響,一般會使運放的總噪聲在ADC噪聲的1/5左右。

2、rc參數(shù)選取

運放rc濾波分為輸入濾波與輸出濾波

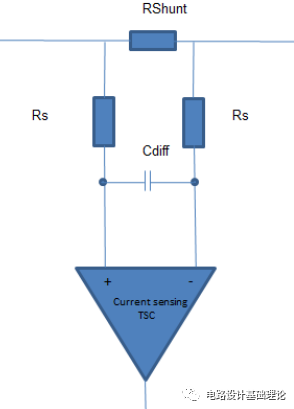

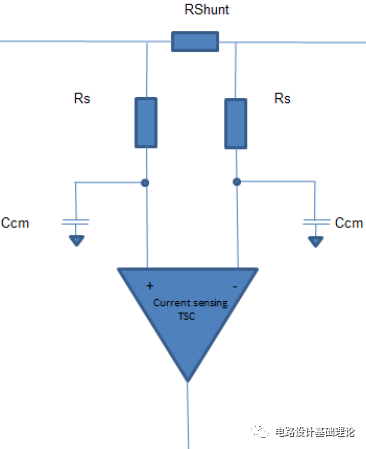

a:差模濾波:

F=1/(2Π2Rs*Cdiff)

b:共模濾波:

F=1/(2ΠRs*Ccm)

以上兩種輸入濾波電路根據(jù)信號頻率選擇合適的參數(shù)即可,本文不過多介紹,有些電路可能應(yīng)用差-共模濾波電路,主要注意Cdiff容值要大于Ccm,平衡Rs1-Ccm1、Rs2-Ccm2時間常數(shù)不匹配帶來的影響,一般取值Cdiff=Ccm*10

c:輸出濾波:

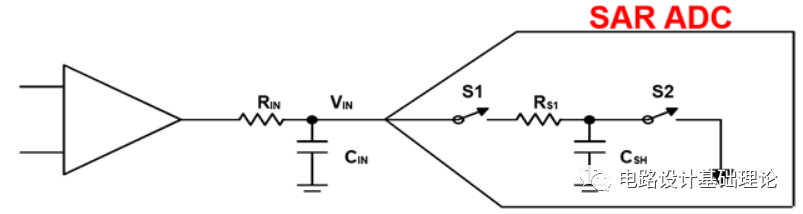

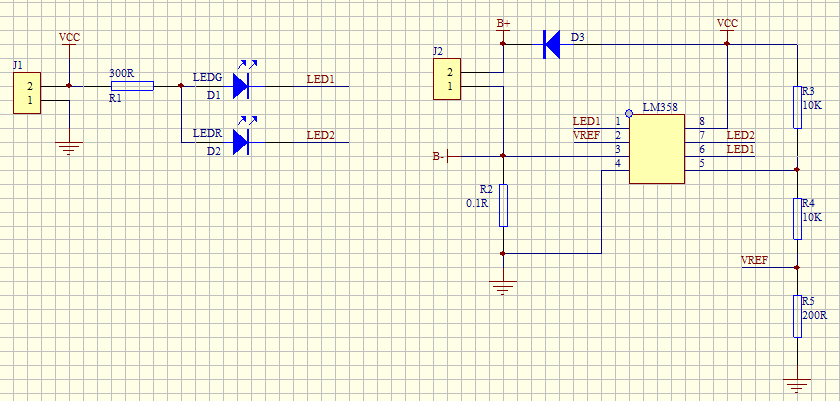

該圖為常見的SAR-ADC結(jié)構(gòu),針對該結(jié)構(gòu)展開如何設(shè)計RC電路,首先RC電路在該結(jié)構(gòu)中的作用有兩部分:

1、是對ADC的Csh進行充電,由于ADC采樣保持階段需要給采樣電容Csh充電。開始采樣時,Csh的電荷由輸入部分和RC濾波電容提供,保證在一定時間內(nèi)達到精度的要求。顯然,隨著采樣精度和采樣率的不斷提高,驅(qū)動ADC的難度加大,因為必須在有限的時間內(nèi)將Csh上的電壓達到滿足精度要求。所以我們在ADC前加入電容,當(dāng)采樣保持階段時對Csh進行充電,保證采樣的精度。電阻則作為隔離作用,避免運放直接驅(qū)動容性負載,提升系統(tǒng)的穩(wěn)定性。

2、RC網(wǎng)絡(luò)同時也限制了輸入信號的帶寬,并且降低了運放帶來的噪聲量,但是此時,帶寬的限制會使信號的延長建立時間,引起信號的失真。

基于以上兩點我們設(shè)計RC的目標就是在有限的的時間內(nèi)將Csh上的電壓滿足精度要求。

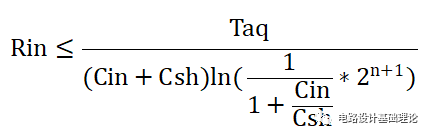

Tap:采集時間、n:ADC采集位數(shù)

Cin選取參考MCU內(nèi)部的采樣電容(sampling capacitance),一般取值為采樣電容的20倍左右。

-

運放電路

+關(guān)注

關(guān)注

39文章

367瀏覽量

36424 -

濾波器

+關(guān)注

關(guān)注

162文章

8444瀏覽量

186093 -

adc

+關(guān)注

關(guān)注

100文章

7932瀏覽量

556712 -

運放

+關(guān)注

關(guān)注

49文章

1230瀏覽量

55722 -

濾波電路

+關(guān)注

關(guān)注

47文章

657瀏覽量

71717

發(fā)布評論請先 登錄

淺談集成運放及典型運放電路

TINA仿真運放電路時,運放的參數(shù)中是否可以增加溫度參數(shù)呢?

從0學(xué)運放,史上最全運放電路設(shè)計入門資料

從零學(xué)運放—02怎樣分析運放電路

單運放構(gòu)成的單穩(wěn)延時電路

揭開運放電路神秘面紗:如何選型運放?

運放電路上的延時有哪些 運放如何選取合適的參數(shù)

運放電路上的延時有哪些 運放如何選取合適的參數(shù)

評論