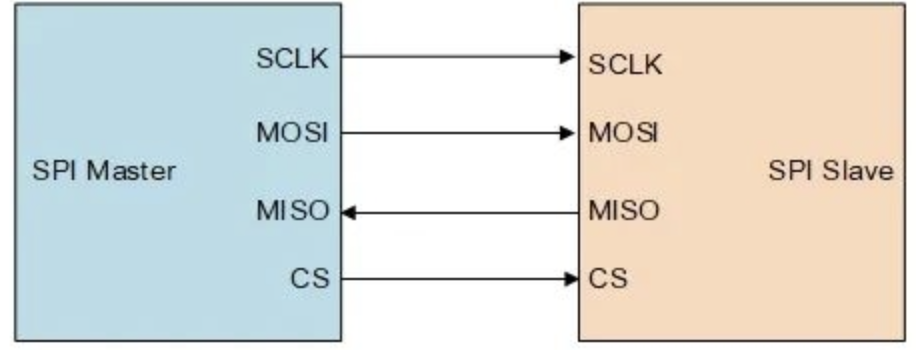

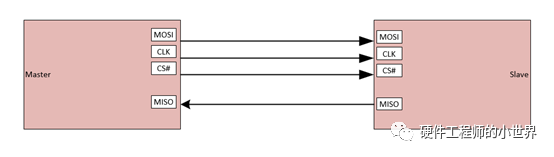

SPI用于CPU與各種外圍器件進行全雙工、同步串行通訊。它只需四條線就可以完成MCU與各種外圍器件的通訊,這四條線是:串行時鐘線(CSK)、主機輸入/從機輸出數(shù)據(jù)線(MISO)、主機輸出/從機輸入數(shù)據(jù)線(MOSI)、低電平有效從機選擇線CS。

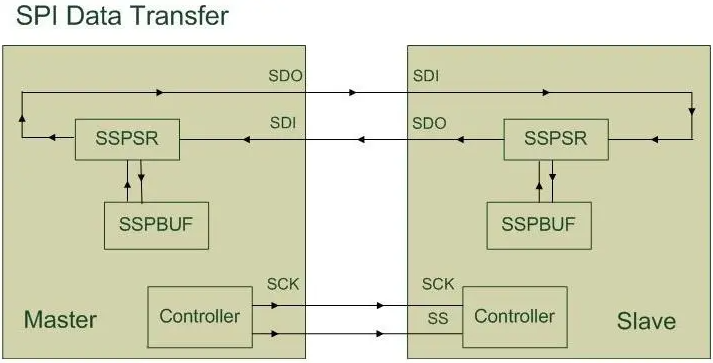

當(dāng)SPI工作時,在移位寄存器中的數(shù)據(jù)逐位從輸出引腳(MOSI)輸出(高位在前),同時從輸入引腳(MISO)接收的數(shù)據(jù)逐位移到移位寄存器(高位在前)。

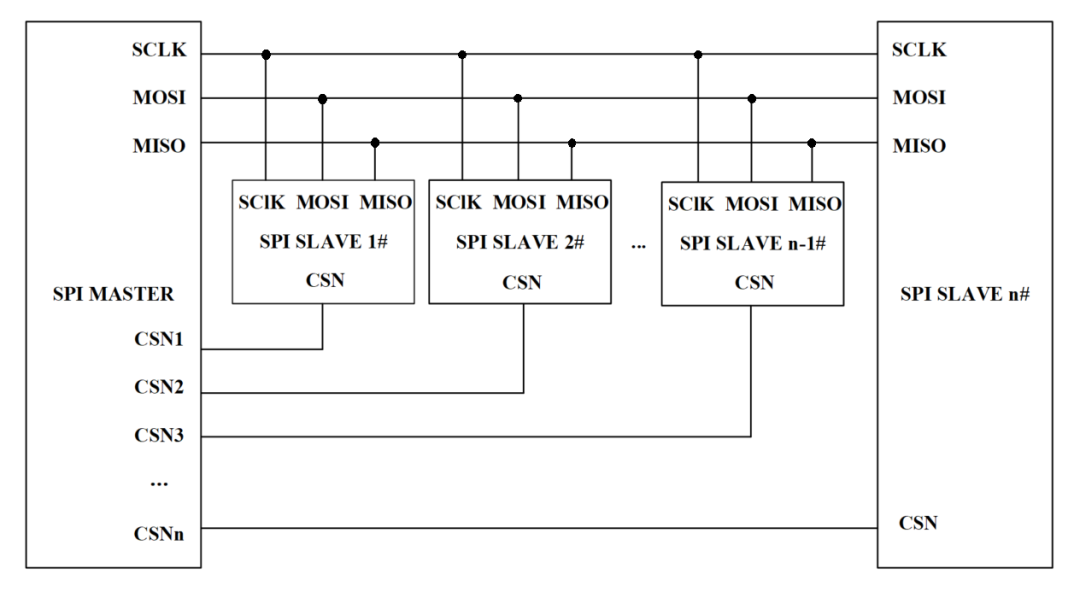

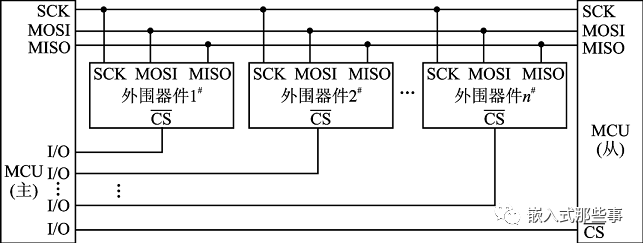

發(fā)送一個字節(jié)后,從另一個外圍器件接收的字節(jié)數(shù)據(jù)進入移位寄存器中。即完成一個字節(jié)數(shù)據(jù)傳輸?shù)膶嵸|(zhì)是兩個器件寄存器內(nèi)容的交換。主SPI的時鐘信號(SCK)使傳輸同步。SPI總線是同步、全雙工雙向的4線式串行接口總線。它是由“單個主設(shè)備+多個從設(shè)備”構(gòu)成的系統(tǒng)。

在系統(tǒng)中,只要任意時刻只有一個主設(shè)備是處于激活狀態(tài)的,就可以存在多個SPI主設(shè)備。常運用于AD轉(zhuǎn)換器、EEPROM、FLASH、實時時鐘、數(shù)字信號處理器和數(shù)字信號解碼器之間實現(xiàn)通信。

為了實現(xiàn)通信,SPI共有4條信號線,分別是:

主設(shè)備出、從設(shè)備入(Master Out Slave In,MOSI):由主設(shè)備向從設(shè)備傳輸數(shù)據(jù)的信號線,也稱為從設(shè)備輸入(Slave Input/Slave Data In,SI/SDI)。

主設(shè)備入、從設(shè)備出(Master In Slave Out,MISO):由從設(shè)備向主設(shè)備傳輸數(shù)據(jù)的信號線,也稱為從設(shè)備輸出(Slave Output/Slave Data Out,SO/SDO)。

串行時鐘(Serial Clock,SCLK):傳輸時鐘信號的信號線。

從設(shè)備選擇(Slave Select,SS):用于選擇從設(shè)備的信號線,低電平有效。

SPI 的工作時序模式由CPOL(Clock Polarity,時鐘極性)和CPHA(Clock Phase,時鐘相位)之間的相位關(guān)系決定,CPOL表示時鐘信號的初始電平的狀態(tài),CPOL 為0 表示時鐘信號初始狀態(tài)為低電平,為1 表示時鐘信號的初始電平是高電平。

CPHA 表示在哪個時鐘沿采樣數(shù)據(jù),CPHA 為0 表示在首個時鐘變化沿采樣數(shù)據(jù),而CPHA 為1 則表示在第二個時鐘變化沿采樣數(shù)據(jù)。

SPI總線特點

?全雙工

?可以當(dāng)作主機或從機工作

?提供頻率可編程時鐘

?發(fā)送結(jié)束中斷標(biāo)志

?寫沖突保護

?總線競爭保護等

-

寄存器

+關(guān)注

關(guān)注

31文章

5608瀏覽量

129998 -

接口

+關(guān)注

關(guān)注

33文章

9521瀏覽量

157041 -

SPI

+關(guān)注

關(guān)注

17文章

1885瀏覽量

101260 -

總線

+關(guān)注

關(guān)注

10文章

3040瀏覽量

91661

發(fā)布評論請先 登錄

一文詳解SPI串行外設(shè)接口

一文詳解SPI串行外設(shè)接口

一文詳解SPI串行外設(shè)接口協(xié)議

SPI(串行外設(shè)接口)工作原理介紹

如何利用SPI串行外設(shè)接口去讀取W25Q128的數(shù)據(jù)呢

SPI串行外設(shè)接口的優(yōu)缺點是什么

理解ATE SPI (串行外設(shè)接口)

一文讀懂SPI串行外設(shè)接口

怎樣設(shè)計一個基于AVR單片機的SPI串行外設(shè)接口?

SPI串行外設(shè)接口的編程說明資料免費下載

SPI 串行外設(shè)接口

SPI串行外設(shè)接口的特點概述

SPI串行外設(shè)接口設(shè)計實現(xiàn)

SPI串行外設(shè)接口是什么

SPI串行外設(shè)接口是什么

評論