** DC-PSRR**

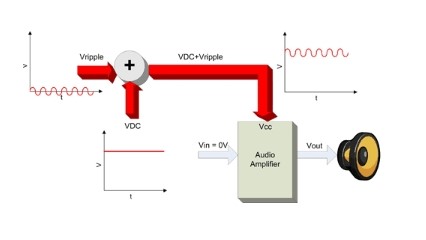

在理想運放中,運放的特性不會隨電源電壓的變化而變化。但實際應用時并非如此,實際運放在電源電壓發生變化時,總會引起運放參數的變化。

這就引出運放的一個重要參數,運放的電源(紋波)抑制比PSRR(Power Supply Ripple Rejection Ratio)。

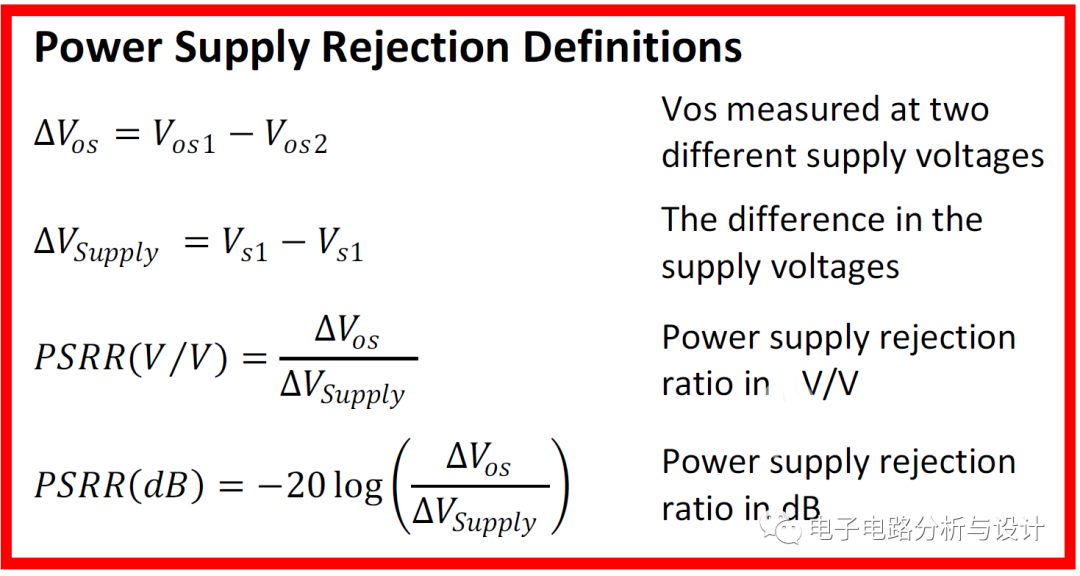

《SJT 10738-1996 半導體集成電路 運算(電壓)放大器測試方法的基本原理》一文中給出其定義:電源的單位變化所引起的輸入失調電壓的變化率。公式如下圖,可知PSRR可以用V/V、μV/V或dB表示。

這兩種表示方法,都可以讓我們清楚的理解到運放對電源電壓變化的抑制能力。注:DC-PSRR表示直流電壓源(頻率為0)大小變化時,對輸入失調電壓大小變化的抑制能力。

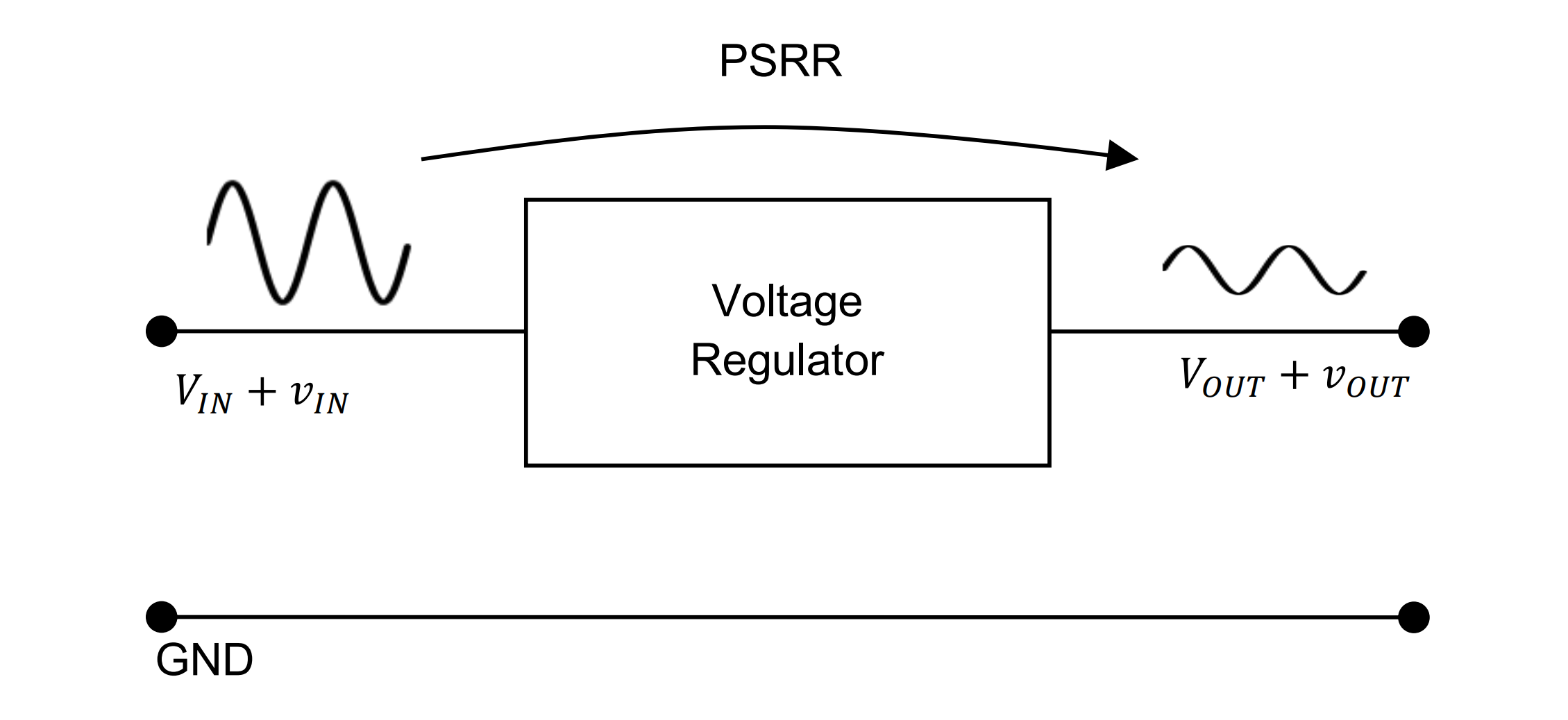

** PSRR的測試**

測試原理圖如下所示:

測試步驟:

a.開關管K4置地(或規定的參考電壓),只要保證地或參考電壓具有很低的噪聲即可;

b.開關K置“1”,在輔助放大器A的輸出端測得電壓VL8;

c.開關管置“2”(即正負電源電壓同時增加ΔV),在輔助放大器A的輸出端測得電壓VL9;

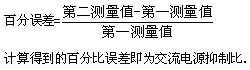

d.由bc可以計算求出PSRR:

注:PSRR不可能為無窮大(一般為40dB~80dB),與運放差分輸入管的不完全匹配有極大關系。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

放大器

+關注

關注

146文章

14345瀏覽量

222068 -

電源電壓

+關注

關注

3文章

1260瀏覽量

26395 -

電源抑制比

+關注

關注

0文章

78瀏覽量

14152 -

PSRR

+關注

關注

0文章

226瀏覽量

40748 -

直流電壓源

+關注

關注

1文章

29瀏覽量

10165

發布評論請先 登錄

相關推薦

熱點推薦

一文詳解LDO的電源抑制比

低壓差線性穩壓器(LDO)相比 DC-DC 的優點之一,是輸出電壓紋波小。但是高速電路下,LDO 的電源抑制比(PSRR)也是不可忽略的因素

發表于 08-30 17:09

?2.7w次閱讀

運算放大器電源抑制比(PSRR)與電源電壓

如果運算放大器的電源發生變化,輸出不應變化,但實際上通常會發生變化。如果X V的電源電壓變化產生Y V的輸出電壓變化,則該電源的PSRR(折合到輸出端)為X/Y。無量綱

發表于 11-06 09:02

電源電壓抑制比(PSRR)是什么意思

如果運算放大器的電源發生變化,輸出不應變化,但實際上通常會發生變化。如果X V的電源電壓變化產生Y V的輸出電壓變化,則該電源的PSRR(折合到輸出端)為X/Y。無量綱

發表于 12-27 08:15

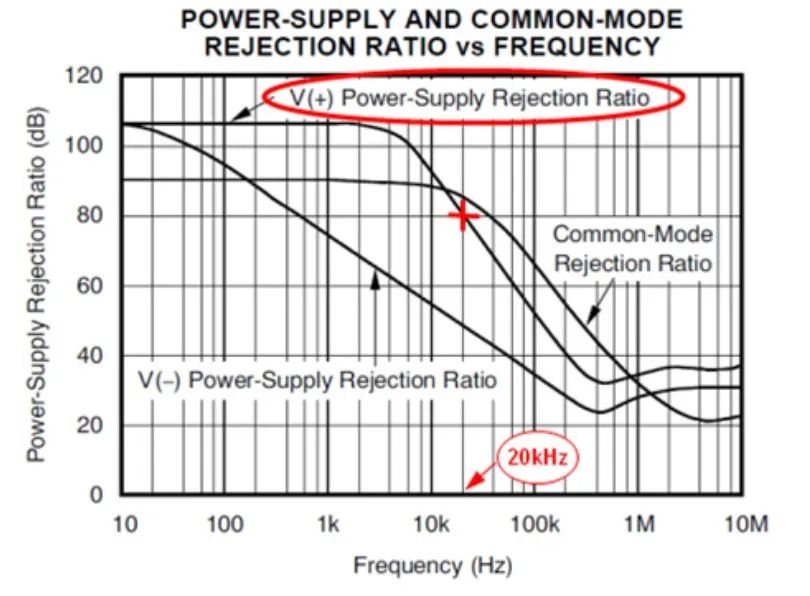

共模抑制比CMRR與電源抑制比PSRR相關介紹

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejecti

發表于 12-27 07:24

電源抑制比(PSRR)

電源抑制比(PSRR)

對于高質量的D/A轉換器,要求開關電路及運算放大器所用的電源電壓發生變化時,對輸出的電壓影響極小.通常把滿量程電壓

發表于 12-26 10:04

?2365次閱讀

電源抑制比(PSRR )

如果運算放大器的電源發生變化,輸出不應變化,但實際上通常會發生變化。如果X V的電源電壓變化產生Y V的輸出電壓變化,則該電源的PSRR(折合到輸出端)為X/Y。無量綱

發表于 01-05 14:11

?11次下載

共模抑制比CMRR與電源抑制比PSRR的仿真原理

共模抑制比(CMRR:comon-mode-rejection-ratio)和電源抑制比(PSRR:power-supply-rejecti

發表于 01-05 14:22

?6次下載

什么是電源抑制比(PSRR)

原文鏈接: http://www.3532n.com/baike/bandaoti/jichuzhishi/20100309184356.html電源抑制比電源

發表于 01-11 10:05

?8次下載

什么是共模抑制比CMRR?什么是電源抑制比PSRR?

什么是共模抑制比CMRR?什么是電源抑制比PSRR? 共模抑制比(common mode rej

什么是電源抑制比(PSRR)?它有哪些作用和應用?

在電子設備和系統的設計中,電源抑制比(Power Supply Rejection Ratio,簡稱PSRR)是一個至關重要的參數。它描述了電子設備或系統對來自

電源抑制比DC-PSRR測試

電源抑制比DC-PSRR測試

評論