在層次化的設(shè)計(jì)當(dāng)中,我們常常將復(fù)雜電路系統(tǒng)進(jìn)行功能模塊劃分,先設(shè)計(jì)各個(gè)子功能模塊電路,然后再在頂層模塊中通過(guò)實(shí)例化這些子模塊,并通過(guò)各個(gè)子模塊的輸入輸出端口進(jìn)行模塊間的互聯(lián),來(lái)實(shí)現(xiàn)復(fù)雜電路設(shè)計(jì)。

在這里,為了說(shuō)明實(shí)例化的方法,我使用了一個(gè)簡(jiǎn)單的門(mén)電路的例子,幫助大家理解和掌握。當(dāng)然,在實(shí)際當(dāng)中我們是不會(huì)去這樣去進(jìn)行設(shè)計(jì)的,當(dāng)有了這樣的邏輯表達(dá)式,我們僅使用一條assign語(yǔ)句就可以實(shí)現(xiàn)設(shè)計(jì)了。這里僅僅是給大家演示實(shí)例化的方法。

0****1系統(tǒng)模塊劃分

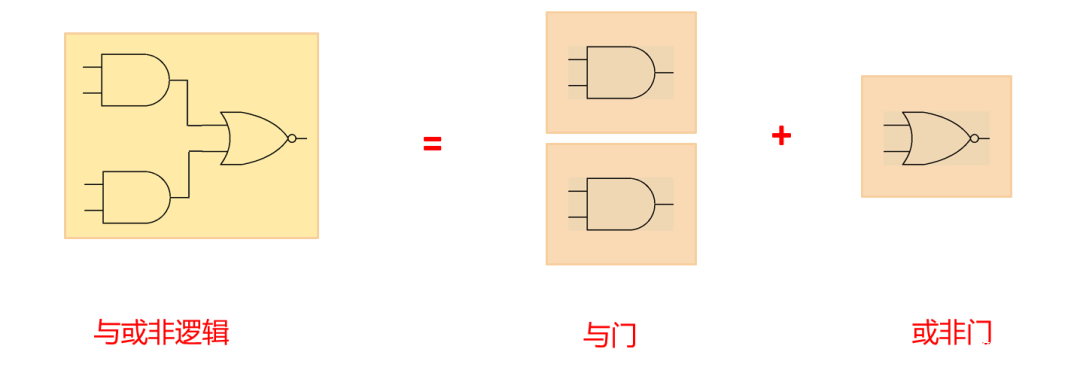

要實(shí)現(xiàn)一個(gè)與或非邏輯的電路,可以先將這個(gè)電路進(jìn)行模塊劃分,根據(jù)功能劃分為與門(mén)和或非門(mén),如下圖所示。

△ 與或非門(mén)模塊劃分

0****2子模塊設(shè)計(jì)

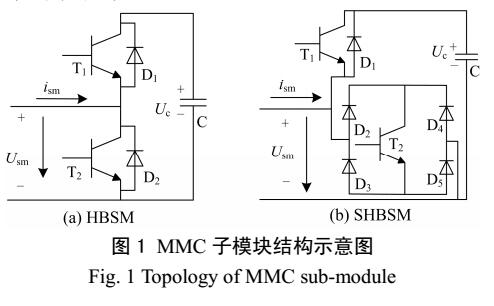

模塊劃分好后,分別對(duì)與門(mén)和或非門(mén)進(jìn)行獨(dú)立設(shè)計(jì)。在這里,我們可以將子功能模塊看作一個(gè)電路或者一個(gè)具有一定功能的芯片,我們現(xiàn)在要對(duì)這個(gè)芯片進(jìn)行設(shè)計(jì)。設(shè)計(jì)包括模塊名稱、端口聲明,電路功能描述。

△ 子功能模塊設(shè)計(jì)

03頂層模塊搭建

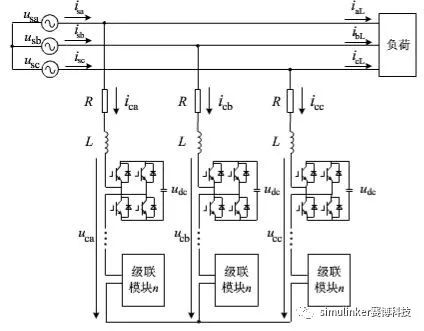

子模塊設(shè)計(jì)好后,我們需要再新建一個(gè)源程序.v文件作為頂層文件,并進(jìn)行頂層模塊的設(shè)計(jì)。頂層模塊的端口就是最終整個(gè)電路的端口。與或非門(mén)有四個(gè)輸入端口,分別是A、B、C和D,輸出端口是L。

**規(guī)則:**頂層模塊中只出現(xiàn)模塊的實(shí)例化,不要有assign或always等功能描述語(yǔ)句。

接下來(lái),我們要將設(shè)計(jì)的子模塊實(shí)例化到頂層文件中。這個(gè)過(guò)程就好像將一個(gè)個(gè)帶引腳的芯片,用導(dǎo)線將他們的引腳根據(jù)輸入輸出關(guān)系進(jìn)行連接,形成最終的數(shù)字電路系統(tǒng)。

模塊實(shí)例化中信號(hào)與模塊端口的接方式有兩種,位置對(duì)應(yīng)方式和名稱對(duì)應(yīng)方式。

(1)位置對(duì)應(yīng)方式

實(shí)例化模塊時(shí),上層模塊的信號(hào)必須嚴(yán)格按照低層模塊端口聲明的順序一一對(duì)應(yīng)連接。例如本示例中可以這樣寫(xiě):

my_AND U1 (A, B, c1);

my_AND U2 (C, D, c2);

my_NOR U3 (c1, c2, L);

(2)名稱對(duì)應(yīng)方式(推薦)

實(shí)例化模塊時(shí),使用端口名稱進(jìn)行連接,使用“.”符號(hào)標(biāo)明原模塊定義的端口,其后所跟括號(hào)中為與之相連接的信號(hào)名,如下圖所示,即為名稱對(duì)應(yīng)方式的寫(xiě)法。此方式不需要按順序排列。

△ 頂層模塊設(shè)計(jì)

my_AND是子模塊的模塊名,實(shí)例化后的實(shí)例需要一個(gè)名稱來(lái)唯一指定該器件,例如這里的U1、U2和U3。a、b、c是原子模塊中定義的端口名稱,括號(hào)中是在頂層模塊中所要連接的端口。

模塊內(nèi)部信號(hào),要聲明為wire型,如這里的c1和c2。

總結(jié)一下,在設(shè)計(jì)之初,我們需要將電路系統(tǒng)進(jìn)行模塊劃分,然后進(jìn)行子模塊設(shè)計(jì),具有相同功能和端口的電路,只需要設(shè)計(jì)一次,然后在頂層模塊中進(jìn)行子模塊的實(shí)例化,每個(gè)實(shí)例都有獨(dú)一無(wú)二的實(shí)例名,因?yàn)樗麑?duì)應(yīng)的實(shí)實(shí)在在的電路,在對(duì)相同的模塊進(jìn)行實(shí)例化時(shí),實(shí)例化幾次就產(chǎn)生幾個(gè)相同的電路,由實(shí)例名唯一指定。最后通過(guò)端口和信號(hào)線將子模塊的輸入輸出根據(jù)邏輯關(guān)系進(jìn)行連接。

04自頂向下的設(shè)計(jì)

自頂向下是一種設(shè)計(jì)思想,是解決復(fù)雜問(wèn)題的有效方法。在數(shù)字系統(tǒng)設(shè)計(jì)中,設(shè)計(jì)者要先從整個(gè)系統(tǒng)的功能和結(jié)構(gòu)出發(fā),先進(jìn)行最上層的設(shè)計(jì)。例如,與或非門(mén)設(shè)計(jì)示例中,我們先設(shè)計(jì)整個(gè)系統(tǒng)的模塊名,輸入、輸出端口。

接下來(lái),將系統(tǒng)分成若干個(gè)子系統(tǒng),每個(gè)子系統(tǒng)分成若干功能模塊,模塊還可以繼續(xù)向下劃分成子模塊,直至分成許多最基本的數(shù)字功能電路。

在自頂向下的設(shè)計(jì)中,我們可以先逐級(jí)設(shè)計(jì)每一層次中各個(gè)子系統(tǒng)或子模塊的輸入、輸出端口,以及模塊之間的連接關(guān)系。根據(jù)設(shè)計(jì)可以在在頂層模塊中,將各個(gè)子系統(tǒng)通過(guò)實(shí)例化進(jìn)行連接。此時(shí),可以不必關(guān)心模塊具體是如何實(shí)現(xiàn)的,底層模塊的具體設(shè)計(jì)可以放在最后去完成。

也就是說(shuō),實(shí)際上,上述“ 02子模塊設(shè)計(jì)” 與“ 03頂層模塊的搭建 ”兩部分的順序應(yīng)該顛倒一下,先從全局視角進(jìn)行頂層模塊的設(shè)計(jì)與搭建,最終再進(jìn)行子模塊功能設(shè)計(jì)。

而最終的系統(tǒng)設(shè)計(jì)與驗(yàn)證,則是一個(gè)自底向下的過(guò)程。先完成每個(gè)底層模塊的設(shè)計(jì)與驗(yàn)證,再一步步逐級(jí)向上進(jìn)行驗(yàn)證,直至整個(gè)系統(tǒng)正常運(yùn)行。

-

邏輯電路

+關(guān)注

關(guān)注

13文章

503瀏覽量

44126 -

連接器

+關(guān)注

關(guān)注

104文章

16157瀏覽量

147227

發(fā)布評(píng)論請(qǐng)先 登錄

verilog模塊的調(diào)用、任務(wù)和函數(shù)

【FPGA】UART頂層模塊的子模塊實(shí)例化

汽車電子模塊常用接口電路

電子模塊總規(guī)范標(biāo)準(zhǔn)

汽車電子模塊常用接口電路

車載信息娛樂(lè)系統(tǒng)IO端口和電子模塊的電路保護(hù)注意事項(xiàng)

CPU卡水表電子模塊的實(shí)現(xiàn)

新型MMC子模塊及其混合拓?fù)?/a>

汽車電子模塊常用不同類型的接口電路實(shí)例

Verilog快速掌握之模塊例化資源下載

MMC全橋子模塊電磁暫態(tài)快速模型建模

電子模塊用的電源設(shè)計(jì)

系統(tǒng)模塊與子模塊的實(shí)例化設(shè)計(jì)

系統(tǒng)模塊與子模塊的實(shí)例化設(shè)計(jì)

評(píng)論