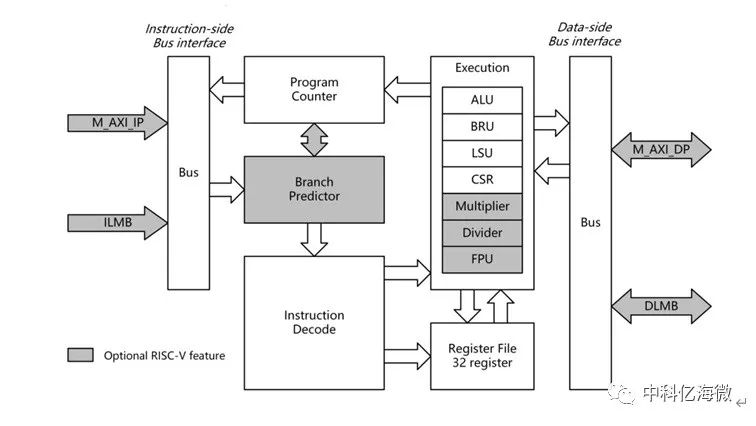

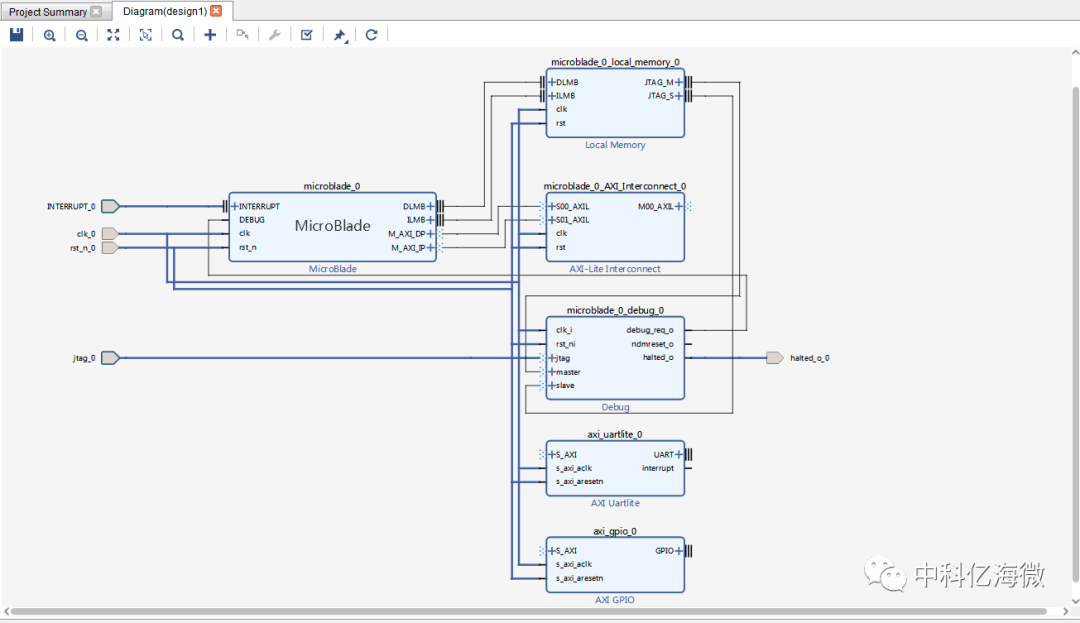

MicroBlade 處理器軟核 IP是實現(xiàn)基于 RISC-V(Reduced Instruction Set Computer,精簡指令集計算機)指令集架構(gòu)的 32 位處理器軟核,支持 RV32IM 指令集,支持 AXI4-Lite 接口,用于簡化 FPGA 中復雜的控制邏輯。MicroBlade 處理器軟核框架如下圖所示:

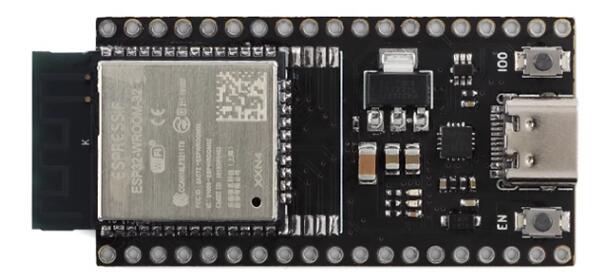

MicroBlade 串口設計,開發(fā)板實現(xiàn)使用的是億海神針系列EQ6HL45型FPGA。本篇通過原理圖設計,學習MicroBlade基本結(jié)構(gòu),通過創(chuàng)建簡單的MicroBlade工程,實現(xiàn)MicroBlade調(diào)用AXI Uartlite模塊和AXI GPIO模塊,完成串口打印功能,掌握在模塊化設計中,MicroBlade最小系統(tǒng)的組成,學會導出、建立以及運行基于SDK的工程。

設計原理

本系統(tǒng)中的MicroBlade模塊通過AXI Lite總線與AXI Uartlite IP和AXI GPIO IP進行通信,完成led指示燈的狀態(tài)改變以及串口打印功能。

操作步驟

基于GUI界面創(chuàng)建工程

1

創(chuàng)建新的工程項目

1)雙擊桌面圖標打開eLinx3.0;2)點擊Create Project,或者單擊File>New Project創(chuàng)建工程文件;3)將新的工程項目命名TEST_MICROBLADE,選擇工程保存路徑,勾選Create project subdirectory,創(chuàng)建一個新的工程文件夾,點擊Next繼續(xù);4)選擇新建一個RTL工程,由于本工程無需創(chuàng)建源文件,故將Do not specify sources at this time(不指定添加源文件)勾選上。點擊 Next繼續(xù);5)選擇目標FPGA器件:Family:eHiChip6 Package:CSG324Available devices: EQ6HL456)最后在新工程總結(jié)中,檢查工程創(chuàng)建是否有誤。沒有問題,則點擊Finish,完成新工程的創(chuàng)建。

2

創(chuàng)建原理圖,添加IP,進行原理圖設計

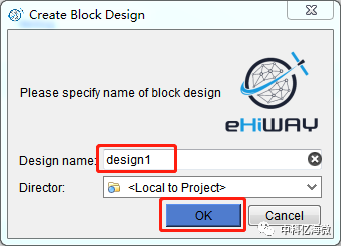

1)在Flow Navigator下,展開IP INTEGRATOR,選擇Create Block Design創(chuàng)建新的原理圖設計;2)將新的設計命名為design1;

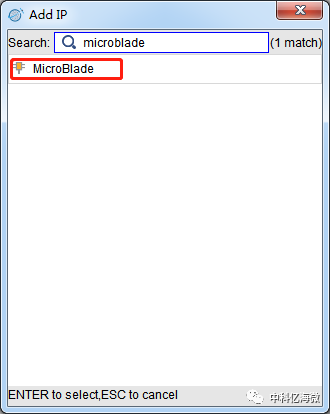

3)在Diagram中添加MicroBlade IP;

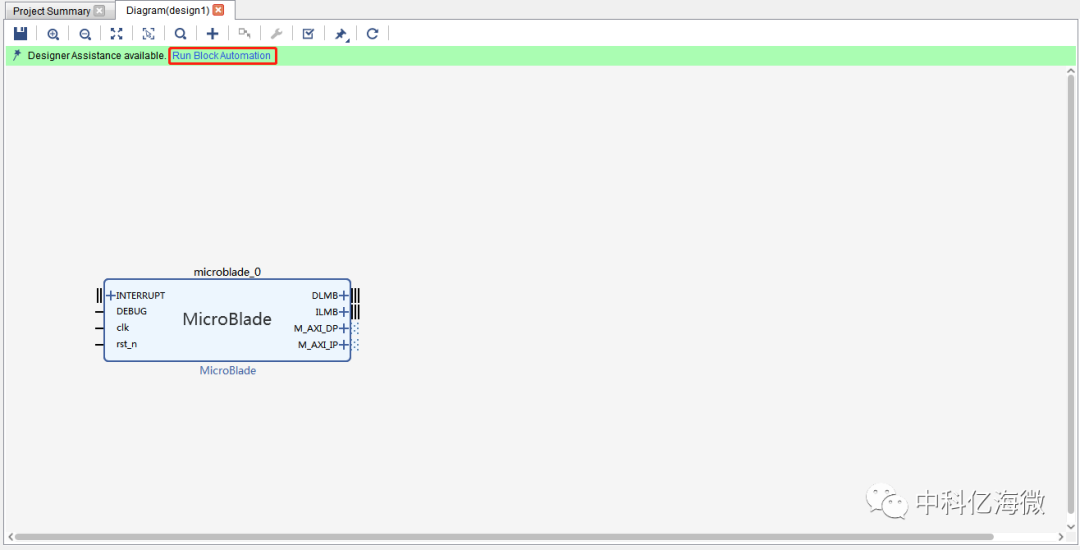

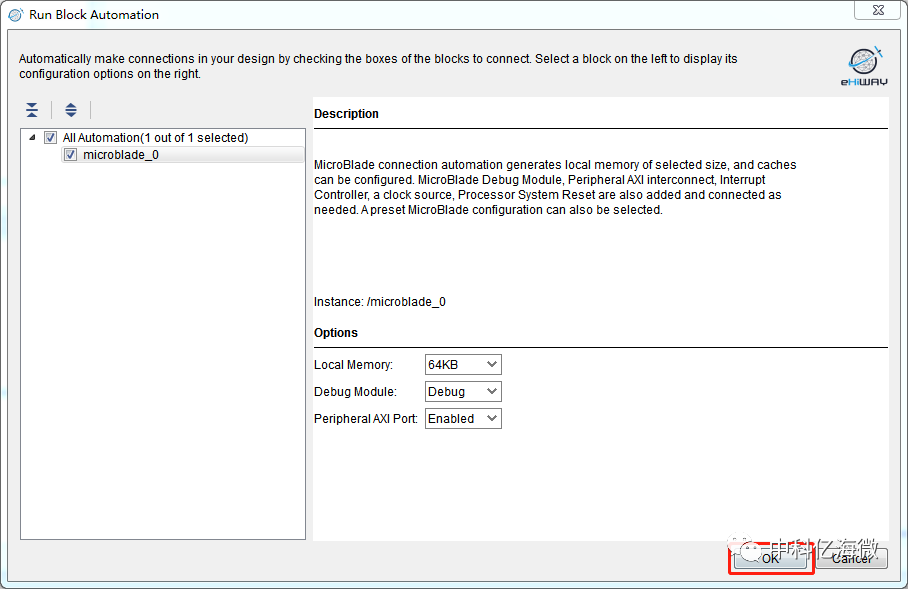

4)添加完成后如下圖所示,點擊Run Block Automation;

5) 在彈出窗口中,使用以下設置替換默認設置:

Local Memory: 64KB

Debug Module: Debug

Peripheral AXI Port: Enabled

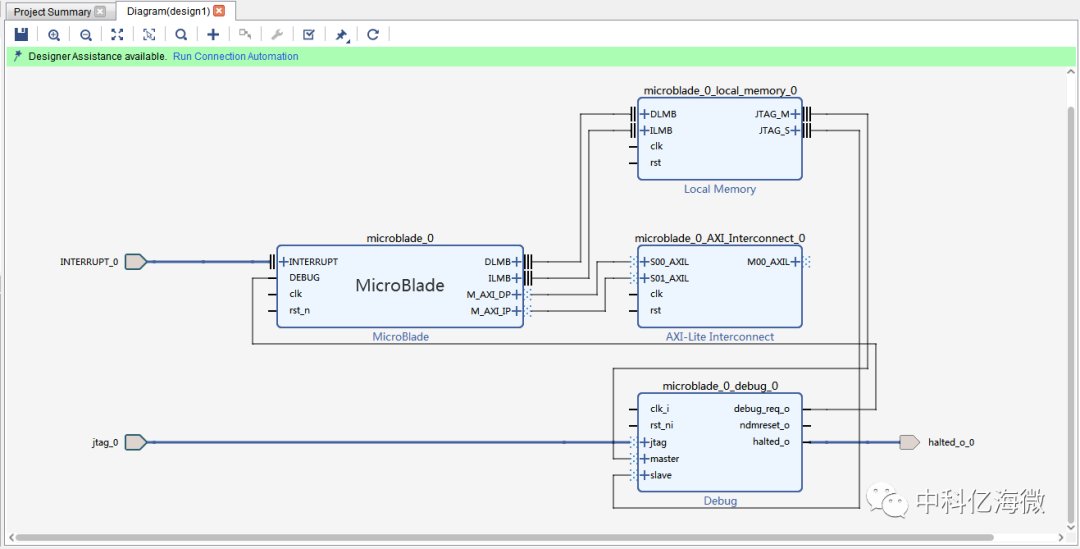

6)完成之后,eLinx會基于之前的設置自動生成一些額外的IP,并且會自動連接完畢,此時不要點擊Run Connection Automation;

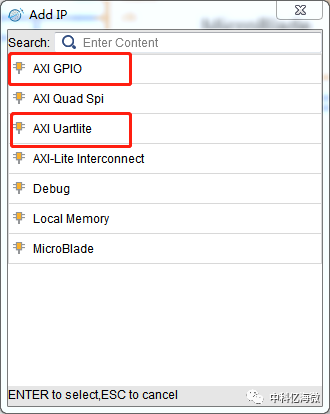

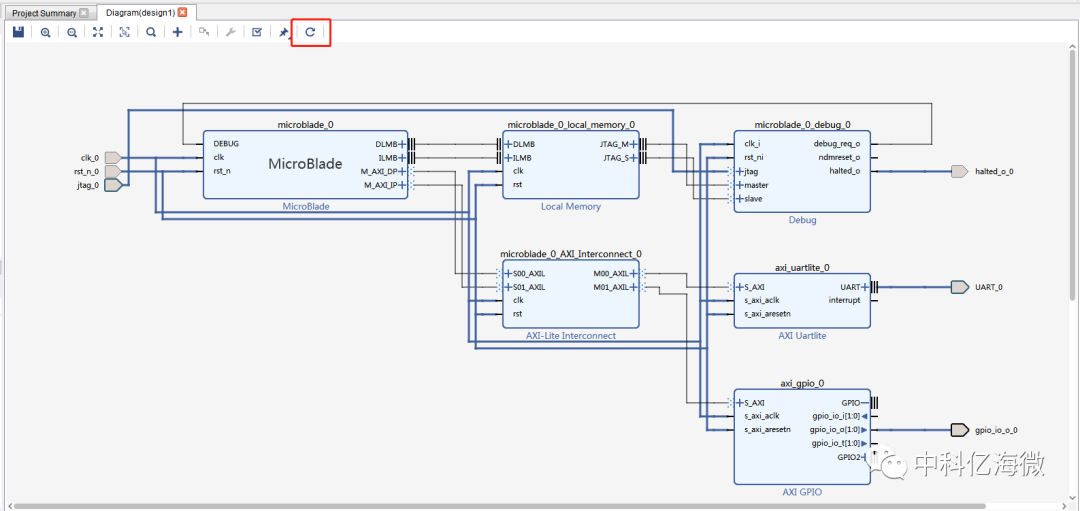

7)在Diagram中添加AXI Uartlite IP和AXI GPIO IP;

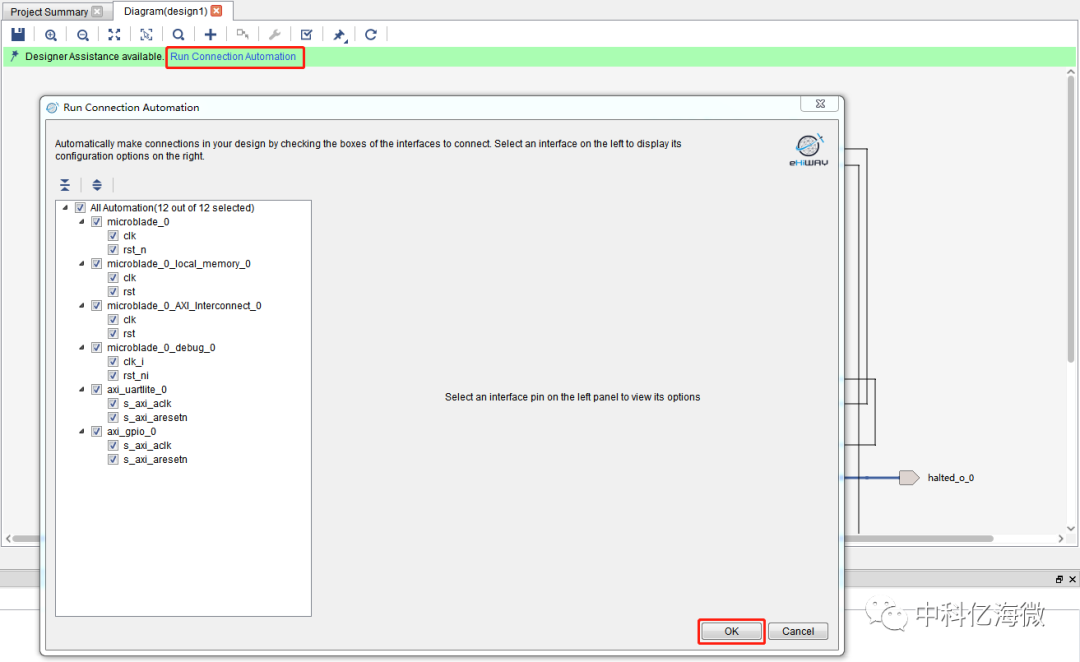

8)完成后,點擊Run Connection Automation,在彈出窗口中勾選所有端口,點擊OK繼續(xù);

9)完成后,雙擊MicroBlade IP,打開界面,取消勾選Enable Interrupt隱藏Interrupt端口;10)雙擊AXI_Lite Interconnect IP,打開界面,把master端口的數(shù)量修改為2。手動完成AXI_Lite Interconnect IP與AXI Uartlite IP,與AXI GPIO IP的連線; 11)雙擊AXI Uartlite IP,打開界面,把AXI CLK Frequency修改為50(板卡晶振為50M)。單擊UART端口,引出外設IO;12)雙擊AXI GPIO IP,打開界面,把GPIO通道GPIO Width修改為2,勾選Enable Dual Channel,把GPIO2通道GPIO Width修改為1。點擊展開GPIO端口,點擊gpio_io_o端口,引出外設IO;13)完成后,點擊布局重置按鈕重新布局,如下圖所示:

14)Ctrl+S保存設計。

3

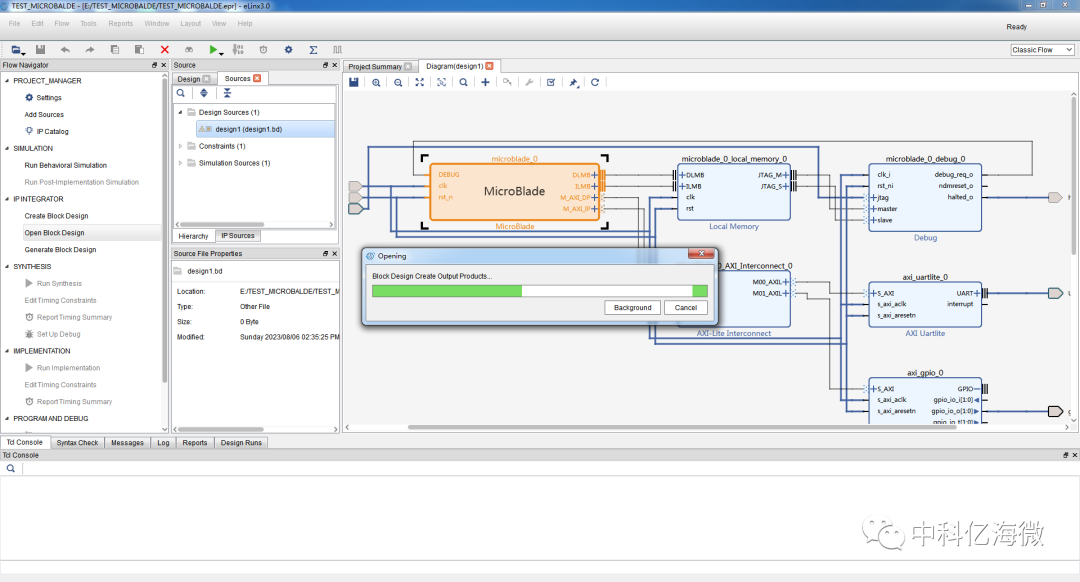

綜合、實現(xiàn)、生成比特流文件

1)保存后,在Sources窗格中鼠標右鍵design1,選擇Generate Output Products...,開始BD工程綜合,如下圖所示:

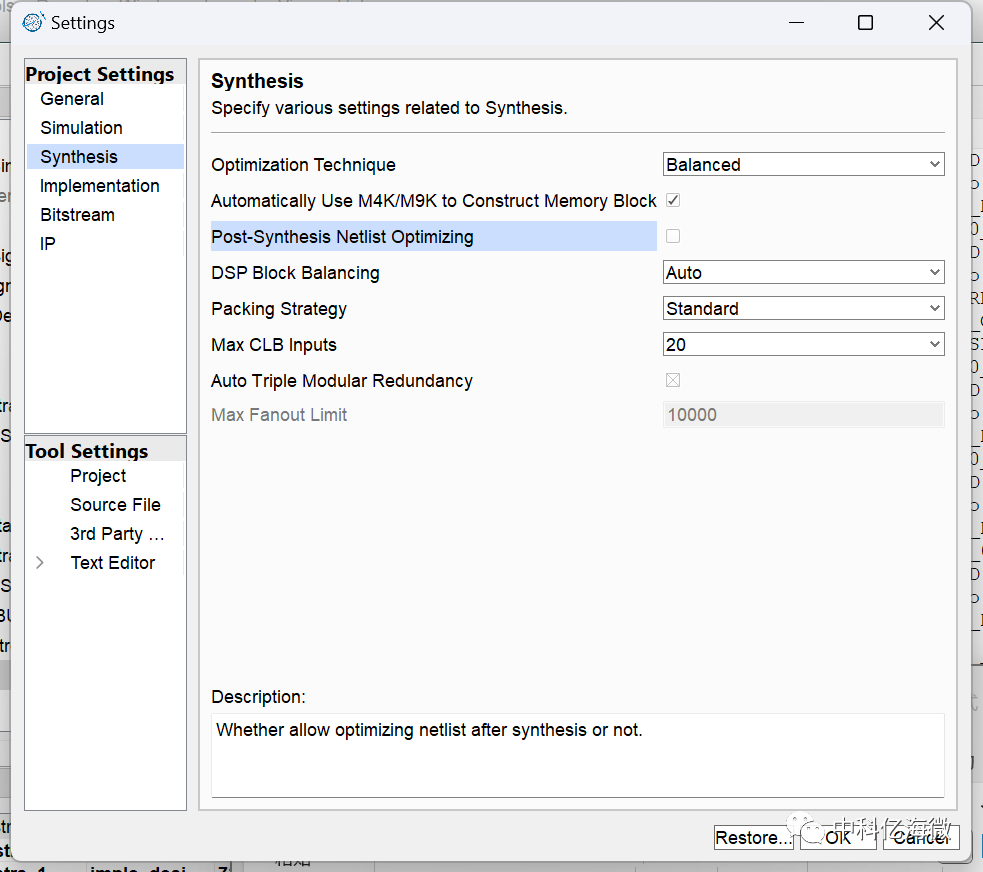

2)在Sources窗格中BD文件點擊右鍵,選擇Create HDL Wrapper,自動更新Sources列表,同時工程沒有頂層,則自動設置為頂層;3)在界面上方工具欄中,選擇Toos>Settings…在彈出的界面中點擊Synthesis欄,取消勾選Post_Synthesis Netlist Optimizing;

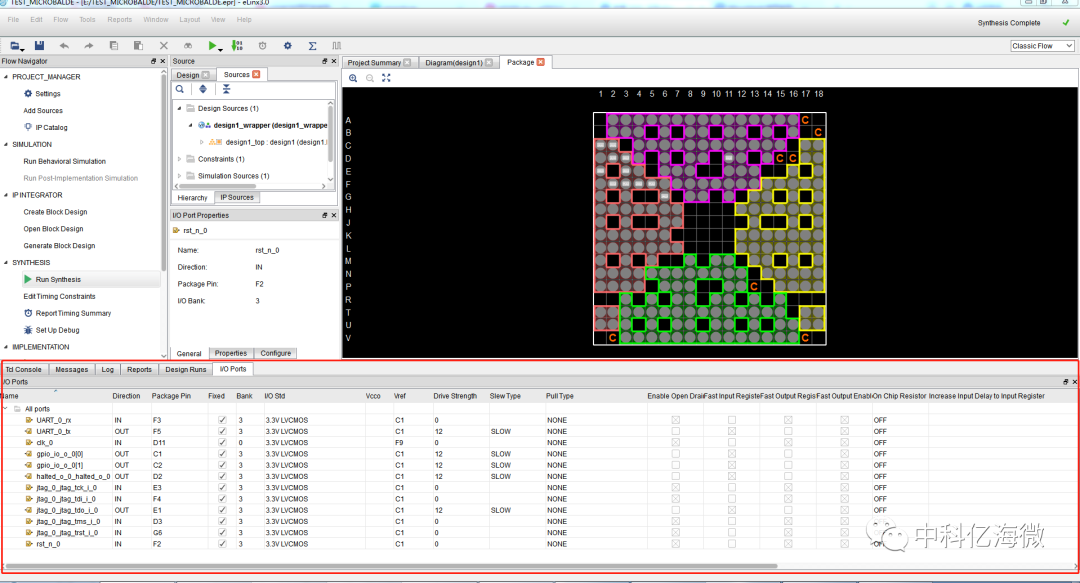

4)完成后繼續(xù)點擊Flow Navigator中的SYNTHESIS欄中的Run Synthesis進行工程綜合;5)綜合結(jié)束后在界面上方工具欄中,選擇Toos >I/O Planning編輯管腳指定;

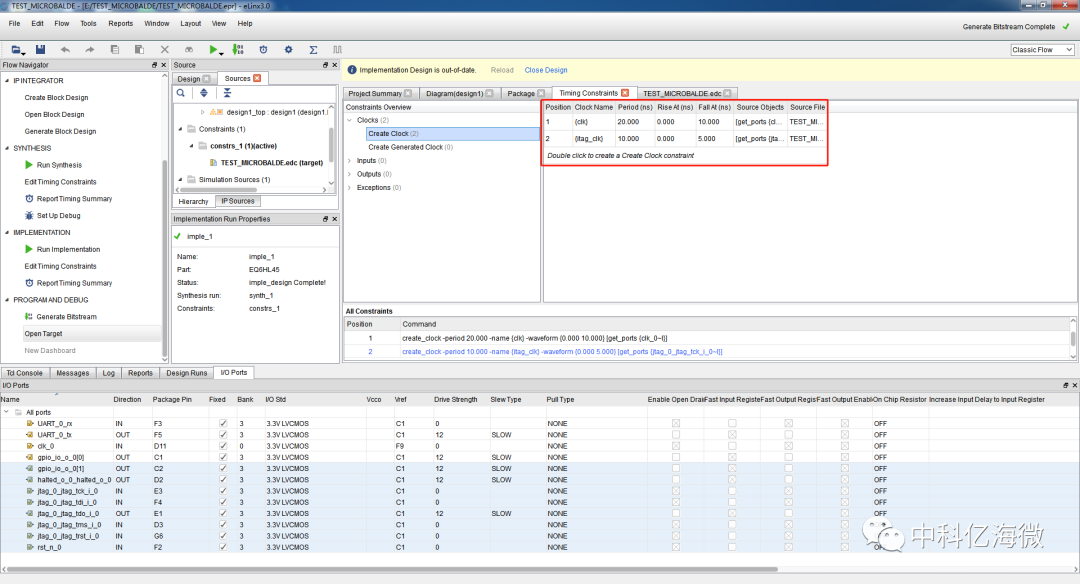

6)完成后在SYNTHESIS欄中點擊Edit Timing Constraints添加2個時序約束后保存;

7)完成后繼續(xù)點擊左側(cè)Run Implemenation按鈕進行布局布線編譯實現(xiàn);8)在PROGRAM AND DEBUG欄點擊Generate Bitstream。連接開發(fā)板,完成后點擊Open target啟動Programmer下載碼流。下載成功后默認狀態(tài)為led1和led2交替閃爍。

4

導出SDK并啟動

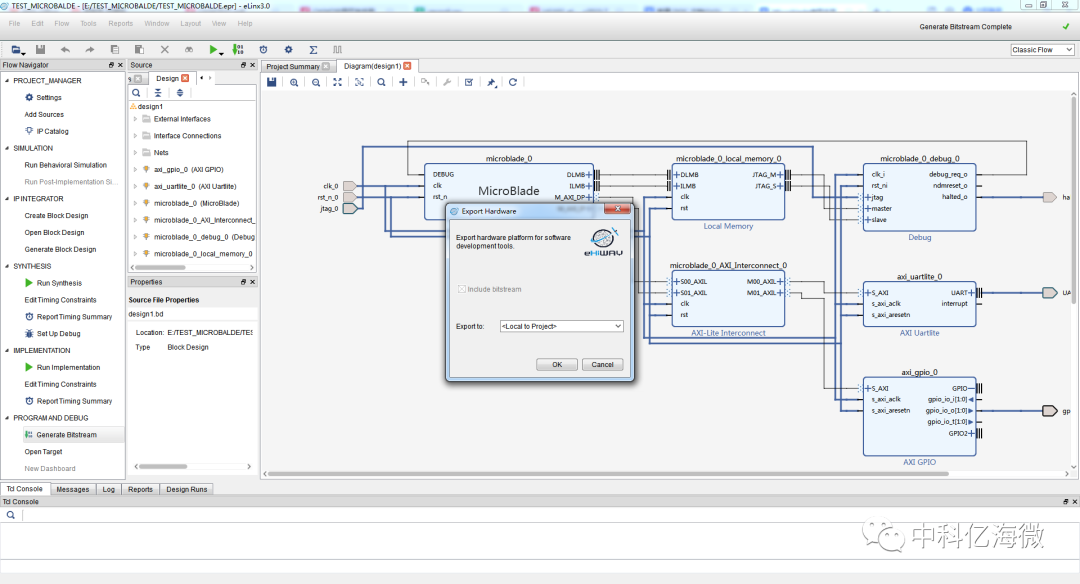

1)在頂部工具欄中,選擇File>Export>Export Hardware導出硬件工程到SDK;

2)在工具欄中,選擇File>Launch SDK,使用默認工程,啟動SDK;

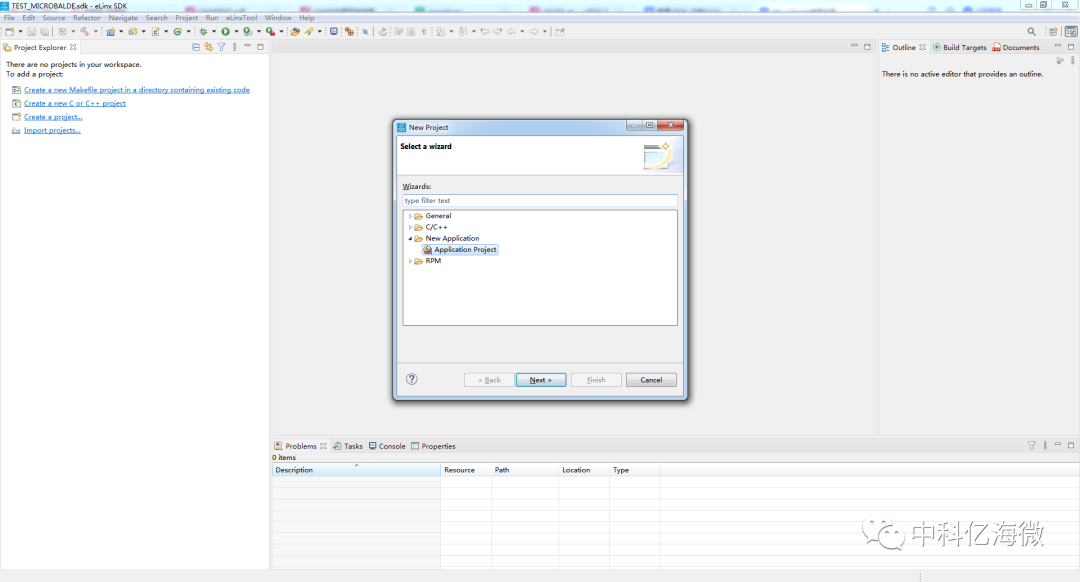

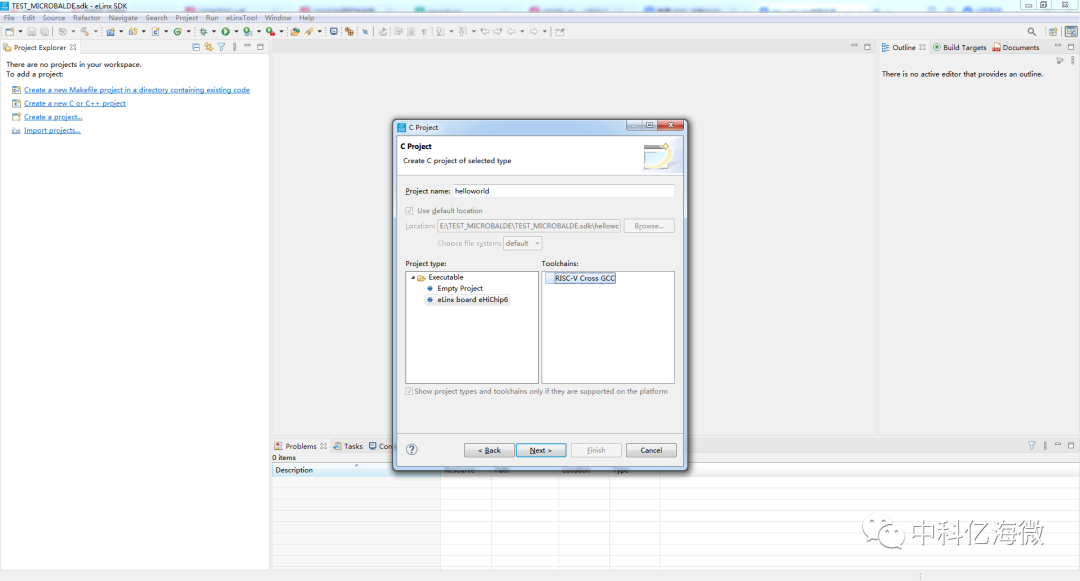

3)啟動SDK后,如下界面,點擊Create a project,彈出如下界面:

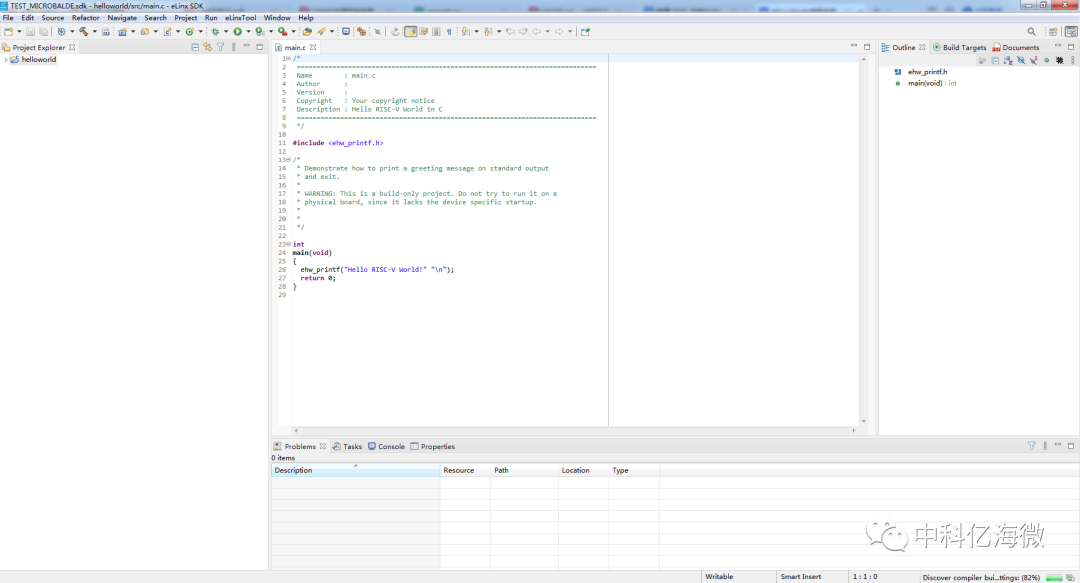

4)選擇New Application->Application project,輸入工程名helloworld,依次默認配置點擊Finish完成創(chuàng)建;

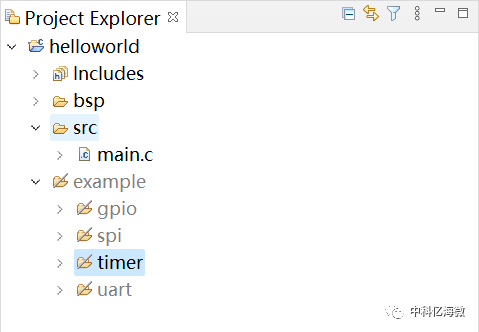

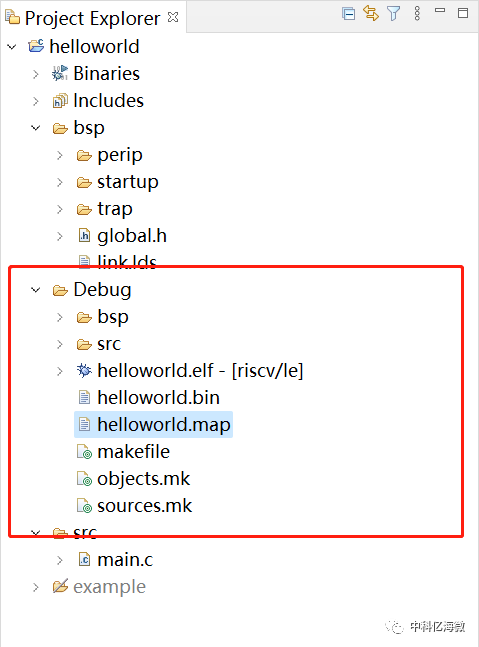

5)工程屬性無需配置,工程中集成了例程,如下圖:

6)構(gòu)建。構(gòu)建成功后左側(cè)生成Debug文件夾

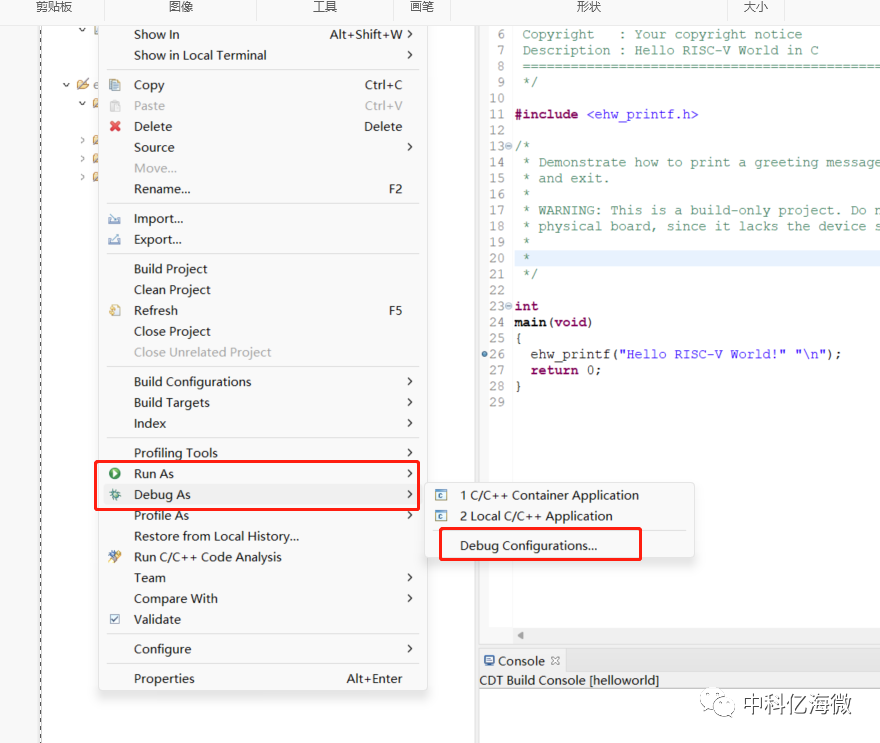

7)進行上板運行a)在工程名稱上點擊右鍵,彈出界面選擇run as

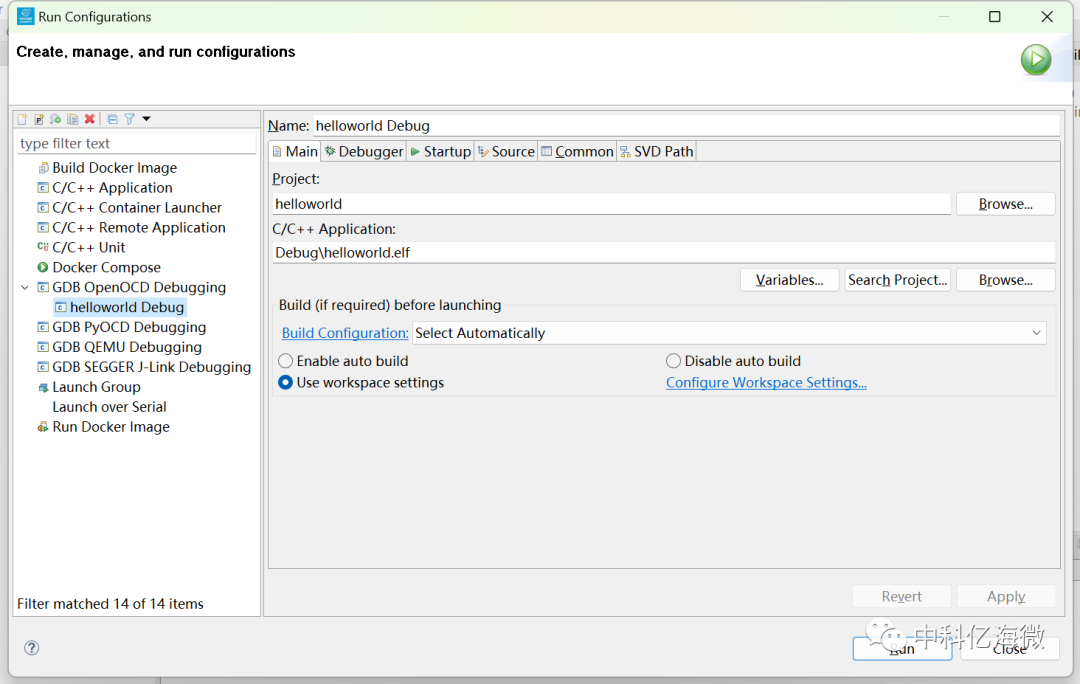

b)點擊后彈出如下界面,在GDB OpenOCD Debugging按鈕雙擊即可

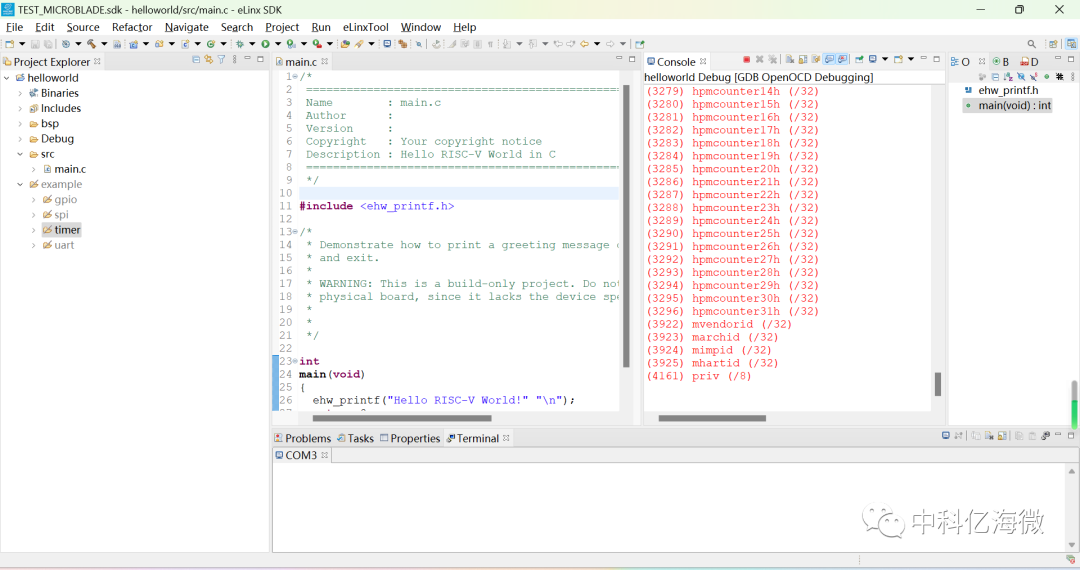

c)完成后,點擊run可開始板卡聯(lián)調(diào),成功如下圖所示:

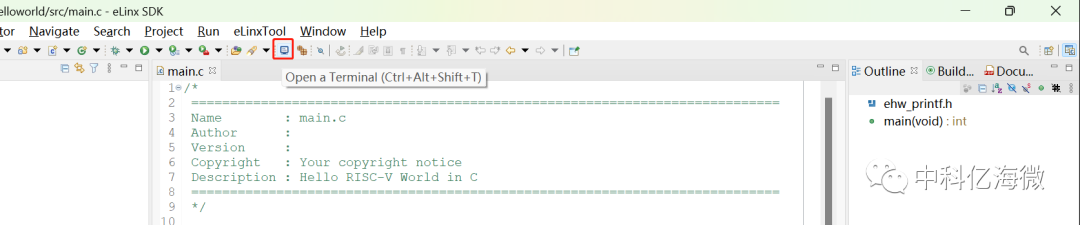

5)連接串口。選擇SDK界面下方的Terminal窗口,點擊下圖的按鈕

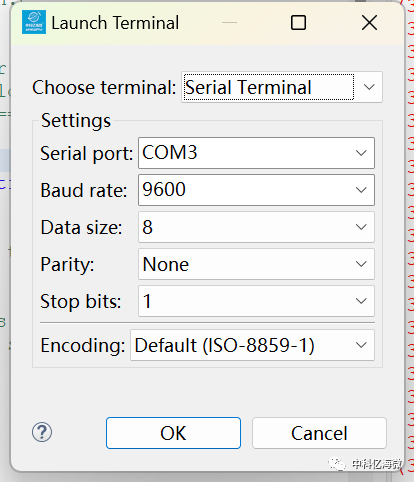

6)在彈出窗口中,進行如下配置:

?

?

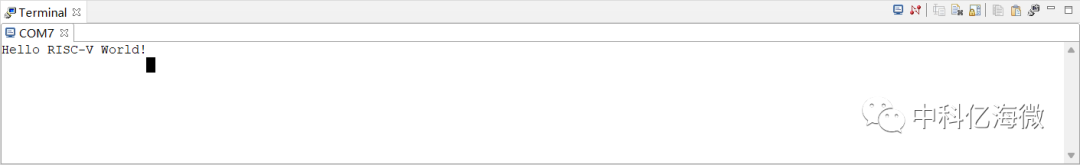

7)點擊OK后,點擊EQ6HL45板卡上的復位按鈕(F2),Terminal界面出現(xiàn)了’Hello RISC-V World’字樣。

-

處理器

+關注

關注

68文章

20255瀏覽量

252290 -

計算機

+關注

關注

19文章

7807瀏覽量

93202 -

IP

+關注

關注

5文章

1863瀏覽量

155844 -

串口

+關注

關注

15文章

1619瀏覽量

82823 -

串口傳輸

+關注

關注

0文章

33瀏覽量

2115

發(fā)布評論請先 登錄

串口協(xié)議的深度剖析

STM32驅(qū)動串口屏,STM32F103C8T6串口發(fā)送指令控制HMI串口屏

RK3588平臺串口配置修改指南:切換至串口8

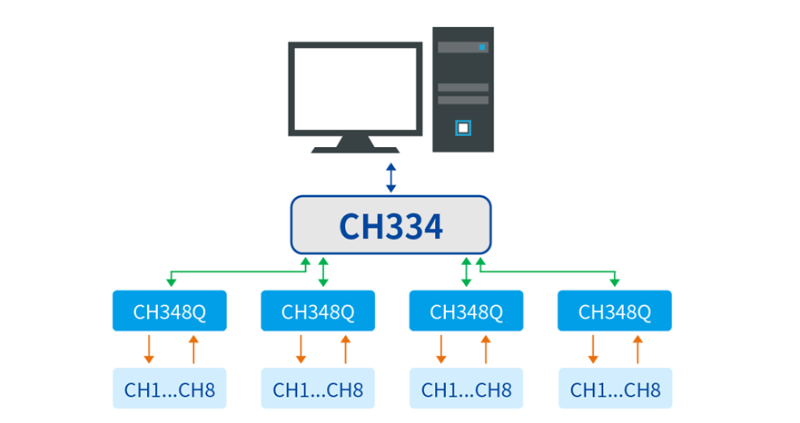

USB轉(zhuǎn)多串口擴展方案詳解

串口調(diào)試步驟(適合免驅(qū)動的232串口設備)

串口服務器產(chǎn)品解析與應用方案選型指南

外部晶振在USB轉(zhuǎn)串口模塊的應用

智嵌物聯(lián)串口轉(zhuǎn)光纖轉(zhuǎn)換器-延長串口通信距離,增強抗干擾性能

ESP32用作經(jīng)典藍牙串口透傳模塊與手機進行串口通信

串口網(wǎng)關是什么

第七章 串口通信

如何選擇國產(chǎn)串口屏

MicroBlade 串口設計

MicroBlade 串口設計

評論