PCI-Express,簡稱“PCI-e”是一種高速串行計算機擴展總線標準,PCI-E屬于高速串行點對點雙通道高帶寬傳輸,所連接的設備分配獨享通道帶寬,不共享總線帶寬,它的主要優勢就是數據傳輸速率高。

PCI-E2.0和PCI-E3.0主要存在以下不同:

1)最大數據率不同:PCI-E 2.0只能提供5GT/S的最大數據率,而PCI-E 3.0的數據傳輸率則達到了8GT/S,提高了總線帶寬。PCI-E 3.0規范將數據傳輸率提升到8GT/S,并且保持了對PCI-E 2.x/1.x的向下兼容,繼續支持2.5T/S、5T/S信號機制。

2)編碼方式不同:PCI Express 3.0工作在8T/S頻率上,取消了傳統的8b/10b編碼,它將引入包括信號強化(enhanced signaling)、數據完整性(data integrity)、傳輸接收均衡、PLL改善、時脈數據恢復和通用擴展等多項技術。

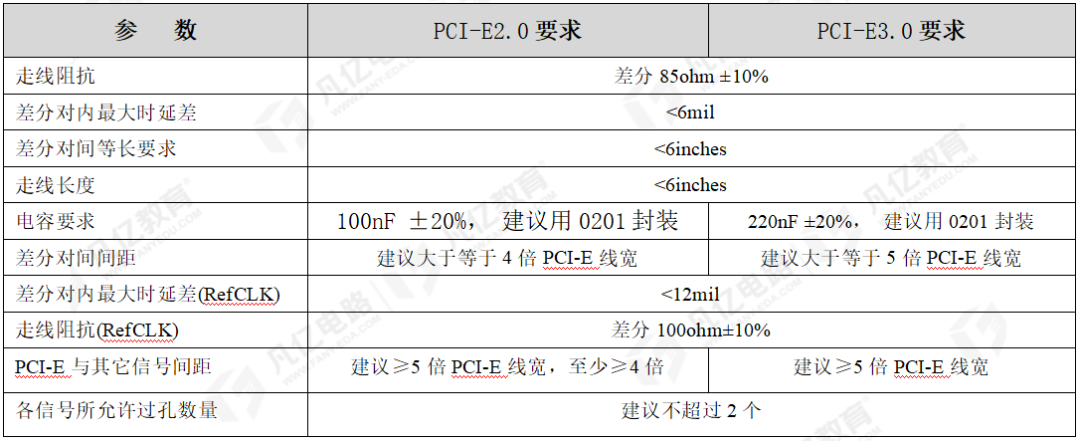

針對PCI-E2.0和PCI-E3.0的不同特點,對應也有不同的PCB設計要求。

表1 PCI-E接口的PCB設計要求

建議在 BGA 區域的以下位置加地通孔,并建議差分信號作包地處理,包地線的地孔間隔小于300mil。如圖1所示。

圖1 PCIe3.0 BGA 區域扇出走線

聲明: 本文凡億教育原創文章,轉載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207-

pcb

+關注

關注

4405文章

23878瀏覽量

424351

原文標題:PCIe接口的PCB布局布線要求

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

深入探討PCB布局布線的專業設計要點與常見挑戰

基于Molex NearStack PCIe連接器系統的技術分析文章

PCB布局布線的相關基本原理和設計技巧

嵌入式接口通識知識之PCIe接口

高速接口布局指南

如何理解芯片設計中的后端布局布線

高速PCB布局/布線的原則

高速PCB板的電源布線設計

如何布線才能降低MDDESD風險?PCB布局的抗干擾設計技巧

PCIe接口的PCB布局布線要求

PCIe接口的PCB布局布線要求

評論