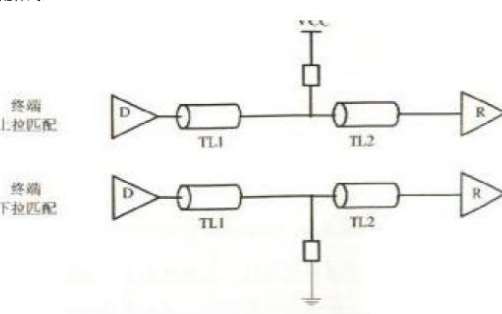

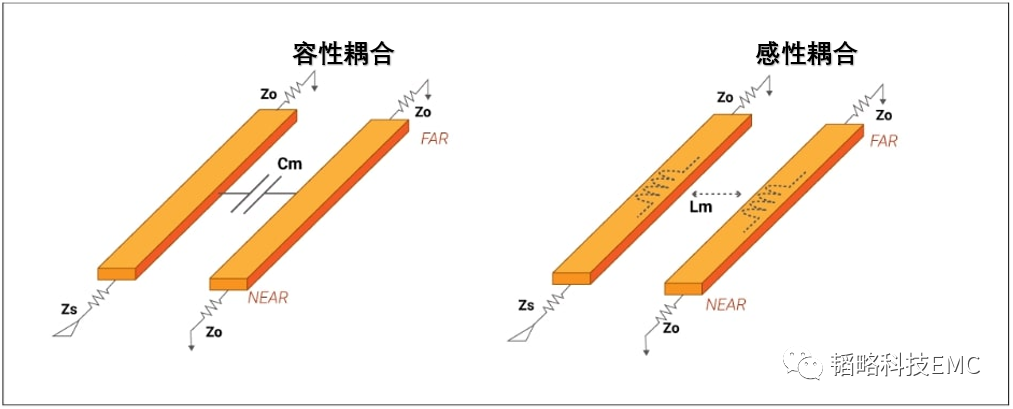

一切煩惱的根源來源于執(zhí)念,串?dāng)_和噪聲則來源于電容兩端電壓差不能突變。串?dāng)_可以定義為一條Net電平變化導(dǎo)致鄰近的net電平的波動(dòng)。這種波動(dòng)可能對(duì)受害Net的時(shí)序帶來變化,甚至可能造成功能的錯(cuò)誤。

在90nm,65nm及更先進(jìn)工藝,串?dāng)_和噪聲的影響越來越嚴(yán)重,主要原因還是在于繞線更密,頻率更高,電壓更低。

串?dāng)_

串?dāng)_是一直困擾著后端和EDA工具的一個(gè)問題。做過先進(jìn)工藝的同仁應(yīng)該深有體會(huì),在Place和CTS階段,時(shí)序已經(jīng)優(yōu)化得不錯(cuò),但是Route之后,引入了Delta Delay,時(shí)序立即惡化,需要通過幾輪Post-Route優(yōu)化才能勉強(qiáng)恢復(fù)到Route之前的狀態(tài),即便如此,功耗和面積也會(huì)有很大犧牲。其原因在于Pre-Route階段不存在真實(shí)的繞線,沒辦法精準(zhǔn)預(yù)估繞線之間串?dāng)_的影響。

隨著機(jī)器算力的快速增長(zhǎng),以及EDA公司在逐漸普及AI技術(shù),老本相信這個(gè)問題應(yīng)該最終會(huì)得到解決,因?yàn)?a href="http://www.3532n.com/tags/ai/" target="_blank">AI的本質(zhì)在于預(yù)測(cè)。通過不斷地學(xué)習(xí),建立在布局階段去預(yù)測(cè)布線之后串?dāng)_的深度學(xué)習(xí)模型,從而能夠在布局階段相對(duì)精準(zhǔn)地預(yù)測(cè)串?dāng)_將會(huì)帶來的影響。或者更簡(jiǎn)單粗暴一點(diǎn),仗著算力夠用,在布局階段就直接用Detail Route Based的Placer引擎。

PT進(jìn)行SI分析需要特別注意以下SI相關(guān)命令是否正確:

...

#使能Crosstalk/SI分析

set si_enable_analysis true

#指定composite aggressor模式

set_app_var si_xtalk_composite_aggr_mode statistical

#指定victim和aggressor窗口對(duì)齊模式

set_app_var si_xtalk_delay_analysis_mode all_path_edges/all_path

...

#確保讀入耦合電容寄生參數(shù)

read_parasitics -keep_capacitive_coupling ...

...

#在timing path中顯示Delta Delay一欄信息

report_timing -crosstalk

窗口

時(shí)序窗口是指信號(hào)在通過不同的路徑到達(dá)某條Net時(shí),時(shí)間上有快有慢,最長(zhǎng)路徑延時(shí)和最短路徑延遲之間的差值就是時(shí)序窗口的大小。如下圖所示中,信號(hào)線A1, A2, A3和V都有各自的時(shí)序窗口。對(duì)于信號(hào)線V來說,A1, A2, A3都與之有重疊窗口(overlapping timing window),而A2和A3之前是沒有重疊窗口的,A1和A3可以認(rèn)為有部分重疊窗口。那么在計(jì)算信號(hào)線V的Delta Delay時(shí),將其分成3個(gè)階段:第1階段,A1和A2同時(shí)對(duì)V造成影響,Delta Delay = 0.12 + 0.14 = 0.26;第2階段,A1對(duì)V造成影響,Delta Delay = 0.14;第3階段,A3對(duì)V造成影響,Delata Delay = 0.23。這種情況下,信號(hào)線V的Delta Delay取最差值0.26。

需要注意的是,上面考慮的Net之間是同步的情況下,如果兩條Net相關(guān)的clock是異步的,處理的方式會(huì)有很大不同。假如是設(shè)成Async,那么計(jì)算Delta Delay采用的是無限時(shí)序窗口,考慮的是最悲觀的可能情況;假如是設(shè)成Logic Exclusive,那么只有在有重疊窗口的情況下才去計(jì)算Delta Delay;假如設(shè)成Physical Exclusive,無需考慮串?dāng)_的影響,不計(jì)算Delta Delay。假如Net相關(guān)的clock設(shè)置成False Path,處理方式和Synchronous相同,所以在設(shè)置Clock異步關(guān)系時(shí)要特別小心。總結(jié)如下表:

CRPR對(duì)Delta Delay的處理

以上圖中Path為例,在Clock Path的公共路徑上如果有串?dāng)_造成的Delta Delay,這一部分Delta Delay會(huì)不會(huì)被CRPR機(jī)制影響,進(jìn)而被取消呢?答案是:在計(jì)算Setup時(shí),Delta Delay不會(huì)被CRPR影響;而在計(jì)算Hold時(shí),Delta Delay會(huì)被CRPR影響。原因在于:

(1)計(jì)算Setup時(shí),Launch Clock和Capture Clock采樣一般發(fā)生在不同的時(shí)鐘沿,所以Aggressor對(duì)兩個(gè)時(shí)鐘沿的影響是不同的,考慮到最差的情況,這部分的Delta Delay不能被取消。

(2)在計(jì)算Hold時(shí),Launch Clock和Capture Clock采樣一般發(fā)生在相同的時(shí)鐘沿,Aggressor對(duì)兩者的影響是一模一樣的,既然在公共路徑上,這一部分Delta Delay是可以通過CRPR機(jī)制取消的。

那么如何降低串?dāng)_的影響呢?從本文闡述可以看出,主要的方法還是隔離,例如Shielding和加大線間距等,另外一種有效的方式就是錯(cuò)開特定走線之間的時(shí)序窗口。

-

EDA工具

+關(guān)注

關(guān)注

5文章

276瀏覽量

34034 -

電容電壓

+關(guān)注

關(guān)注

0文章

79瀏覽量

11828

發(fā)布評(píng)論請(qǐng)先 登錄

解決串擾的設(shè)計(jì)方法

什么是串擾?如何減少串擾?

串擾之耦合的方式

【經(jīng)驗(yàn)分享】系統(tǒng)常用 (電磁兼容)EMC處理方式

如何解決PCB布局中的串擾問題

串擾是怎么引起的 降低串擾有哪些方法

理解串擾Crosstalk

串?dāng)_,窗口以及CRPR對(duì)Delta Delay的處理方式

串?dāng)_,窗口以及CRPR對(duì)Delta Delay的處理方式

評(píng)論