概述

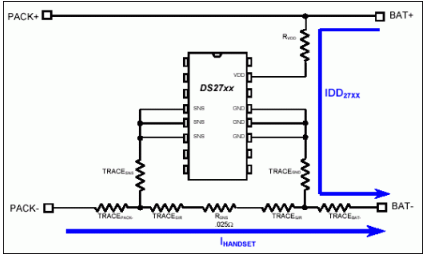

適當(dāng)?shù)碾娐钒宀季謱?duì)于任何庫(kù)倫計(jì)IC的電流測(cè)量精度非常關(guān)鍵。DS2780能夠補(bǔ)償與增益相關(guān)的電流測(cè)量誤差,但不能補(bǔ)償失調(diào)誤差。為確保電流測(cè)量失調(diào)誤差降至最小,本應(yīng)用筆記給出了Dallas Semiconductor推薦的DS2780電路板設(shè)計(jì)準(zhǔn)則。

應(yīng)用電路

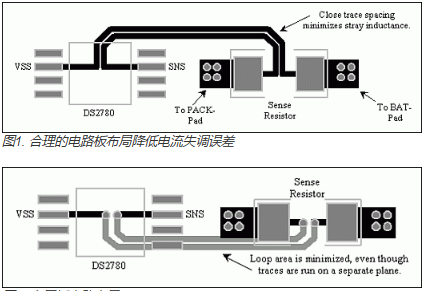

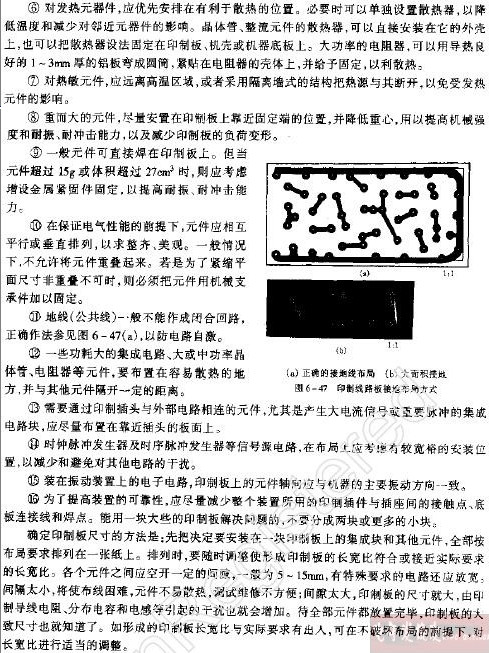

受電池包尺寸的限制,元件通常只能安裝在PCB的一個(gè)層面。另外,較窄的PCB寬度一般限制在TSSOP8封裝范圍內(nèi),如DS2780,需沿著PCB長(zhǎng)度方向安裝元件。這實(shí)際上限制了元件安裝的選擇方案。圖1所示電路給出了SNS和VSS的一個(gè)理想布線方案,檢流電阻應(yīng)該盡可能靠近IC安裝,VSS和SNS之間應(yīng)保持最小的環(huán)路區(qū)域,以降低引線之間的寄生電感。有時(shí),在PCB的單層面上無(wú)法滿足這一設(shè)計(jì)要求,圖2給出了VSS和SNS需要通過(guò)不通電路板層布線時(shí)的最佳布局。如果沒(méi)有很好地限制PCB的寄生電感,A/D失調(diào)誤差將大于數(shù)據(jù)資料中給出的指標(biāo)。

圖2. 多層板電路布局

結(jié)論

DS2780不能調(diào)節(jié)VSS阻抗或VSS寄生電感產(chǎn)生的電流測(cè)量失調(diào)誤差,為盡可能消除這些影響,電路板設(shè)計(jì)中應(yīng)該將VSS和SNS布線之間的環(huán)路間距降到最小。增益誤差可通過(guò)軟件校準(zhǔn),因此,增益精度不需要考慮布線問(wèn)題。

審核編輯:郭婷

-

電路板

+關(guān)注

關(guān)注

140文章

5317瀏覽量

108160 -

電池

+關(guān)注

關(guān)注

85文章

11525瀏覽量

143417 -

PCB

+關(guān)注

關(guān)注

1文章

2308瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

印制線路板設(shè)計(jì)與布局布線(1)

印制線路板設(shè)計(jì)與布局布線(2)

印制線路板設(shè)計(jì)與布局布線(3)

合理的DS2780線路板布局降低電流測(cè)量失調(diào)誤差

存放電池電量計(jì)DS2780參數(shù)-Storing Batter

DS2780電路板布局,最大限度降低電流測(cè)量失調(diào)誤差

具有降低電流測(cè)量失調(diào)誤差的替代DS2740U應(yīng)用電路

DS27xx電量計(jì)電路板布局技巧,實(shí)現(xiàn)測(cè)量誤差最小化

合理的DS2780線路板布局降低電流測(cè)量失調(diào)誤差

合理的DS2780線路板布局降低電流測(cè)量失調(diào)誤差

評(píng)論