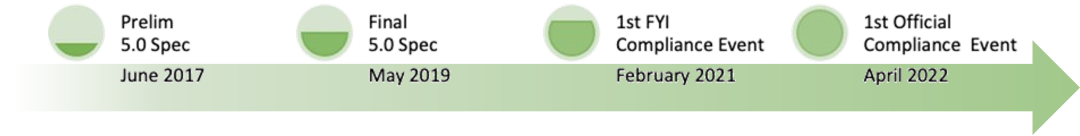

從規范草案到被 PCI-SIG 列入集成商的合規目錄需要經歷數年。初步 PCIe 5.0 規范于 2017 年 6 月公布,最終規范于 2019 年 5 月發布,第一次正式合規研討會于 2022 年 4 月舉行。如此漫長的過程說明了所開發的產品以及支持這些產品所需的生態系統非常復雜。

Cadence 一直是 PCI-SIG 的長期成員,也是 PCIe IP 的積極開發者。隨著多個產品被列入集成商的合規目錄,PCIe 5.0 也不例外。Cadence依托之前的技術專長,增強了子系統解決方案,以開發符合這些嚴格規范的 IP,同時也參與了合作性的合規計劃。

PCI-SIG 合規計劃:PCIe 5.0

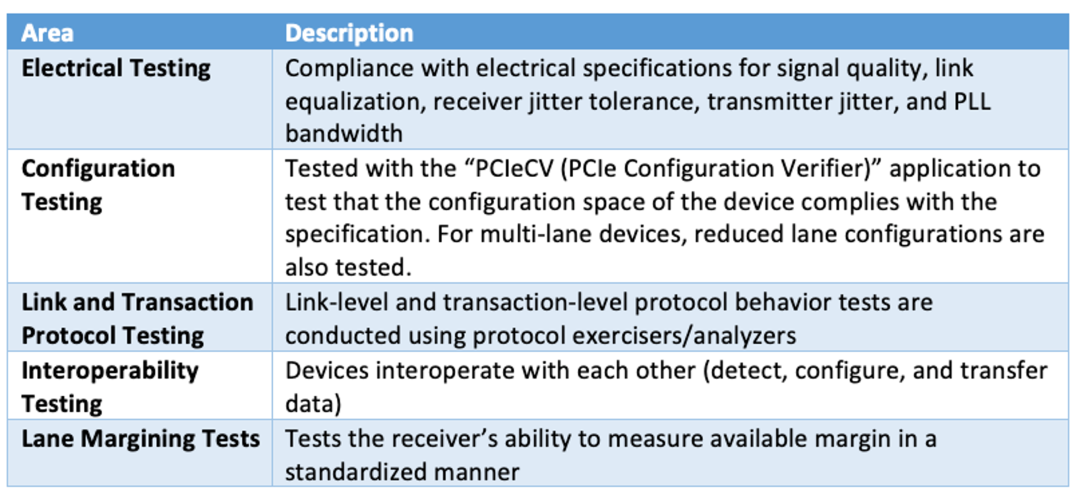

工作小組 Serial Enabling Workgroup (SEG) 負責執行 PCI-SIG 合規性計劃。該合規性計劃旨在確保經認證符合規范的設備可以實現互操作。該合規性計劃包括一套電氣和協議合規性測試(設備需要通過這些測試),還要在 PCI-SIG 組織的研討會上指定測試程序。此外,在這些研討會上,PCI-SIG 成員需要針對其他成員的產品測試自家設備的互操作性。

SEG 與各個成員公司和測試設備供應商合作,為每個版本的規范制定測試程序。該計劃涵蓋了規范的各個領域。

對于 PCIe 5.0,在 2022 年 4 月舉行的正式合規性研討會之前,PCI-SIG 在 2021 年以及之前的一年多時間里舉辦了多場“FYI(For Your Information,供參考)”研討會。這些 FYI 研討會不僅僅是一次預演,更是在完善測試程序以及確保設備和軟件可靠運行方面發揮了重要作用。這些研討會是保密的,使競爭者能夠彼此合作并改進各自的產品和標準——這是一種真正的競爭性合作,有力地推動了行業的發展。

Cadence 的方法和成功經驗

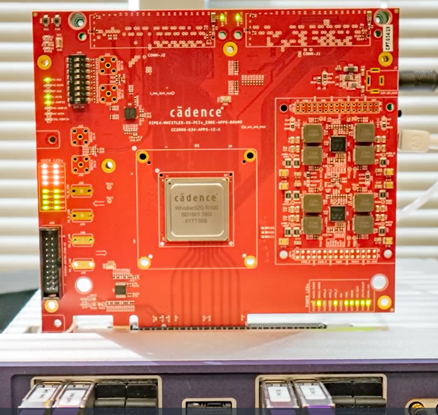

Cadence 依托之前在 3.0 和 4.0 版規范合規性方面取得的成功,對 PCIe 5.0 采取了獨特的方法。通過在硅片中構建一個 IP 子系統,Cadence可以將整個協議棧作為一個 8 通道的解決方案進行測試,其中涵蓋了許多客戶實際使用的應用。

左圖為 PCIe 5.0 子系統子卡

右圖為 PCIe 5.0 子系統示意圖

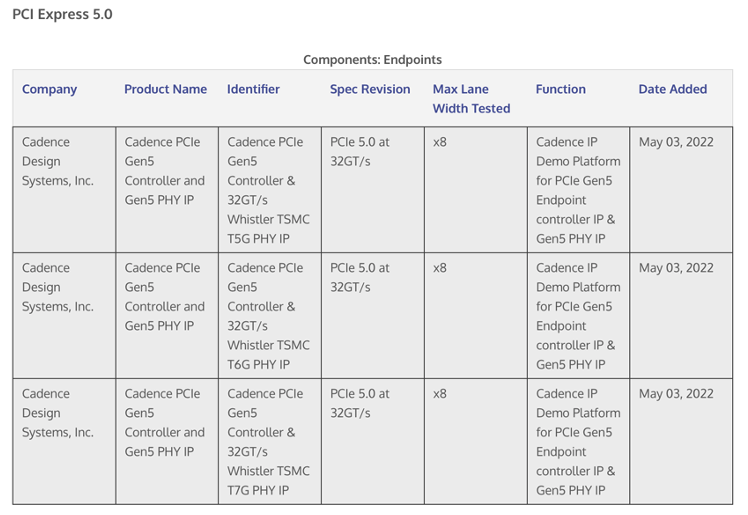

Cadence 的 PCIe 5.0 產品在整個 FYI 計劃中表現良好,并在 2022 年 4 月舉行的第一次研討會上實現了合規。由于測試點有限,Cadence 在這次會議上對終端產品進行了多個工藝節點的認證。我們的根端口配置在7月 25-28 日舉行的研討會上經過了認證,并將很快被列入集成商的目錄。

在 2022 年 4 月舉行的合規性研討會上,Cadence PCIe 5.0 接受測試

超越合規性:壓力測試和互操作性

雖然合規性測試旨在檢查產品是否符合互操作性的一系列必要要求,但在現實中,這些測試只是產品需要滿足的最低要求。

在真實的系統中,我們會需要測試各種狀況,包括鏈路錯誤、速度變化和電源狀態變化。我們的實驗室經過妥當配置,可針對這些條件進行壓力測試,涵蓋各種溫度和工藝條件,在各種商用平臺上進行數十萬次測試。除了 8 通道擴展卡,我們還構建了 U.2 規格的擴展卡,可以將其輕松插入機架安裝的系統中進行測試。通過在以上條件下的詳盡測試,我們可以胸有成竹地向 Cadence IP 解決方案的采用者保證其應用將平穩運行。

目前,PCIe 6.0 規范也已于2022年初由 PCI-SIG 發布。PCIe 6.0 具有64GT/s 的原始數據速率,通過 x16 配置,最高可達 256GB/s,并利用業界現有的 PAM4 技術。如欲了解 PCIe 6.0 的詳細內容,歡迎閱讀文章《行業洞察 I PCIe 6.0 標準與 Cadence 的實施方法》。

在設計 PCIe 6.0 時,信號完整性問題格外重要。因為PCIe 通道并不是隔離的,并且通道的走線與附近的所有導電結構都會產生電耦合。這就意味著數學模型、2D 仿真和近似值通常都太不準確,無法正確預測寄生值以滿足 PCIe 6.0 代標準的要求。

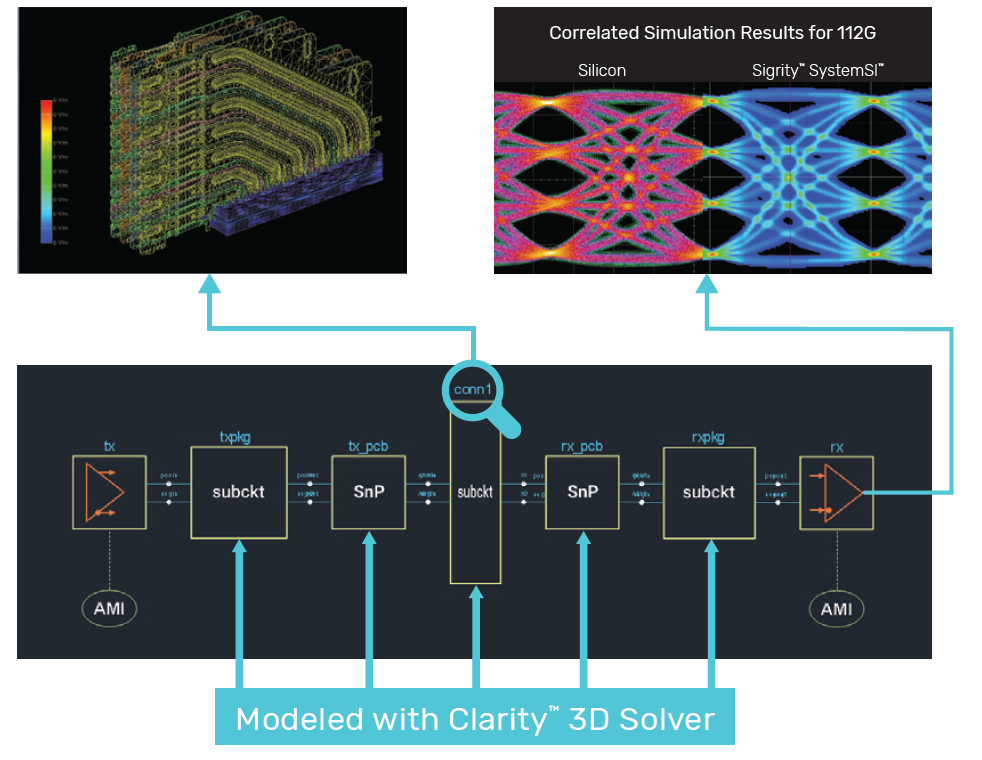

Cadence Clarity 3D Solver 使用了真正的整體的 3D 電磁場求解器,專門為適應大型 PCB 結構的仿真而構建。具有足夠高的精度和速度來捕獲小尺寸的 3D 電磁求解器甚至可以用于提供 IC 封裝和 PCB 走線的電磁仿真。與將通過不同 IC 和 PCB 寄生提取方法得到的結果級聯在一起相比,這種方法能夠更加精確和完整地展現寄生行為和通道特性。

與近似值和簡化模型相比,擁有足夠容量的精確 3D 仿真工具可以生成與 PCIe 通道特性的實驗數據更好匹配的模型。

同時,使用 Clarity 3D Solver 生成的模型與實驗室的測量結果會更為接近,并且可以直接導入到行業標準電路仿真器(例如 Cadence Sigrity SystemSI)中,以實現實際測量和仿真之間極高的相關性。這對 PCIe 的合規性和互操作性測試尤具價值,可以幫助設計在電氣測試(包括平臺和內插卡發射器和接收器特性測試)中獲得關鍵性優勢,增強設計人員首次測試即可通過的信心。

-

IP

+關注

關注

5文章

1863瀏覽量

155837 -

PCI

+關注

關注

5文章

689瀏覽量

134248

發布評論請先 登錄

MAX5954:PCI Express熱插拔控制器的卓越之選

LTC4242:PCI Express熱插拔控制器的卓越之選

PI7C9X110:PCI Express到PCI可逆橋接器的技術剖析與應用指南

Splashtop 合規體系全景解讀:ISO/IEC 27001、SOC 2、GDPR 和 CCPA 等

國產高性能ONFI IP解決方案全解析

探索DS50PCI402:PCI Express應用的理想選擇

探索DS80PCI402:PCI - Express中繼器的卓越性能與應用實踐

Sutherland與ComplyAdvantage推出AI原生“統一金融犯罪合規”解決方案,旨在打擊日益復雜的新一代金融犯罪

Amphenol PCI Express? Gen 6 卡邊緣連接器:下一代系統的高速解決方案

亞馬遜基于NVIDIA技術實現創新型制造解決方案

艾默生 SolaHD 通過 \"從地板到云端?\"解決方案和在線產品配置器推進電能質量管理

QDMA Subsystem for PCI Express v5.0產品指南

產品創新 I 構建強大的 PCI Express IP 解決方案:實現并超越合規性

產品創新 I 構建強大的 PCI Express IP 解決方案:實現并超越合規性

評論