Allegro的全稱是Cadence Allegro PCB Designer,是Cadence公司推出的一個完整的、高性能印制電路板設計套件。通過頂尖的技術,它為創建和編輯復雜、多層、高速、高密度的印制電路板設計提供了一個交互式、約束驅動的設計環境。它允許用戶在設計過程的任意階段定義、管理和驗證關鍵的高速信號,并能抓住今天最具挑戰性的設計問題。Allegro印制電路板設計提高了PCB設計效率和縮短設計周期,讓您的產品盡快進入量產。

接下來我們給大家分享一些關于Allegro的設計小技巧,本次文章介紹如何使用Allegro直接添加相對傳輸延遲的等長規則。怎么去添加相對傳輸延遲的等長規則,首先講述的是通過直接添加法去添加,直接添加法只適用于點對點的傳輸模式,中間沒有任何串阻、串容的情況,具體操作如下所示:01打開規則管理器

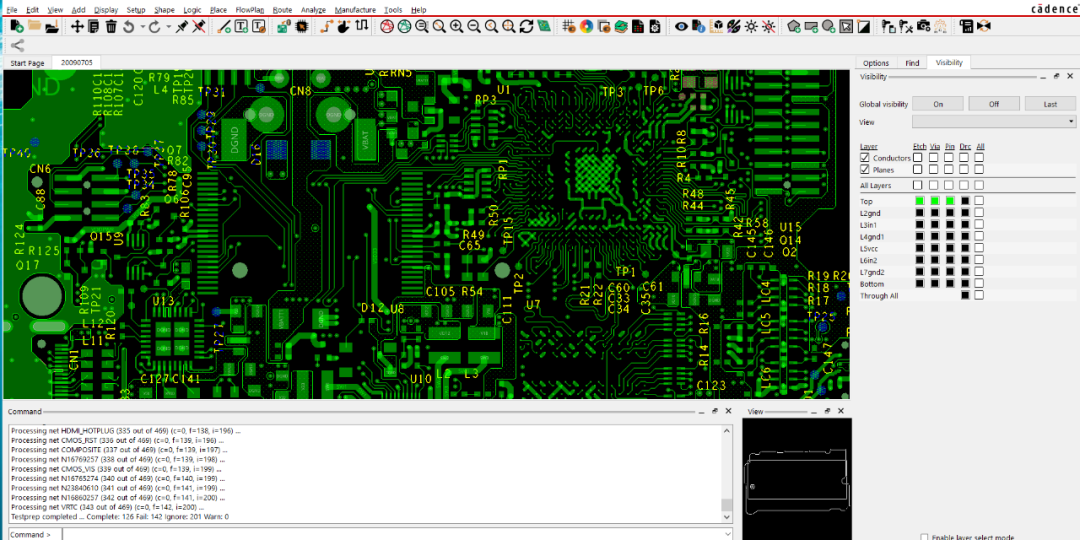

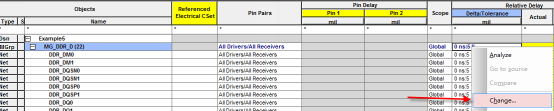

打開規則管理器,執行菜單命令Setup-Constraints,在下拉菜單中選擇Constraint Manager,如圖1所示,進入到規則管理器中;

圖1 規則管理器示意圖

02Relative Propagation Delay

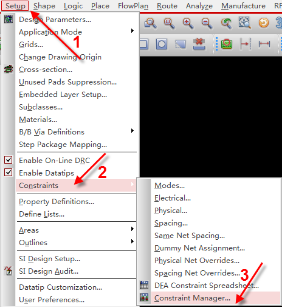

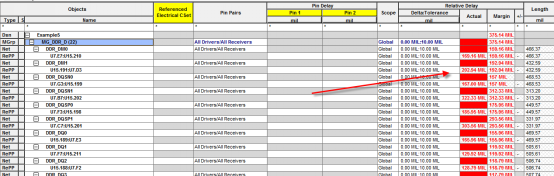

進入到規則管理器之后,在CM左側的目標欄中選擇Net,在Net中選擇相對傳輸延遲選項Relative Propagation Delay,如圖2所示;

圖2 相對傳輸延遲設置示意圖

03創建等長信號線

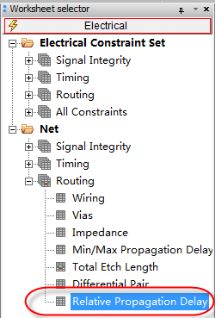

選擇需要創建等長的信號線,或者是事先將需要創建等長的信號線加好Bus,直接全部選中,點擊鼠標右鍵,執行菜單命令Create-Match Group,創建等長集合,如圖3所示;

圖3 創建等長集合示意圖

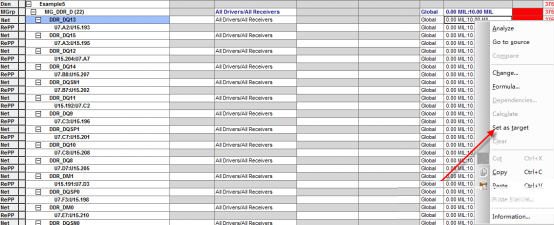

04創建等長集合

在彈出的界面中,輸入需要創建的等長集合的名稱,見名知意,如:“MG_DDR_D”,取好名稱之后,點擊按鈕,則等長的集合就創建完畢了,創建好之后,在誤差那一欄,選中最上面的根目錄,點擊鼠標右鍵,點擊Change命令,對所設置的等長集合的誤差進行修改即可,如圖4所示;

圖4 誤差設置示意圖

05添加等長信號線規則

設置好誤差之后,比如±10mil,點擊OK按鈕,則這一組需要做等長的信號線的規則就添加好了,如圖5所示;

圖5 等長列表示意圖

06設置目標線

等長添加好以后,選擇一根合適的信號線,點擊右鍵,設置為目標線,則所有的信號線就按照這個線為基準,在誤差范圍進行等長即可,如圖6所示;

圖6 設置目標線意圖

01總結

01總結

通過上面的學習讓我們看到了如何使用Allegro直接添加相對傳輸延遲的等長規則。閱讀完這篇文章的小伙伴可以自己去試一試這個功能。下期給大家分享如何使用Allegro精準定位刪除Out of data shape銅皮框。

-

allegro

+關注

關注

42文章

767瀏覽量

150143

發布評論請先 登錄

Allegro宣布推出全新霍爾效應電流傳感器ACS37017

Allegro ACS37100磁性電流傳感器榮獲EDN 2025年度產品獎

Allegro亮相第五屆汽車AI智能底盤大會

凡億Allegro Skill字符功能-添加中文字符

一文讀懂Allegro先進磁性開關和鎖存器

強強聯合!Allegro 與沃德爾簽署戰略合作協議,賦能汽車、工業等多元領域持續創新

Allegro 2025慕尼黑上海電子展精彩回顧

Allegro亮相2025慕尼黑上海電子展

安森美終止收購Allegro 此前安森美為什么要收購Allegro MicroSystems?

Allegro電流傳感器替代采樣電阻的解決方案

Allegro小技巧 | 如何使用Allegro直接添加相對傳輸延遲的等長規則

Allegro小技巧 | 如何使用Allegro直接添加相對傳輸延遲的等長規則

評論