編者按

“中國科學院大學集成電路學院是國家首批支持建設的示范性微電子學院。為了提高學生對先進光刻技術的理解,本學期集成電路學院開設了《集成電路先進光刻技術與版圖設計優化》研討課。在授課過程中,除教師系統地講授外,學生還就感興趣的課題做深入調研。師生共同討論調研報告,實現教學互動。調研的內容涉及光刻工藝、光刻成像理論、SMO、OPC和DTCO技術。

考慮到這些內容也是目前業界關注的實用技術,征得教師和學生的同意,本公眾號將陸續展示一些學生的調研結果。這些報告還很初步,甚至有少許謬誤之處,請業界專家批評指正。

以下為報告PPT:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

集成電路

+關注

關注

5452文章

12572瀏覽量

374532 -

光刻技術

+關注

關注

1文章

151瀏覽量

16529 -

GAA

+關注

關注

2文章

38瀏覽量

7959

原文標題:【Study】GAA器件結構工藝和挑戰

文章出處:【微信號:光刻人的世界,微信公眾號:光刻人的世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

AI如何重塑模擬和數字芯片工藝節點遷移

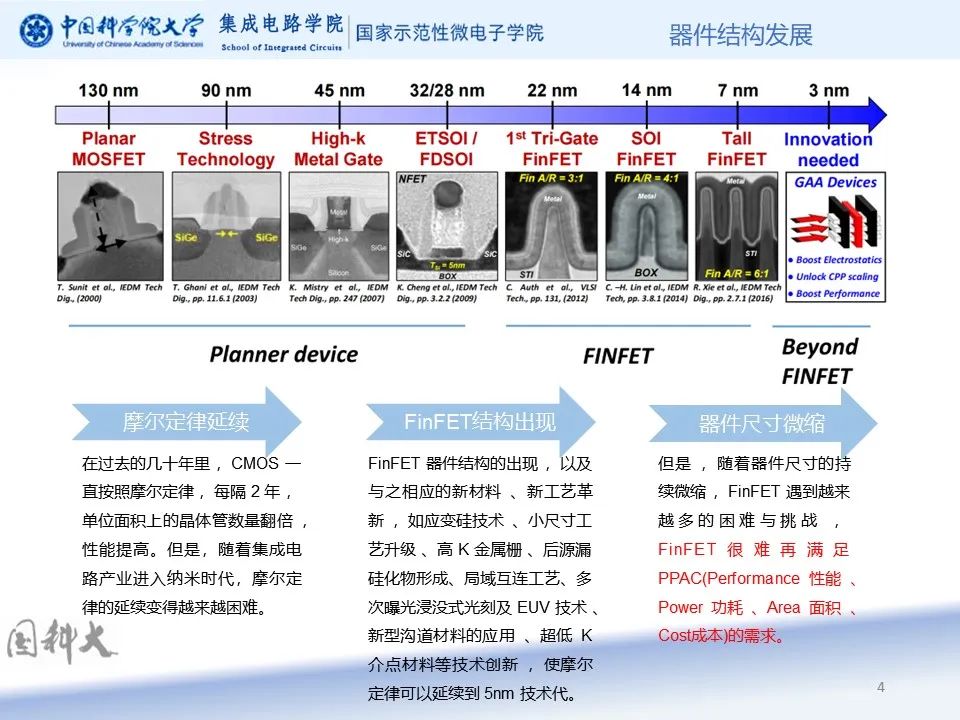

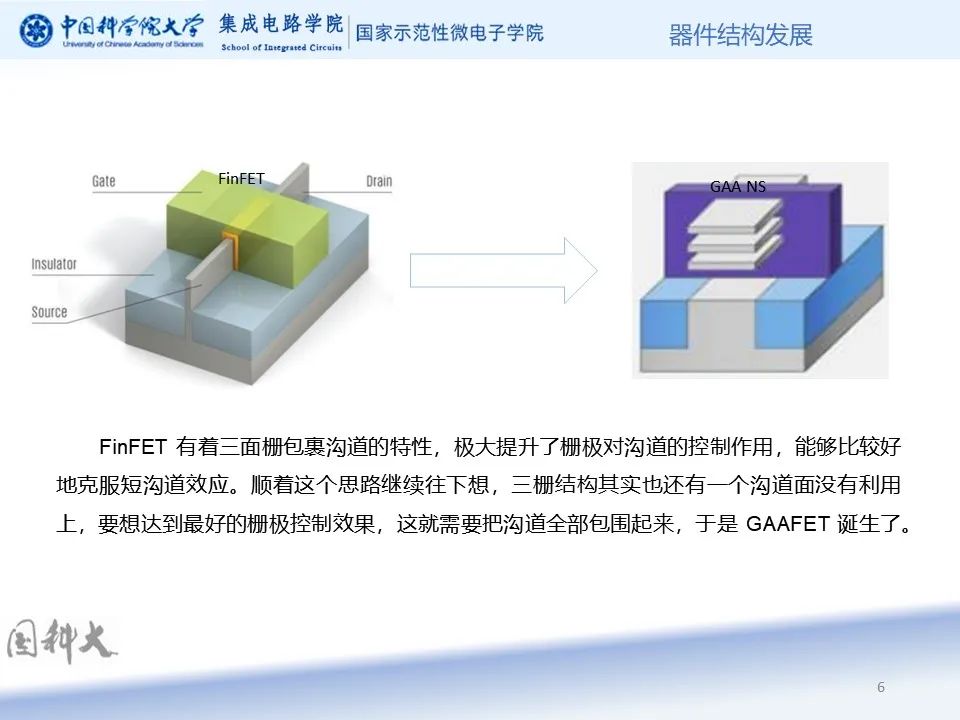

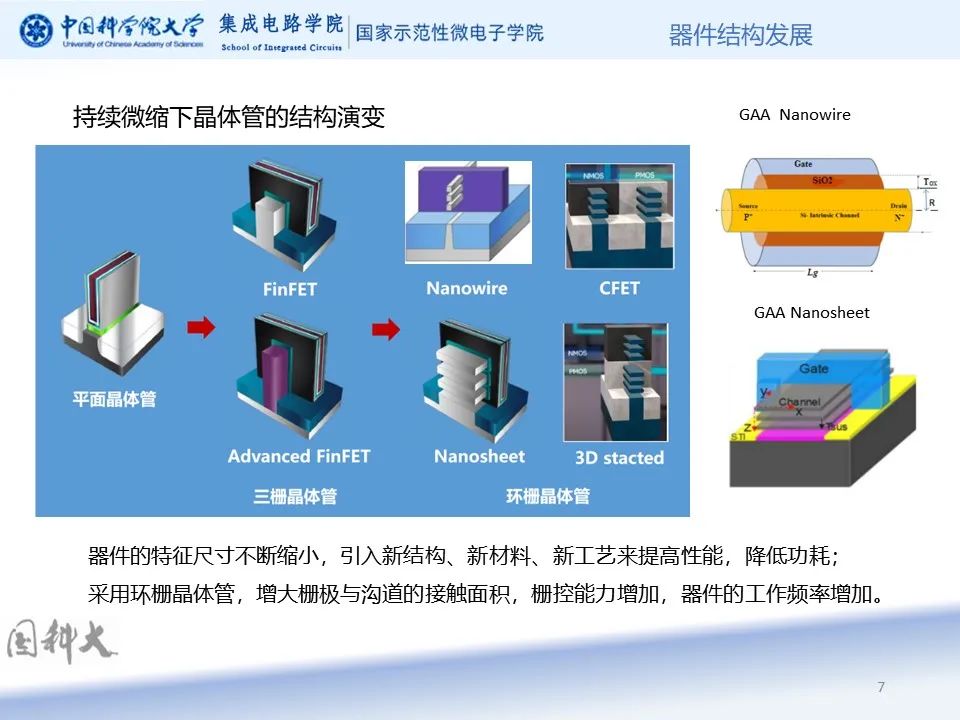

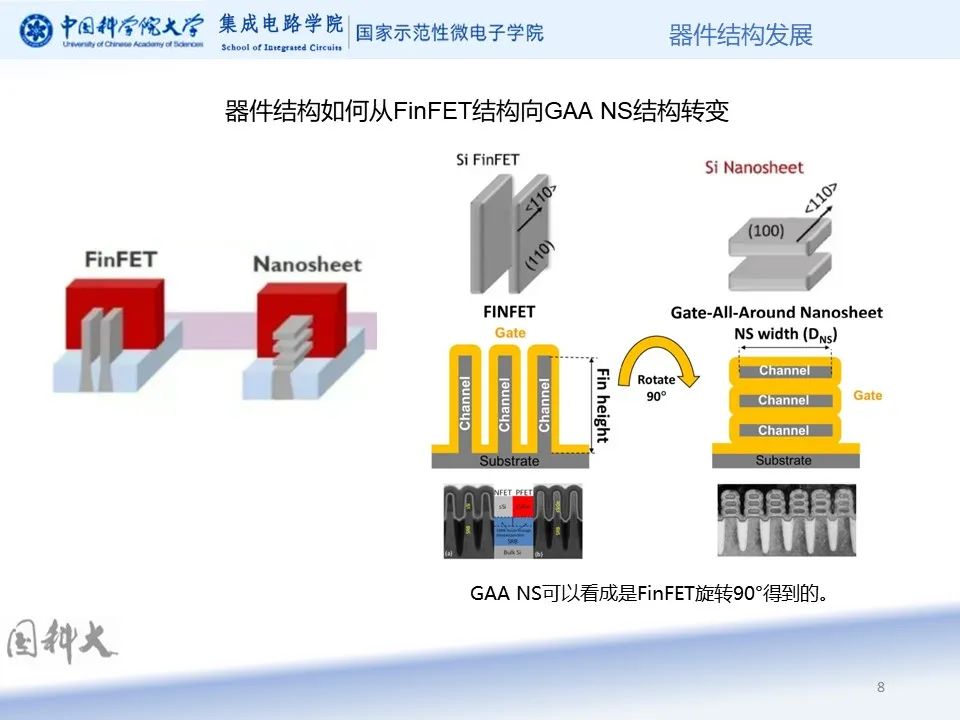

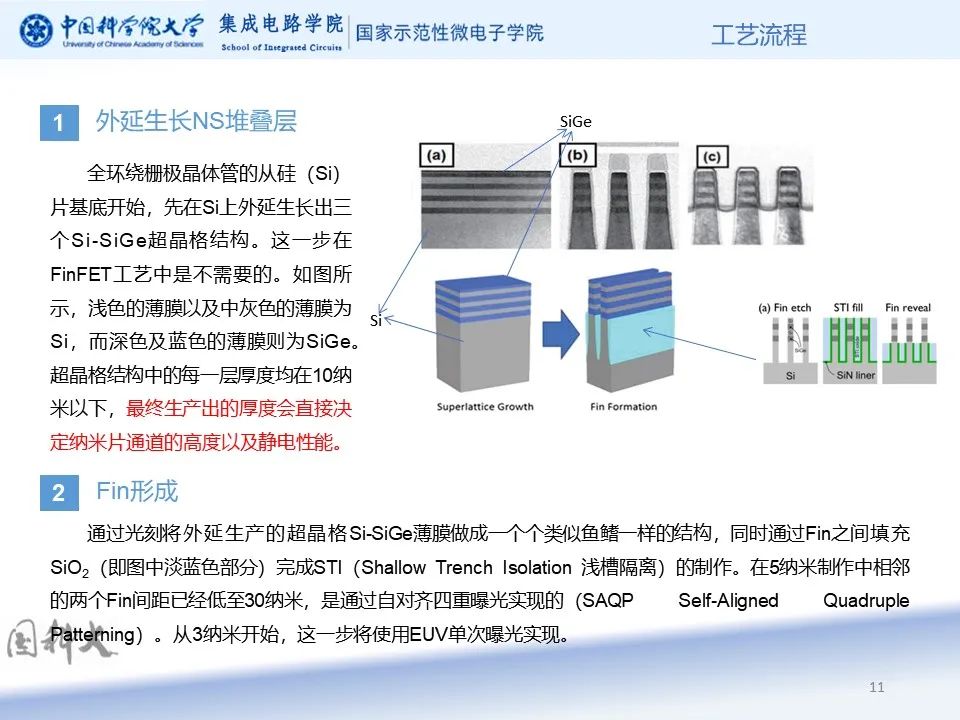

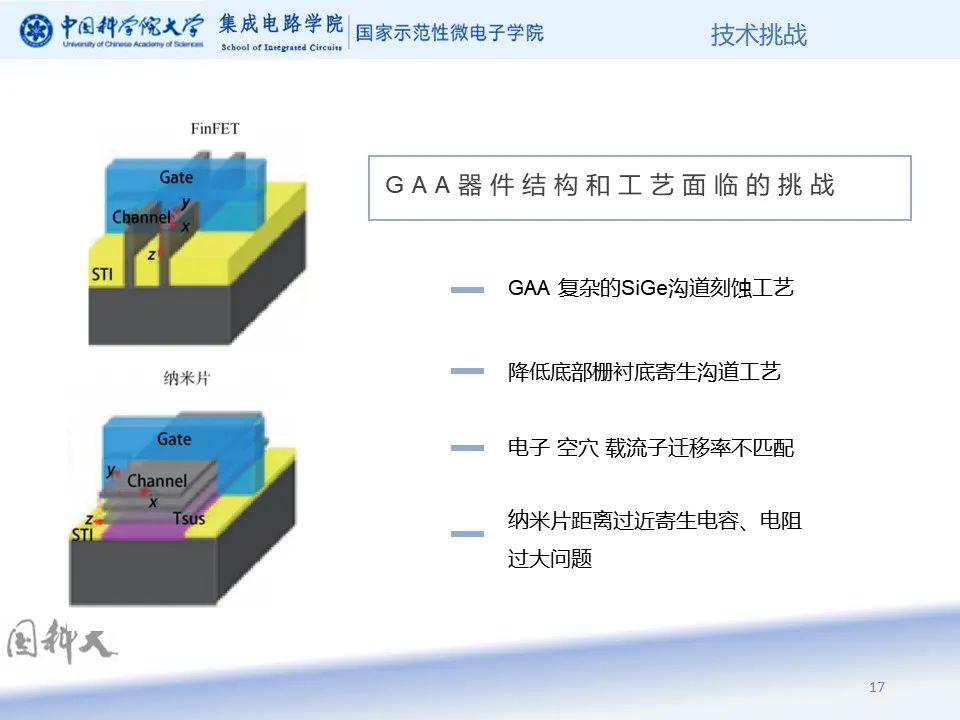

工藝技術的持續演進,深刻塑造了當今的半導體產業。從早期的平面晶體管到鰭式場效應晶體管(FinFET),再到最新的全環繞柵極(GAA)架構,每一代新工藝節點都為顯著改善功耗、性能和芯片面積(PPA)創造了機會。

半導體器件清洗工藝要求

半導體器件清洗工藝是確保芯片制造良率和可靠性的關鍵基礎,其核心在于通過精確控制的物理化學過程去除各類污染物,同時避免對材料造成損傷。以下是該工藝的主要技術要點及實現路徑的詳細闡述:污染物分類與對應

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

的解決漏電流問題,在源極和漏極之間的電流路徑的溝道中控制平面的數量被增加到3個,以抑制漏電流。

GAA:結構中有4個控制平面,與FinFET相比,漏電流問題進一步減小,在先進的邏輯半導體中實現高效率

發表于 09-15 14:50

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

。那該如何延續摩爾神話呢?

工藝創新將是其途徑之一,芯片中的晶體管結構正沿著摩爾定律指出的方向一代代演進,本段加速半導體的微型化和進一步集成,以滿足AI技術及高性能計算飛速發展的需求。

CMOS工藝從

發表于 09-06 10:37

濕法蝕刻工藝與顯示檢測技術的協同創新

在顯示技術飛速迭代的今天,微型LED、柔性屏、透明顯示等新型器件對制造工藝提出了前所未有的挑戰:更精密的結構、更低的損傷率、更高的量產一致性。作為研發顯示行業精密檢測設備的的企業,美能

下一代高速芯片晶體管解制造問題解決了!

在半導體工藝演進到2nm,1nm甚至0.7nm等節點以后,晶體管結構該如何演進?2017年,imec推出了叉片晶體管(forksheet),作為環柵(GAA)晶體管的自然延伸。不過,產業對其可制造

發表于 06-20 10:40

國內外電機結構 工藝對比分析

純分享帖,需要者可點擊附件免費獲取完整資料~~~*附件:國內外電機結構 工藝對比分析.pdf【免責聲明】本文系網絡轉載,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請第一時間告知,刪除內容!

發表于 05-29 14:06

CSD船用變壓器:結構強度不夠?創新工藝來解決

船舶和海洋平臺面臨著復雜的工況,對變壓器的結構強度要求極高。CSD/CDD船用變壓器的結構強度是否足夠應對這些挑戰呢?答案是肯定的!這款變壓器采用ANSYS仿真技術進行多物理場耦合仿真,優化繞組

LPCVD方法在多晶硅制備中的優勢與挑戰

本文圍繞單晶硅、多晶硅與非晶硅三種形態的結構特征、沉積技術及其工藝參數展開介紹,重點解析LPCVD方法在多晶硅制備中的優勢與挑戰,并結合不同工藝條件對材料性能的影響,幫助讀者深入理解硅

TRCX應用:顯示面板工藝裕量分析

制造顯示面板的主要挑戰之一是研究由工藝余量引起的主要因素,如CD余量,掩膜錯位和厚度變化。TRCX提供批量模擬和綜合結果,包括分布式計算環境中的寄生電容分析,以改善顯示器的電光特性并最大限度地減少缺陷。

(a)參照物

(b)膜層未對準

發表于 03-06 08:53

GAA器件結構工藝和挑戰

GAA器件結構工藝和挑戰

評論