當下集成電路芯片測試座的制作方法有很多,但您需要一種高效、穩定、易操作的方法。

集成電路芯片測試座是關鍵的電子產品測試工具,它可以幫助生產廠家快速有效地進行電路芯片測試,從而保證了電子產品的質量和生產效率。為此,我們提供了一種高效、穩定、易操作的集成電路芯片測試座制作方法。

首先,我們需要準備一些基礎材料。這些材料包括硅膠、銅箔、鋼板、熱塑性塑料等。硅膠用于制作測試座的墊片,銅箔則用來做測試座的引腳,鋼板和熱塑性塑料則用來打造測試座的整體結構。

其次,我們需要根據設計圖紙進行加工制作。首先,把銅箔切割成適當的形狀,然后將其焊接在測試座的墊片上。接著,將制作好的曲線模板放置在熱塑性塑料上,用熱水或者其他加熱方式使其變軟,然后將其壓縮成所需的形狀。最后,將硅膠和制作好的引腳和結構組合在一起,形成一個完整的測試座。

最后,我們需要進行測試座的性能測試。這包括電流、電壓、溫度等參數的測試,以確保測試座滿足設計要求。如有必要,還可以對測試座進行改進優化,以提高其性能和可靠性。

以上是一種集成電路芯片測試座的制作方法,希望對您有所幫助。

審核編輯黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片

+關注

關注

463文章

54010瀏覽量

466138 -

集成電路

+關注

關注

5452文章

12572瀏覽量

374568

發布評論請先 登錄

相關推薦

熱點推薦

指令集測試的一種糾錯方法

本文描述在進行指令集測試的一種糾錯方法

1.打開測試指令集對應的dump文件

dump文件是指由匯編文件進行反匯編之后,可以供人閱讀指令的反匯編文件。其包含了每

發表于 10-24 14:04

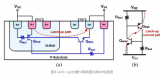

CMOS集成電路中閂鎖效應的產生與防護

閂鎖效應(Latch-up)是CMOS集成電路中一種危險的寄生效應,可能導致芯片瞬間失效甚至永久燒毀。它的本質是由芯片內部的寄生PNP和NPN雙極型晶體管(BJT)相互作用,形成類似可

集成電路測試中的關鍵角色:MEDER超微型繼電器

在當今快速發展的科技時代,芯片設計人員正不斷突破極限,開發出體積更小、運行速度更快且擁有更多門電路的新型集成電路。這些芯片上的成百上千萬個門電路

發表于 04-23 16:50

電機控制專用集成電路PDF版

本書共13章。第1章緒論,介紹國內外電機控制專用集成電路發展情況,電機控制和運動控制、智能功率集成電路概況,典型閉環控制系統可以集成的部分和要求。第2~7章,分別敘述直流電動機、無刷直流電動機、步進

發表于 04-22 17:02

一種分段氣隙的CLLC變換器平面變壓器設計

一種路徑,采用磁集成方法,對1MHz雙向CLLC變換器的變壓器進行研究、設計與測試,通過優化PCB繞線方法、進行仿真優化,提出了一種分段氣隙

發表于 03-27 13:57

一種永磁電機用轉子組件制作方法

一種永磁電機所使用的轉子組件,是由磁鋼與芯軸組裝而成,產品工作轉速80 000 r /mi n,磁鋼相對于芯軸的同軸度要小于O.015 mm。現有的裝配方法是:先在芯軸兩端面制作中心孔,然后直接

發表于 03-25 15:20

一種集成電路芯片測試座的制作方法

一種集成電路芯片測試座的制作方法

評論