大俠好,歡迎來到FPGA技術江湖。本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有系統性學習的機會。

系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。后續會陸續更新 Xilinx 的 Vivado、ISE 及相關操作軟件的開發的相關內容,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用,這種快樂試試你就會懂的。話不多說,上貨。

數字電路中的組合邏輯

根據邏輯功能的不同特點,可以將數字電路分為兩大類,一類稱為組合邏輯電路(簡稱組合電路),另一類稱為時序邏輯電路(簡稱時序電路)。

在組合邏輯電路中,任何時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。這就是組合邏輯電路在邏輯功能上的共同特點。在上一節中,設計的三人表決器就是組合邏輯電路,輸出與輸入一一對應,和其他無關,輸入發生改變,輸出立刻跟著改變。

組合邏輯的設計方法在邏輯代數基礎中有一定的簡單的敘述。

根據現有的資源做出合理的假設(通過為1、還是為0,不同的硬件可能會是不同的結構)。

根據設計要求和假設,列出真值表。

根據真值表得出表達式,并化簡(公式化,卡諾圖)。有時需要化簡為與非的形式或者其他形式。

根據化簡后的布爾表達式做出電路結構,并且驗證。

如果最后結果出現錯誤,上述所有步驟都要檢查,如果上述步驟都沒有問題,可以考慮電路結構中的連接問題或者器件的損壞。

下面利用一個三人表決器的電路設計來說明一些問題。此電路有三個輸入(A、B、C),一個輸出(Y),只有當兩個及兩個以上輸入贊成時,Y輸出贊成。

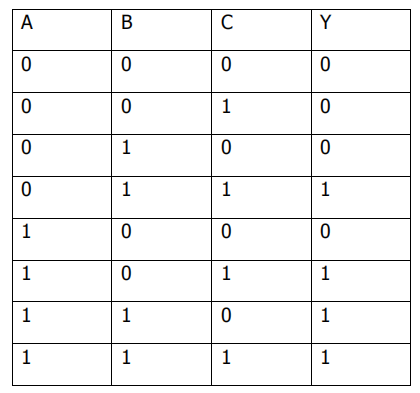

設贊成為1,不贊成為0。根據設計要求得出如下真值表:

圖1 :三人表決器真值表

根據真值表中Y為1的項列出來,對應的A、B、C為1,則留下變量,為0,則留下反變量。

Y = A'BC+AB’C+ABC’+ABC;

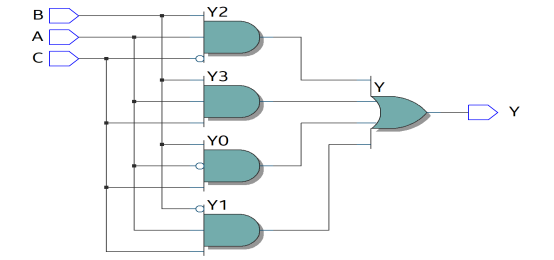

根據上述布爾表達式,我們得出邏輯電路圖:

圖2 :三人表決器的邏輯電路圖

如果所有的邏輯都按照這種寫法的話,那么很多的邏輯就會變的很復雜,并且會浪費很多的資源。我們考慮一下,電路既然是按照布爾表達式做出來的,那么布爾表達式能不能化簡一下呢?

Y = A'BC+AB’C+ABC’+ABC;

= A'BC+ ABC +AB’C+ ABC+ ABC’+ABC;

= BC(A' + A) + AC(B+B') + AB(C+C')

= BC+AC+AB

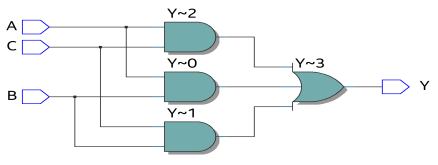

上述布爾表達式所對應的邏輯電路圖如下:

圖3 :化簡后的布爾表達式所對應的電路圖

思考 :半加器、全加器、多路選擇器、乘法器、除法器等常用組合邏輯電路的設計與實現?

在設計組合邏輯時,分析和設計都是在輸入、輸出處于穩定的邏輯電平下進行的。為了保證系統工作的可靠性,有必要再觀察一下當輸入信號邏輯電平發生變化的瞬間電路的工作情況。

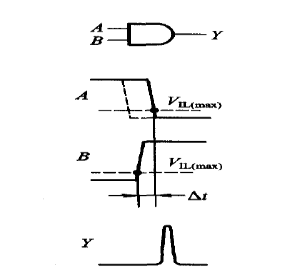

在圖1-28所示的與門電路中,穩態下無論A=1、B=0還是A=0、B=1,輸出都應該是Y=0;但是輸入信號A從1變為0時,如果B從0變為1,由于某些原因(布線的寬度、厚度、溫度等),B先從0變為1了,這樣在極短的時間內出現了A和B都是1的情況,與門電路就會輸出一個極窄的Y=1的尖峰脈沖,或稱為電壓毛刺。這個尖峰脈沖不符合門電路穩態下的邏輯功能,因而它是系統內部的一種噪聲。

圖4 :與門由于競爭而產生的尖峰脈沖

將門電路兩個輸入信號同時向相反的邏輯電平跳變(一個從1變為0,另一個從0變為1)的現象稱為競爭。

在有競爭時,不一定都會產生尖峰脈沖。例:在上述的與門中,如果A先于B發生了改變,此時就不會產生尖峰脈沖。

思考:可以嘗試分析一下或門,分析或門是否有可能會產生尖峰脈沖?

與門和或門在競爭時,都有可能產生尖峰脈沖。與門和或門是復雜數字邏輯電路中的兩個基本門電路,A、B經過不同的傳輸途徑達到,那么在設計時往往難于準確知道A、B到達次序的先后,以及它們在上升時間和下降時間上的細微差異。因此,我們只能說只要存在競爭現象,輸出就有可能出現違背穩態下邏輯關系的尖峰脈沖。

由于競爭而在電路輸出端可能產生尖峰脈沖的現象稱為競爭-冒險。

如果后續電路是一個對尖峰脈沖敏感的電路,那么這種尖峰脈沖將可能使后續電路發生誤動作。

思考:如果存在競爭冒險現象的話,應該怎么避免?

可以在輸出端接入濾波電容;由于競爭-冒險而產生的尖峰脈沖一般都很窄,所以在輸出端并接一個很小的濾波電容就足以把尖峰脈沖的幅度削弱至門電路的閾值電壓一下。這種方法簡單易行,而缺點是增加了輸出電壓波形的上升時間和下降時間,使波形變壞。

引入選通脈沖;由于電路的延遲產生的尖峰脈沖是極窄的,如果在輸入(輸出)信號穩定后,我們再去選取結果作為輸出,此時的結果就是正確的。那么此時的選通脈沖就必須要要在穩定后再能出現,否則也無濟于事。

修改邏輯設計;此方法的局限性比較大,不再做過多介紹。

通過對組合邏輯的認識,感覺自己已經可以設計任何電路。只要按照標準的設計流程,我們都可以很快的做出電路。

思考 :目前需設計一個自動售貨機,販賣售價為三元的飲料,要求每次只能投入一個一元的硬幣。可想而知,我們投入第一個硬幣沒有反應;投入第二個硬幣沒有反應;當我們投入第三個硬幣時,售貨機會給我們一瓶飲料。如果內部是組合邏輯的話,三次投硬幣的輸入并沒有任何改變,但是產生了不同的結果,顯然內部結構不是單純的組合邏輯。內部的功能有一定的記憶性功能,能夠清楚的記得之前我們投入的硬幣的數量。此時我們應該如何去設計電路。

組合邏輯電路中,任一時刻的輸出信號僅取決于當時的輸入信號。

更多熱點文章閱讀

-

電子技術

+關注

關注

19文章

930瀏覽量

60036 -

電子發燒友論壇

+關注

關注

5文章

198瀏覽量

1665

原文標題:【教程分享】FPGA零基礎學習:數字電路中的組合邏輯

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發燒友論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

掌握數字設計基礎:邁向芯片設計的第一步

高速數字電路設計與安裝技巧

零基礎學習LuatOS編程:快速上手開發實戰教程!

【教程分享】FPGA零基礎學習:數字電路中的組合邏輯

【教程分享】FPGA零基礎學習:數字電路中的組合邏輯

評論