利用CMOS設計電路需先自行學習NMOS和PMOS的基本原理。

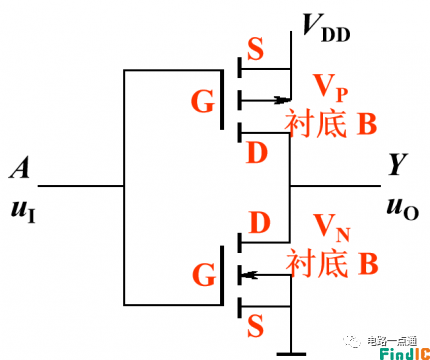

1、非電路設計

如圖所示,非電路由一個PMOS和一個NMOS組成。 當uI=0,PMOS管導通,NMOS管關斷,u0約等于VDD,為高電平; 當uI=VDD,PMOS管關斷,NMOS管導通,u0約等于0,為低電平;

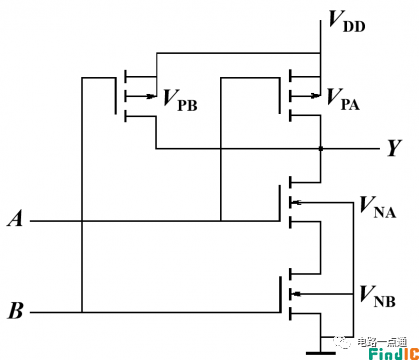

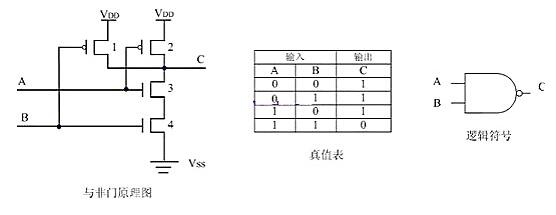

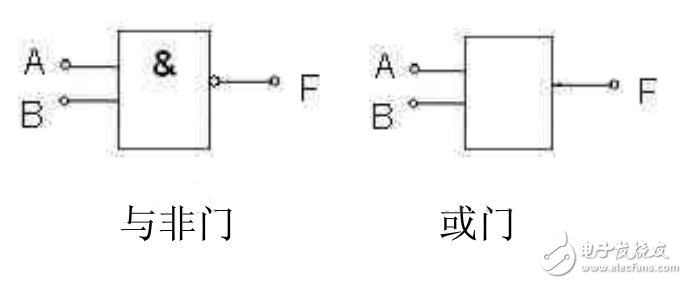

2、與非門設計

如圖所示,與非門設計包含兩個PMOS和兩個NMOS。 兩個PMOS并聯,實現A、B兩個任何一個為0,都能導通,使Y輸出高電平。 兩個NMOS串聯,實現A、B兩個同時為VDD,才能導通,使Y輸出低電平。 下表中1代表VDD高電平,0代表低電平

| A | B | Y |

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 1 |

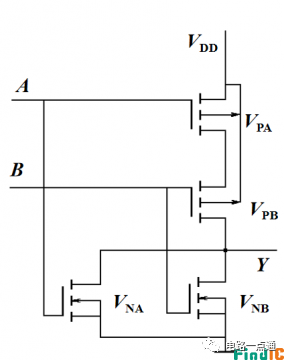

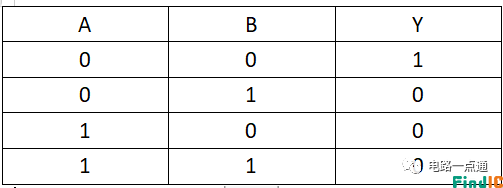

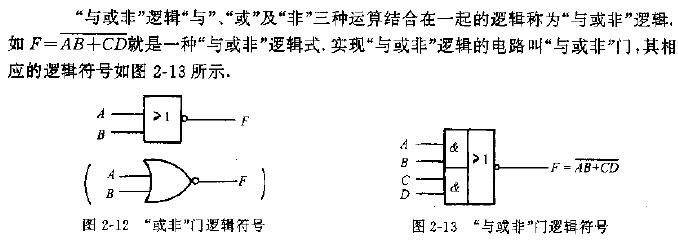

3、或非門

如圖所示,或非門設計包含兩個PMOS和兩個NMOS。 兩個PMOS串聯聯,實現A、B兩個同時為0,才能導通,使Y輸出高電平。 兩個NMOS串聯,實現A、B兩個任何一個為VDD,就能導通,使Y輸出低電平。 下表中1代表VDD高電平,0代表低電平

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

CMOS

+關注

關注

58文章

6217瀏覽量

242841 -

NMOS

+關注

關注

3文章

401瀏覽量

36829 -

非門

+關注

關注

1文章

34瀏覽量

34547 -

PMOS

+關注

關注

4文章

271瀏覽量

31609 -

與非門

+關注

關注

1文章

141瀏覽量

13429

原文標題:基于CMOS的非門、與非門、或非門設計

文章出處:【微信號:電路一點通,微信公眾號:電路一點通】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

或非門芯片

或非門芯片型號有74260 TTL 5輸入端雙或非門、74266 TTL 2輸入端四異或非門、7427 TTL 3輸入端三或非門、7402 TTL 2輸入端四

發表于 11-09 23:04

?4.9w次閱讀

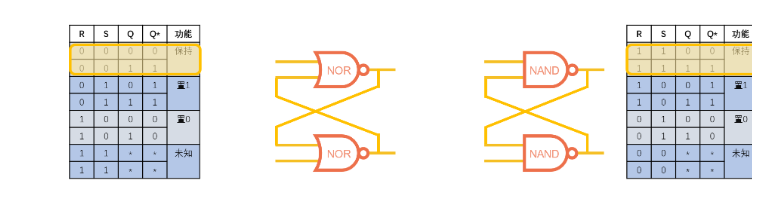

基本rs觸發器與非門和或非門的區別

基本的RS觸發器是一種使用與非門和或非門構成的存儲器元件,它可以存儲一個比特的信息并在觸發信號的控制下改變狀態。與非門和或非門則是用于邏輯運算的基本門電路,它們執行邏輯“與”和“或”運

為什么與非門觸發器輸入信號要非

觸發器,與非門的輸入為什么是R非S非,而或非門是RS。我百度到的說法是,與非門是低電平觸發,或非門是高電平觸發,也就是要使Q=1,與非門里S

發表于 01-28 20:39

【數字電路】關于邏輯或非門系統特性分析教程

使用單獨的NOR門。常用的數字邏輯或非門IC包括:TTL邏輯或非門74LS02四路2輸入74LS27三路3輸入74LS260雙4輸入CMOS邏輯或非門CD4001四路2輸入CD4025

發表于 01-22 09:00

與非門實現非門功能方法介紹

本文主要闡述了關于如何用與非門實現非門功能介紹,以及用二輸入與非門實現非門功能方法,為了便于理解,在講解之前我們先來了解一下與非門及

MOS與非門或非門構成原理

與非門(英語:NANDgate)是數字邏輯中實現邏輯與非的邏輯門,功能見左側真值表。若當輸入均為高電平(1),則輸出為低電平(0);若輸入中至少有一個為低電平(0),則輸出為高電平(1)。與非門是一種通用的邏輯門,因為任何布爾函數都能用

發表于 06-25 14:21

?2.9w次閱讀

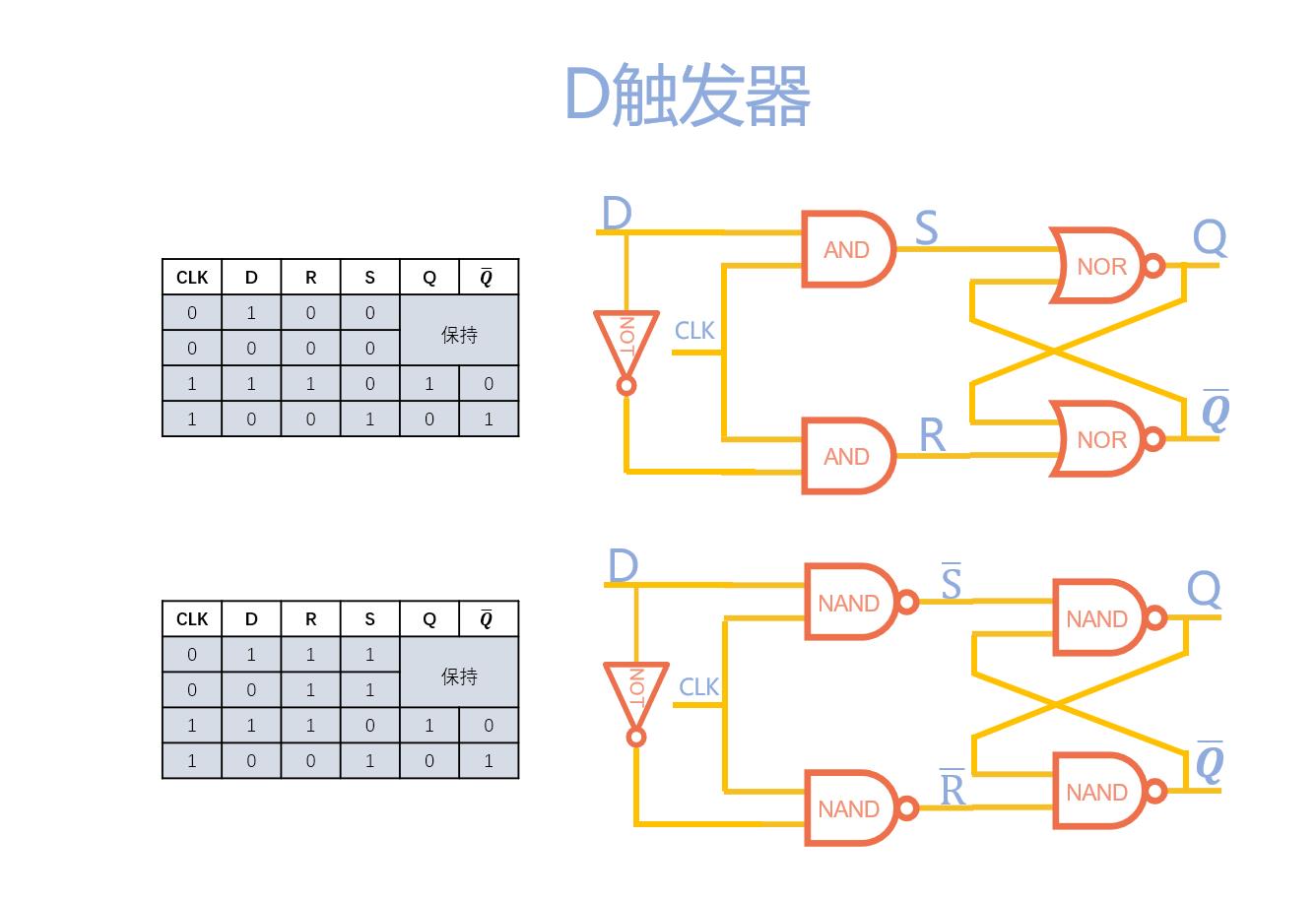

使用或非門和與非門實現觸發器

大家好,上次我們研究了D觸發器,今天我們繼續研究。在開始之前,先來做一點刪減,之前我們討論了用或非門或者與非門實現觸發器的方法,在功能上兩種實現方法完全相同,在輸入輸出和實現上略微有些差異。

TTL與非門的電壓傳輸特性 TTL與非門的靜態輸入與輸出特性

TTL與非門的電壓傳輸特性 TTL與非門的靜態輸入與輸出特性 TTL與非門的動態特性? TTL與非門是一種基本的邏輯門電路,用于將兩個輸入信號進行邏輯與運算,并輸出結果。TTL(雙晶體

cmos或非門電路與ttl或非門電路的邏輯功能

本文就CMOS或非門電路和TTL或非門電路的邏輯功能進行了詳細講解。首先介紹了CMOS和TTL兩種電路的基本原理和實現方式。然后分別從輸入特性、輸出特性和功耗三個方面,深入比較了

基于CMOS的非門、與非門、或非門設計

基于CMOS的非門、與非門、或非門設計

評論